OLeh IVAN WAHYUMAN A2.1300162 TEKNIK INFORMATIKA IE

advertisement

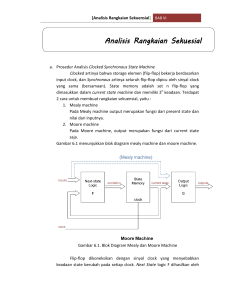

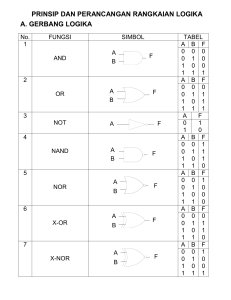

Tugas Mata Kuliah Pengantar Sistem Digital Pengertian Flip-Flop Atau juga bisa seperti berikut Flip-flop adalah rangkaian utama dalam logika sekuensial. Counter, register serta rangkaian sekuensial lain disusun dengan menggunakan flip-flop sebagai komponen utama. Flip-flop adalah rangkaian yang mempunyai fungsi pengingat (memory). Artinya rangkaian ini mampu melakukan proses penyimpanan data sesuai dengan kombinasi masukan yang diberikan kepadanya. Data yang tersimpan itu dapat dikeluarkan sesuai dengan kombinasi masukan yang diberikan. Berikut Rangkaian Flip-Flop Tabel Kebenaran Berikut macam-macam Flip-Flop yaitu : A. Flip-flop R-S SR Flip-Flop yaitu rangkaian Flip-Flop yang mempunyai 2 jalan keluar Q dan Q (atasnya digaris). Simbol-simbol yang ada pada jalan keluar selalu berlawanan satu dengan yang lain. RS-FF adalah flip-flop dasar yang memiliki dua masukan yaitu R (Reset) dan S (Set). Bila S diberi logika 1 dan R diberi logika 0, maka output Q akan berada pada logika 0 dan Q not pada logika 1. Bila R diberi logika 1 dan S diberi logika 0 maka keadaan output akan berubah menjadi Q berada pada logik 1 dan Q not pada logika 0. Sifat paling penting dari Flip-Flop adalah bahwa sistem ini dapat menempati salah satu dari dua keadaan stabil yaitu stabil I diperoleh saat Q =1 dan Q not = 0, stabil ke II diperoleh saat Q=0 dan Q not = 1. Tabel Kebenaran dan Rangkaian Flip-flop R-S B. D Flip-flop D Flip-flop merupakan salah satu jenis flipflop yang dibangun dengan menggunakan flipflop S-R. Perbedaannya dengan flip-flop S-R terletak pada inputan R, pada D Flip-flop inputan R terlebi dahulu diberi gerbang NOT, maka setiap input yang diumpankan ke D akan memberikan keadaan yang berbeda pada input S-R, dengan demikian hanya akan terdapat dua keadaan S dan R yairu S=0 dan R=1 atau S=1 dan R=0, jadi dapat disi. Rangkaian D Flip-flop Tabel Kebenaran D Flip-Flop C. RST Flip-Flop R-S flip-flop terdetak merupakan bentuk Masukan R dan S pada rangkaian R-S flip-flop dapat di sinkronisasi dengan menambahkan masukan klok (detak) pada rangkaian. Keluaran Q pada R-S flip-flop tidak dapat segera merespon masukan S dan R sebelum ada masukan klok. Respon keluaran R-S flip-flop dari masukanmasukannya. Rangkaian RST Flip-Flop Tabel Kebenaran RST Flip-Flop D. Clock Flip-Flop CRS Flip-flop adalah clocked RS-FF yang dilengkapi dengan sebuah terminal pulsa clock. Pulsa clock ini berfungsi mengatur keadaan Set dan Reset. Bila pulsa clock berlogik 0, maka perubahan logik pada input R dan S tidak akan mengakibatkan perubahan pada output Q dan Qnot. Akan tetapi apabila pulsa clock berlogik 1, maka perubahan pada input R dan S dapat mengakibatkan perubahan pada output Q dan Q not. Rangkaian Clock Flip-Flop Tabel Kebenaran Clock Flip-Flop E. T Flip-flop T Flip-flop merupakan rangkaian flip-flop yang dibangun dengan menggunakan flip-flop JK yang kedua inputnya dihubungkan menjadi satu maka akan diperoleh flip-flop yang memiliki watak membalik output sebelumnya jika inputannya tinggi dan outputnya akan tetap jika inputnya rendah. Rangkaian T Flip-flop dan Tabel Kebenaran F. JK flip-flop JK flip-flop sering disebut dengan JK FF induk hamba atau Master Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF dan Slave FF. Master Slave JK FF ini memiliki 3 buah terminal input yaitu J, K dan Clock. Sedangkan IC yang dipakai untuk menyusun JK FF adalah tipe 7473 yang mempunyai 2 buah JK flip-flop dimana lay outnya dapat dilihat pada Vodemaccum IC (Data bookc IC). Kelebihan JK FF terhadap FF sebelumnya yaitu JK FF tidak mempunyai kondisi terlarang artinya berapapun input yang diberikan asal ada clock maka akan terjadi perubahan pada output. Sering disebut dengan JK FF induk hamba atau Master Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF dan Slave FF. Master Slave JK FF ini memiliki 3 buah terminal input yaitu J, K dan Clock. Sedangkan IC yang dipakai untuk menyusun JK FF adalah tipe 7473 yang mempunyai 2 buah JK flip-flop dimana lay outnya dapat dilihat pada Vodemaccum IC (Data bookc IC). Kelebihan JK FF terhadap FF sebelumnya yaitu JK FF tidak mempunyai kondisi terlarang artinya berapapun input yang diberikan asal ada clock maka akan terjadi perubahan pada output. Rangkaian JK flip-flop Tabel Kebenaran JK flip-flop TERIMA KASIH Ivan Wahyuman TI I E

![SISDIG tubes[1]](http://s1.studylibid.com/store/data/004540342_1-5fe74bed059bcdb16f0fa14e32ceaa7c-300x300.png)