![SISDIG tubes[1]](http://s1.studylibid.com/store/data/004540342_1-5fe74bed059bcdb16f0fa14e32ceaa7c-768x994.png)

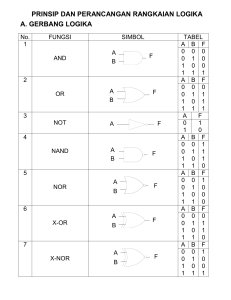

Perancangan schematic menggunakan JK-FF counter up decimal seven segment Laporan ini diajukan untuk memenuhi tugas besar Sistem Digital Disusun Oleh: 1. Albi Ahmad Nursultan (1102220166) 2. Rizqy Pratama Athaurrahman (1102220274) 3. Galih Duwiki Gilang Pamungkas (1102223065) FAKULTAS TEKNIK ELEKTRO UNIVERSITAS TELKOM BANDUNG 2023 KATA PENGANTAR Segala puji bagi Allah SWT yang Maha Pengasih lagi Maha Penyang. Shalawat serta salam tetap tercurahkan pada junjungan Nabi kita Nabi Muhammad SAW dan para sahabatnya, keluarganya, serta pengikutnya hingga akhir zaman. Laporan ini telah kami susun dengan semaksimal mungkin dan mendapatkan bantuan dari berbagai pihak hingga tersusun dengan baik. Untuk itu kami menyampaikan banyak terima kasih kepada semua pihak yang sudah membantu dalam membuat makalah ini. Kami juga memiliki kekurangan dalam membuat makalah ini, dari segi kalimat maupun tata bahasanya. Oleh karena itu kami sangat lapang dada dalam saran dan kritikan dari pembaca agar bisa menyempurnakan makalah ini. Akhir kata kami dari laporan tentang Perancangan schematic menggunakan JK-FF counter up decimal seven segmentsemoga mendapatkan manfaat atau inspirasi untuk pembaca i DAFTAR ISI KATA PENGANTAR ..................................................... Ошибка! Закладка не определена. DAFTAR ISI............................................................................................................................... ii DAFTAR TABEL ...................................................................................................................... iv DAFTAR GAMBAR .................................................................................................................. v BAB I PENDAHULUAN .............................................. Ошибка! Закладка не определена. A. Latar Belakang ....................................................... Ошибка! Закладка не определена. B. Rumusan masalah .............................................................................................................. 1 C. Tujuan .................................................................... Ошибка! Закладка не определена. D. Manfaat .................................................................. Ошибка! Закладка не определена. BAB II LANDASAN TEORI..................................................................................................... 3 A. Rangkaian Sequensial ........................................................................................................ 3 B. Macam-Macam flip-flop .................................................................................................... 3 C. Clock .................................................................................................................................. 4 D. Universal Flip-flop (JK-FF)............................................................................................... 5 BAB III PENDAHULUAN ........................................................................................................ 7 A. Metodologi tindakan ........................................................................................................ 7 B. Alat dan bahan eksperimen.............................................................................................. 7 C. Prosedur eksperimen ....................................................................................................... 8 BAB IV LANDASAN TEORI ....................................... Ошибка! Закладка не определена. A. Diagram state ....................................................... Ошибка! Закладка не определена. B. State table ............................................................ Ошибка! Закладка не определена. C. State Assigment table .......................................... Ошибка! Закладка не определена. D. State equation table ................................................ Ошибка! Закладка не определена. E. Final Schematic ................................................... Ошибка! Закладка не определена. F. Implemntasi Rangkaian dengan bahan-bahan ....... Ошибка! Закладка не определена. ii BAB V PENUTUP ......................................................... Ошибка! Закладка не определена. A. Kesimpulan .......................................................... Ошибка! Закладка не определена. B. Saran .................................................................... Ошибка! Закладка не определена. Daftar pustaka ................................................................. Ошибка! Закладка не определена. iii DAFTAR TABEL Tabel 3.1 alat dan bahan ............................................................................................................. 8 iv DAFTAR GAMBAR Gambar 2. 1 Tabel kebenaran dan rangkaian ............................................................................. 3 Gambar 2. 2 IC jk ff.................................................................................................................... 5 Gambar 3. 1 Seven segmnent mpx ............................................................................................. 7 Gambar 3. 2 project board .......................................................................................................... 7 Gambar 3. 3j umper .................................................................................................................... 7 Gambar 3. 4 ic j .......................................................................................................................... 7 Gambar 3. 5 Resistror ................................................................................................................. 8 Gambar 3. 6 ic 7447 ................................................................................................................... 8 v BAB 1 PENDAHULUAN A. Latar Belakang Flip-flop merupakan suatu rangkaian sekuensial yang dapat menyimpan data sementara (latch) dimana bagian outputnya akan merespon input dengan cara mengunci nilai input yang diberikan atau mengingat input tersebut. Flip-flop juga adalah sebagai rangkaian untuk memori yang merupakan salah satu bagian yang penting dari sebuah computer. Ada dua macam memori yaitu memori tipe Non Volatile yang merupakan memori yang dapat menyimpan atau mengingat suatu informasi atau data untuk jangka waktu lama dan memori tipe Volatile yang merupakan memori yang dapat menyimpan informasi selama sambungan listrik tersambung. Memori tipe Volatile terdiri atas memori dinamik dan memori static. Flip-flop termasuk tipe memori statik. Perubahan dari setiap keadaan output dapat terjadi jika diberikan trigger pada flip-flop tersebut. Triger nya berupa sinyal logika 1 dan 0 yang kontinu. Ada 4 (empat) tipe Flip-flop yang dikenal yaitu SR, JK, D dan T Flip-flop. Dua tipe pertama merupakan tipe dasar dari Flip-flop, sedangkan D dan T merupakan turunan dari SR dan JK Flipflop. B. Rumusan Masalah Berdasarkan uraian judul di atas, maka permasalahan yang akan dikaji adalah sebagai berikut: 1. Apa fungsi dari Universal Flip – Flop (JK – FF) ? 2. Bagaimana Cara Kerja Universal Flip – Flop (JK – FF) ? 1 C. Tujuan Berdasarkan latar belakang dan rumusan masalah yang telah kelompok kami tetapkan, tujuan dari dilaksanakannya percobaan ini adalah sebagai berikut : 1. Mengetahui fungsi dari Universal Flip – Flop (JK – FF). 2. Mengetahui cara kerja dari Universal Flip – Flop (JK – FF) dalam penelitian Pemanfaatan energi Surya sebagai alternatif bahan bakar mobil. D. Manfaat Laporan tugas besar ini diharapkan bermanfaat baik secara teoritis maupun praktis sebagai berikut : 1. Manfaat Secara Teoritis Penulisan secara teoritis diharapkan dapat menambah wawasan dan pemahaman dasar teori terhadap dari konsep Universal Flip – Flop (JK – FF). 2. Manfaat Secara Praktis Laporan tugas besar ini bermanfaat bagi masyarakat umum maupun bagi mahasiswa sebab dengan adanya laporan tugas besar ini dapat meningkatkan wawasan mengenai fungsi, cara kerja, dan pengaplikasian dari konsep Universal Flip – Flop (JK – FF). 2 BAB 2 LANDASAN TEORI A. Rangkaian Sekuensial Rangkaian sekuensial adalah rangkaian logika yang outputnya dipengaruhi oleh input saat ini dan output sebelumnya. Rangkaian sekuensial dapat dikatakan pula sebagai rangkaian logika yang bekerja berdasarkan urutan waktu. Adapun contoh dari rangkaian sekuensial yaitu flip flop, counter, register, dan detektor sekuensial. Flip-flop adalah rangkaian logika yang digunakan untuk menyimpan satu bit secara semi permanen sampai ada suatu perintah untuk menghapus atau mengganti isi dari bit yang disimpan. Flip-flop bekerja berdasarkan control dari sinyal clock. Prinsip dasar dari flip-flop adalah suatu komponen elektronika dasar seperti transistor, resistor dan dioda yang dirangkai menjadi suatu gerbang logika yang dapat bekerja secara sekuensial. Flip-flop merupakan bentuk dasar dari rangkaian logika sekuensial. Pada dasarnya flip flop berasal dari basic cell NAND atau basic cell NOR, yang sering disebut RS-flip- flop (SET RESET flip-flop). Berikut gambar rangkaian, dan table kebenaran dari RS flip-flop: Gambar 2.1 (Tabel Kebenaran dan Rangkaian) Tidak seperti gerbang logika, flip-flop mempunyai dua keluaran komplementer. Keluaran tersebut diberi lambang Q dan 𝑄�̅. Keluaran Q merupakan keluaran normal dan paling sering digunakan pada kondisi normal dan 𝑄�̅merupakan komplemen dari Q. B. Macam-macam flip-flop Flip flop memiliki 4 macam diantaranya yaitu: Data Flip – Flop (D – FF) D-FF adalah sebuah flip-flop yang memiliki satu data input dimana operasi dari flip-flop ini dikontrol oleh sebuah sinyal clock, sehingga saat 3 clock aktif terus tanpa mengalami perubahan logic level maka noise logic dapat terkunci dan diteruskan ke output next state. D-FF disusun dengan menambahkan gerbang NOT antara masukkan S dan R. Universal Flip – Flop (JK – FF) JK-FF memiliki dua input yang mempengaruhi keluaran. Operasi flip flop JK sama dengan operasi flip-flop SR, kecuali pada masukkan, JK diperbolehkan kondisi J=K=1. Bila kondisi seperti itu maka keadaan Q akan berubah tanpa memperhatikan keadaan Q sebelum ada detak. Sifat master slave terlihat pada output table operasi yang selalu sama dengan masternya (J ). Istilah dari JK Flip Flop diambil dari nama penemunya yaitu Jack Kilby. Toggle Flip – Flop (T – FF) T-FF mempunyai sifat “Toggle”, artinya saat input T = 1 maka output = complement output sebelum clock aktif. karena output selalu berlawanan dengan kondisi awalnya, sehingga saat Clock aktif terus dan input T=1 maka output akan berosilasi. Set Reset Flip Flop (RS – FF) RS Flip-flop yaitu rangkaian Flip-Flop yang mempunyai 2 output. Nilai output yang keluar selalu berlawanan satu dengan yang lain. FlipFlop ini memiliki 2 input yaitu R (Reset) dan S (Set). C. Clock Clock adalah salah satu masukan yang ada dalam beberapa rangkaian Flip-flop. Rangkaian komputer menggunanakan ribuan flip-flop. Untuk mengkoordinasi kegiatan keseluruhan, sinyal umum yang bernama kunci-waktu (clock) dikirimkan ke setiap flip-flop. Sinyal ini mencegah flip-flop berubah keadaan sebelum waktunya. Ada beberapa kondisi clock yang biasa digunakan untuk menyerempakkan kerja flipflop yaitu : Tepi naik : perubahan sinyal clock dari logika rendah (0) ke logika tinggi (1) 4 Tepi turun : perubahan sinyal clock dari logika tinggi (1) ke logika rendah (0) Logika tinggi : saat sinyal clock berada dalam logika 1 Logika rendah : yaitu saat sinyal clock berada dalam logika 0 D. Universal Flip – Flop (JK – FF) Rangkaian JK flip-flop sebenarnya merupakan rangkaian modifikasi dari RS flip-flop yang dimodifikasi sedemikian rupa sehingga hasil tabel kebenaran RS flip-flop hampir mirip dengan JK flip-flop. BedanyaBedanya adalah pada JK flip-flop tidak terdapat kondisi terlarang. JK flip-flop mempunyai 2 input yaitu input J dan input K. RangkaianRangkaian JK flip-flop merupakan rangkaian flip-flop yang paling universal karna JK flip-flop mempunyai semua sifat flip flop lainnya baik dari RS flip-flop maupun D flip-flop. Kelebihanlah JK flip dapat dirubah menjadi rangkaian T flip-flop JK flip-flop sering disebut dengan JK FF induk hamba atau Master Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF dan Slave FF. Master Slave JK FF ini memiliki 3 buah terminal input yaitu J, K dan Clock. Sedangkan IC yang dipakai untuk menyusun JK FF adalah tipe 7473 yang mempunyai 2 buah JK flip-flop dimana layoutnya dapat dilihat pada Vodemaccum IC (Data bookc IC). Kelebihan JK FF terhadap FF sebelumnya yaitu JK FF tidak mempunyai kondisi terlarang artinya berapapun input yang diberikan asal ada clock maka akan terjadi perubahan pada output. Dalam rangkaian digital JK flip-flop disimbolkan sebagai gambar berikut : Gambar 2.2 (JKFF) Prinsip kerja JK flip-flop hampir sama dengan RS flip-flop hanya saja kondisi terlarang sudah dihilangkan dan pada kondisi tersebut JK flip-flop dapat berubah menjadi Tanggung flip-flop. Pada RS flip-flop saat kedua input bernilai 1 merupakan kondisi terlarang maka tidak berlaku demikian jika pada JK flip-flop. PadaPada JK flip5 flop saat kedua input J dan K bernilai 1 maka flip-flop tersebut akan berubah menjadi flip-flop toogle atau T flip-flop. JK flip-flop master atau slave merupakan pengembangan dari RS flip-flop dan JK flip-flop. Pada JK flip-flop master atau slave ini dibangun dari 2 bagian yaitu bagian Master (Majikan) dan bagian Slave (Budak). Kedua bagian pada JK flip-flop master slave tersebut pada dasarnya adalah RS flip-flop atau JK flip-flop. Prinsip kerja dari JK flip-flop master / slave adalah sebagai berikut. Pertama, flip-flop master terpicu-pinggiran-positif dan flip-flop slave terpicu-pinggiran-negatif. Oleh karenanya, flip-flop master memberikan tanggapan terhadap masukan-masukan J dan K nya sebelum flip-flop slave. Jika J=1 dan K=0, flip-flop master diset pada saat pinggiran pulsa clock positif diberikan. Keluaran Q yang tinggi dari flip-flop utama mendrive masukan J pada flip-flop slave, maka pada saat pinggian pulsa clock negatif diberikan, flip-flop slave diset, menyamai kerja flip-flop master. Jika J=0 dan K=1, flipflop master direset pada saat pinggiran naik pulsa clock diberikan. Keluaran Q yang tinggi dari flip-flop master menuju ke masukan K pada flipflop slave. Oleh karenanya, kedatangan pinggiran turun pulsa clock mendorong flipflop slave untuk reset. Sekali lagi, flip-flop slave menyamai kerja flip-flop master. Jika masukan J dan K pada flip-flop master adalah tinggi, maka flip-flop ini toggle pada saat pinggiran pulsa clock positif diberikan sedang flip-flop slave toggle pada saat pinggiran pulsa clock negatif diberikan. Dengan demikian, apapun yang dilakukan oleh flip-flop master, akan dilakukan pula oleh flip-flop slave: jika flip-flop master diset, flip-flop slave diset; jika flip-flop master direset, flip-flop slave direset pula. 6 BAB 3 METODOLOGI A. Metodologi tindakan Penulisan karya tulis ilmiah ini menggunakan metode penelitian eksperimen, yaitu bentuk penelitian percobaan. B. Alat dan bahan Eksperimen 1 7 segmen mpx Gambar 3.1 2 project board Gambar 3.2 3 jumper Gambar 3.3 4 ic jk ff 7473 Gambar 3.4 7 5 resistor Gambar 3.5 6 ic 7447 Gambar 3.6 Tabel 3.1 C. Prosedur Eksperimen Langkah untuk membuat counter up desimal seven segment menggunakan JKFF: 1. Membuat State diagram 2. Membuat State table 3. Membuat State assignment table 4. Membuat State equation dan output 5. Membuat final schematic 6. Membuat Implementasin rangkain dengan menggunakan bahan-bahan seperti: 7 segmen mpx project board jumper ic jk ff 7473 resistor ic 7447 8 BAB 4 PEMBAHASAN A. Diagram State B. State Table C. State assignment table D. State equation dan output E. Final schematic F. Implementasin rangkain dengan menggunakan bahan-bahan 9 BAB 5 PENUTUP A. Kesimpulan Kesimpulan yang dapat kita buat dari makalah ini yaitu flipflop merupakan rangkaian yang dapat bekerja hanya dengan dua buah input dan output secara berlawanan. Flip flop juga merupakan rangkaianyang penting dalam sistem elektronik digital dan juga elemen penyimpanan dasar pada logika sekuensial yang digunakan pada komputer, alat komunikasi dan tipe elektronik lainnya. Clock adalah salah satu masukan yang ada dalam beberapa rangkaian Flip-flop. Sinyal clock mencegah flip-flop berubah keadaan sebelum waktunya. JK flip-flop sering disebut dengan JK FF induk hamba atau Master Slave JK FF karena terdiri dari dua buah flip-flop, yaitu Master FF dan Slave FF. Sedangkan tabel kebenaran digunakan untuk mengetahui benar atau tidaknya rangkaian yang telah kita buat. B. Saran Menurut pendapat kelompok kami, Diharapkan untuk peneliti selanjutnya dapat menyempurnakan fitur dan juga eror yang ada pada rangkaian sehingga dapat menyempurnakan rangkaian yang telah dibuat agar lebih maksimal. Dan diharapkan untuk peneliti selanjutnya agar bisa membuat rangkain sequiential dengan cara yang lebih mudah,simple dan pastinya lebih baik dari peneliti sebelumnya. 10 DAFTAR PUSTAKA Modul Praktikum Sistem digital Telkom University. Mei 2018. Publikasi Ilmiah " MAKALAH ELEKTRONIKA DIGITAL JK FLIP FLOP”. Universitas Negeri Makassar. Makassar. 11