Analisis Rangkaian Sekuesial

advertisement

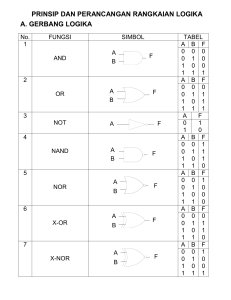

[Analisis Rangkaian Sekuensial] BAB VI Analisis Rangkaian Sekuesial a. Prosedur Analisis Clocked Synchronous State Machine Clocked artinya bahwa storage elemen (flip-flop) bekerja berdasarkan input clock, dan Synchronous artinya seluruh flip-flop dipicu oleh sinyal clock yang sama (bersamaan). State memory adalah set n flip-flop yang dimasukkan dalam current state machine dan memiliki 2n keadaan. Terdapat 2 cara untuk membuat rangkaian sekuensial, yaitu : 1. Mealy machine Pada Mealy machine output merupakan fungsi dari present state dan nilai dari inputnya. 2. Moore machine Pada Moore machine, output merupakan fungsi dari current state saja. Gambar 6.1 menunjukkan blok diagram mealy machine dan moore machine. Gambar 6.1. Blok Diagram Mealy dan Moore Machine Flip-flop dikoneksikan dengan sinyal clock yang menyebabkan keadaan state berubah pada setiap clock. Next State logic F dihasilkan oleh [Analisis Rangkaian Sekuensial] BAB VI current state dan input. Keduanya baik F dan G merupakan rangkaian kombinasional. Sehingga dapat dinotasikan sebagai berikut : 𝑁𝑒𝑥𝑡 𝑆𝑡𝑎𝑡𝑒 = 𝐹 𝐶𝑢𝑟𝑟𝑒𝑛𝑡 𝑆𝑡𝑎𝑡𝑒, 𝐼𝑛𝑝𝑢𝑡 𝑂𝑢𝑡𝑝𝑢𝑡 = 𝐺(𝐶𝑢𝑟𝑟𝑒𝑛𝑡 𝑆𝑡𝑎𝑡𝑒, 𝑖𝑛𝑝𝑢𝑡) Persamaan output diatas digunakan untuk rangkaian sekuensial model moore. State machine menggunakan positive-edge-triggerd D flip-flop sebagai state memory, dimana clock terjadi pada saat rising edge pada sinyal clock. b. Persamaan Output Pada rangkaian sekuensial model mealy, persamaan outputnya adalah : 𝑂𝑢𝑡𝑝𝑢𝑡 = 𝐺(𝑐𝑢𝑟𝑟𝑒𝑛𝑡 𝑠𝑡𝑎𝑡𝑒) Sehingga perbedaan antara 2 model moore dan mealy adalah bagaimana output dihasilkan. Pada perancangan rangkaian berkecepatan tinggi, dibutuhkan untuk memastikan bahwa output state machine tersedia sedini mungkin dan tidak berubah selama periode clock. Salah satu cara untuk mendapatkannya adalah dengan mengenkode state sehingga state variabel dapat menghasilkan output. Hal ini disebut dengan output-coded state assigment. Pendekatan lainnya adalah mendesain state machine sehingga output selama satu periode clock terjadi pada state dan input selama clock sebelumnya, bisa disebut sebagai pipelined output, dan menghasilkan memory stage yang lain pada mesin output. Gambar 6.2. adalah mesin mealy dengan pipelined output. Gambar 6.2. Mealy machine dengan pipelined output c. Tabel Keadaan Functional Behaviour dari dari latch dan flip-flop dapat didekripsikan secara formal dengan persamaan karakteristik yang menspesifikasikan kondisi next state flip-flop , sebagai fungsi dari current state dan input. [Analisis Rangkaian Sekuensial] BAB VI Persamaan Karakteristik flip-flop disajikan pada tabel 6.1. Nilai Q adalah nilai Next Value dari Q. Persamaan karakteristik tidak mendeskripsikan secara detail timing behaviour, hanya functional respons saja sebagai pengontrol input. Tabel 6.1. Tabel Persamaan Karakteristik Tipe Flip-flop Persamaan karakteristik S-R Latch D Latch Edge-triggered D Flip-flop D flip-flop dengan enable Master/slave S-R Flip-Flop Master/Slave J-K Flip-Flop Edge Triggered J-K Flip-Flop T Flip-Flop T Flip-Flop dengan enable Q = S + R’.Q Q=D Q=D Q = EN.D + EN’.Q Q = S + R’.Q Q = J.Q’ + K’.Q Q = J.Q’ + K’.Q Q = Q’ Q= EN.Q’ + EN’ . Q d. Diagram keaadaan Sebuah state diagram menggambarkan perubahan kondisi dari sebuah variable (dalam hal ini adalah variable output) dari kondisi awal ke kondisi berikutnya. Kondisi dari variable tersebut berubah karena adanya pengaruh input dari luar. State diagram terdiri dari variable Output, dilambangkan dalam bentuk lingkaran dan variable input yang mempengaruhinya, dilambangkan dalam bentuk panah yang keluar dari masing-masing lingkaran. Gambar 6.3 adalah ilustrasi diagram keadaan untuk model mealy dan moore. [Analisis Rangkaian Sekuensial] BAB VI Gambar 6.3. State Diagram Mealy machine dan Moore Machine e. Clocked Syncronous state machine Analysis Tujuan dari menganalisis clocked syncronous state machine adalah untuk menentukan kondisi next state dan fungsi output, sehingga sifat dari rangkaian dapat diprediksi. Langkah-langkah dalam menganalisis clocked syncronous state machine : 1. Menentukan persamaan eksitasi untuk flip-flop control input 2. Menggantikan persamaan eksitasi kedalam persamaan karakteristik, untuk mendapatkan persamaan eksitasi 3. Gunakan persamaan transisi untuk membangun tabel transisi 4. Menentukan persamaan output 5. Tambahkan nilai output pada tabel transisi untuk tiap state (Moore) atau kombinasi state/input (Mealy) untuk menghasilkan tabel transisi / output 6. Berikan nama state dan mengganti nama state untuk kombinasi state variabel pada tabel transisi / output untuk menhasilkan tabel state/output 7. (pilihan) gambarkan state diagram yang sesuai dengan tabel state/output. [Analisis Rangkaian Sekuensial] BAB VI Contoh 6.1: Persamaan eksitasinya : 𝐷0 = 𝑄0 + 𝑄1′ ′ = 𝑄0′ . 𝑄1 𝐷1 = 𝑄0 Output : 𝑌 = 𝑄0 . 𝑄1 𝑍 = 𝑄1 Persamaan Transisi : 𝑄0 𝑡 + 1 = 𝐷0 = 𝑄0′ . 𝑄1 𝑄1 𝑡 + 1 = 𝐷1 = 𝑄0 Tabel Keadaan : Y Z Q1 Q2 Q1(t+1) Q2(t+1) 0 0 0 0 0 0 0 1 0 1 0 1 1 0 0 0 0 0 1 1 1 1 1 1 State Table / state name : S Y Z A A 0 0 B C 0 1 C B 0 0 D B 1 1 S(t+1) [Analisis Rangkaian Sekuensial] BAB VI Persamaan transisi : 𝑄0 𝑡 + 1 = 𝐷0 = 𝑄0′ . 𝑄1 𝑄1 𝑡 + 1 = 𝐷1 = 𝑄0 State Diagram : Contoh 2 : Persamaan eksitasi : D0 = X Y’Q2 D1 = X Q0 D2 = Y’ + Q1 Persamaan karakteristik : Q0(t+1) = D0 Q1(t+1) = D1 Q2(t+1) = D2 Persamaan transisi : Q0(t+1) = D0 = X Y’ Q2’ [Analisis Rangkaian Sekuensial] BAB VI X 1 1 - Y 0 0 - Q1(t+1) = D1 = X Q0 Q2(t+1) = D2 = Y’ + Q1 Q2 0 - Q1 1 Q0 1 - 11 A,11 C,11 E,01 G,11 A,11 C,11 E,00 G,10 10 F,11 H,11 F,01 H,11 E,11 G,11 E,00 G,10 Output : Z1 = X Q0 + Q1’ /Z2= (Q1 Q2)’ Tabel Keadaan : Tabel output : XY S A B C D E F G H 00 E,11 E,11 E,01 E,01 E,11 E,11 E,00 E,00 01 A,11 A,11 E,01 E,01 A,11 A,11 E,00 E,00 [Analisis Rangkaian Sekuensial] BAB VI State Diagram : Analisis dengan J-K Flip-Flop State Machine Terdapat 2 persamaan eksitasi tiap flip-flopnya (J,K). Persamaan karakteristik Q(t+1) = J.Q(t)’ + K’.Q(t). Langkah-langkah analisis terhadap rangkaian sama seperti analisis dengan D Flip-flop. Contoh : [Analisis Rangkaian Sekuensial] BAB VI Persamaan eksitasi : J1 = X K1 = X.Y J2 = X’ K2 = 0 Persamaan karakteristik Q(t+1) = J.Q’ + K’.Q Q1(t+1) = J1.Q1’ + K1’.Q1 Q2(t+1) = J2.Q2’ + K2’.Q2 Persamaan transisi : Q1(t+1) = X.Q1’ + (X.Y)’.Q1 = X.Q1’ + X’.Q1 + Y’.Q1 Q2(t+1) = X’.Q2’ + 0’.Q2 = X’. Q2’ + Q2 Mealy Output : Z = X.Q1 + Q2 Tabel keadaan : [Analisis Rangkaian Sekuensial] BAB VI Penamaan state / output : State Diagram : SOAL TUGAS : 1. Analisis rangkaian berikut ini : Buatlah persamaan eksitasi, tabel eksitasi / transisi, state/output tabel untuk (A-D, untuk Q1, Q2 = 00 - 11) dan state diagramnya [Analisis Rangkaian Sekuensial] BAB VI 2. Analisislah rangkaian clocked synchronous state machine : a. Buatlah persamaan eksitasi, tabel eksitasi/transisi, tabel state/output (gunakan nama state A – H untuk Q1 Q2 Q3 = 000 - 111 ), bualah state diagramnya. b. Buatlah persamaan eksitasi, tabel eksitasi/transisi, tabel state/output (gunakan nama state A – H untuk Q2 Q1 Q0 = 000 - 111 ), bualah state diagramnya. 3. Analisislah rangkaian clocked synchronous state machine : a. Buatlah Persamaan eksitasi, persamaan transisi,tabel transisi, dan tabel state/ output (gunakan nama state A – D untuk Q1 Q2 = 00 - 11). Gambarkan state diagram. b. [Analisis Rangkaian Sekuensial] BAB VI Buatlah Persamaan eksitasi, persamaan transisi,tabel transisi, dan tabel state/ output (gunakan nama state A – D untuk Q1 Q0 = 00 - 11). Gambarkan state diagram. 4. Analisislah rangkaian clocked synchronous state machine : Buatlah Persamaan eksitasi, persamaan transisi,tabel transisi, dan tabel state/ output (gunakan nama state A – D untuk Q1 Q2 = 00 - 11). Gambarkan state diagram. f. Clocked Syncronous state machine Synthesis Langkah-langkah dalam mendesain atau melakukan sintesis terhadap clocked syncronous state machine adalah sebagai berikut : 1. Membuat tabel keadaan / output yang disesuaikan dengan deskripsi / spesifikasi menggunakan nama mnemonic untuk keadaan / state. Dapat dimulai dengan state diagram. 2. Minimalkan jumlah state pada tabel keadaan/output 3. Pilihlah state variabel dan masukkan kombinasi state variabel pada nama state. 4. Gantikan kombinasi state variabel ke dalam tabel state/output untuk membentuk tabel transisi/output yang menyajikan kombinasi next statevariabel dan output untuk tiap kombinasi state/input. 5. Pilihlah flip-flop yang akan digunakan sebagai state memory. 6. Membuat tabel eksitasi yang merupakan representasi dari nilai eksitasi yang tersedia untuk mendapatkan next state untuk setiap kombinasi state/input. 7. Mendapatkan persamaan eksitasi dari tabel eksitasi 8. Mendapatkan persamaan output dari tabel transisi / output. 9. Menggambarkan persamaan logicnya dalam rangkaian yang ada pada statevariabel dan membangun rangkaian berdasarkan persamaan eksitasi dan output. Syntesis rangkaian sekuensial dengan D Flip-flop Tabel eksitasi sama seperti fungsi kombinasional (D1,D2,D3) dan menghasilkan 5 variabel (A, B, Q1, Q2, Q3). Tabel 6.2 menunjukkan adalah tabel eksitasi dan output menggunakan D flip-flop [Analisis Rangkaian Sekuensial] BAB VI Q1 0 1 1 1 1 Tabel 6.2. Tabel eksitasi dan output menggunakan D Flip-flop Q2 Q3 AB 00 01 11 10 0 0 100 100 101 101 0 0 110 110 101 101 0 1 100 100 111 111 1 0 110 110 111 101 1 1 100 110 111 111 D1 D2 D3 Gambar 6.4. adalah map karnaugh untuk D1 D2 D3. (a) (b) Z 0 0 0 1 1 [Analisis Rangkaian Sekuensial] BAB VI (c) Gambar 6.4. Map karnaugh untuk (a) D1; (b) D2; (c) D3 Dari map karnaugh tersebut dihasilkan persamaan berikut ini : 𝐷1 = 𝑄1 + 𝑄2′ . 𝑄3′ 𝐷2 = 𝑄1. 𝑄3′ . 𝐴′ + 𝑄1. 𝑄3. 𝐴 + 𝑄1. 𝑄2. 𝐵 𝐷3 = 𝑄1. 𝐴 + 𝑄2′ . 𝑄3′ . 𝐴 Persamaan outputnya, adalah sebagai berikut : 𝑍 = 𝑄1. 𝑄2. 𝑄3′ + 𝑄1. 𝑄2. 𝑄3 = Q1.Q2 Jika dalam contohnya menggunakan minimal-cost pada persamaan eksitasi, digunakan dont care untuk masukan next – state untuk state yang tidak digunakan. Sehingga diperoleh persamaan eksitasi dari map karnaugh : D1 = 1 D2 = Q1.Q3’.A’ + Q3.A + Q2.B D3 = A Dan outputnya Z = Q2 Map karnaugh dari persamaan menggunakan prinsip dont care ini disajikan pada gambar 6.5. [Analisis Rangkaian Sekuensial] BAB VI (a) (b) (c) Gambar 6.5 (a) map karnaugh untuk D1, (b) map karnaugh untuk D2, (b) map karnaugh untuk D3 [Analisis Rangkaian Sekuensial] BAB VI Rangkaian yang dihasilkan terlihat pada gambar 6.6. Gambar 6.6. Hasil Sinytesis rangkaian dengan D Flip-Flop Syntesis rangkaian sekuensial dengan JK Flip-flop Pada perancangan rangkaian sekuensial dengan JK Flip-flop digunakan tabel eksitasi flip-flop JK sebagai acuannya. Sebagai contoh keadaan 100 pada saat kombinasi input 00, Q1 = 1 dan Q1 next = 1, sehingga d0 dihasilkan pada J1 K1. Pada kombinasi state/input yang sama, Q2 = 0 dan Q2 = 1 sehingga 1d dihasilkan dari J2 K2. Gambar 6.6 adalah map karnaugh dari rangkaian sekunsial dengan JK Flip-Flop. (a) [Analisis Rangkaian Sekuensial] BAB VI (b) (c) Gambar 6.6. Hasil Sinytesis rangkaian dengan D Flip-Flop (a) untuk J1 K1, (b) untuk J2 K2, (c) untuk J3 K3 Walaupun next state, pada state yang tidak digunakan adalah 000. Pada map karnaughnya next state tidak diisi dengan 0 pada map yang berkorespondensi. Tabel kombinsai juga digunakan untuk menentukan kombinasi dari J dan K dibutuhkan untuk memperoleh next state Q = 0, untuk setiap masukan keadaan yang tidak dibutuhkan. Tabel 6.4 adalah tabel eksitasi dan output dari state machine menggunakan J-K Dlip-flop. Tabel 6.3 adalah tabel eksitasi dari JKFF. Tabel 6.3. Tabel Eksitasi JKFF Q NEXT Q J K 0 0 d 0 1 1 d 0 0 d 1 1 1 d 0 1 Tabel 6.4. Tabel Eksitasi dari output state machine Q1Q2Q3 000 100 101 110 111 00 1d,0d,0d d0,1d,0d d0,0d,d1 d0,d0,0d d0,d1,d1 AB 01 11 1d,0d,0d 1d,0d,1d d0,1d,0d d0,0d,1d d0,0d,d1 d0,1d,d0 d0,d0,0d d0,d0,1d d0,d0,d1 d0,d0,d0 J1K1, J2K2,J3K3 Z 10 1d,0d,1d d0,0d,1d d0,1d,d0 d0,d1,1d d0,d0,d0 Dari map karnaugh tersebut diperoleh persamaan berikut : 𝐽1 = 𝑄2′ . 𝑄3′ 𝐽2 = 𝑄1. 𝑄3′ . 𝐴′ + 𝑄1. 𝑄3. 𝐴 𝐽3 = 𝑄2′ . 𝐴 + 𝑄1. 𝐴 𝐾1 = 0 𝐾2 = 𝑄1′ + 𝑄3′ . 𝐴. 𝐵′ + 𝑄3. 𝐴′ . 𝐵′ 𝐾3 = 𝑄1′ + 𝐴′ 0 0 0 1 1 [Analisis Rangkaian Sekuensial] BAB VI Pendekatan lainnya adalah dengan memasukkan nilai dont care pada map karnaugh sehingga diperoleh persamaan berikut : 𝐽1 = 1 𝐾1 = 0 𝐽2 = 𝑄1. 𝑄3′ . 𝐴′ + 𝑄3. 𝐴 𝐽3 = 𝐴 𝐾2 = 𝑄3′ . 𝐴. 𝐵′ + 𝑄3. 𝐴′ . 𝐵′ 𝐾3 = 𝐴′ Dari persamaan diatas diperoleh rangkaian sekuensial menggunakan JKFF, yang ditunjukkan pada gambar 6.7. Gambar 6.7. Rangkaian State Machine menggunakan J-K Flip-Flop SOAL TUGAS 1. Desainlah sebuah clocked synchronous state machine dengan tabel state/output menggunakan D Flip-flop, gunakanlah 2 variabel Q1, Q2 dengan kondisi state A = 00, B = 01, C = 11, D = 10. Berdasarkan Tabel keadaan berikut ini : X S A B C D 0 B C B B 1 D B A C NEXT STATE : S Z 0 0 1 0