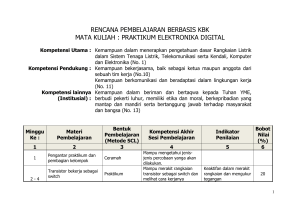

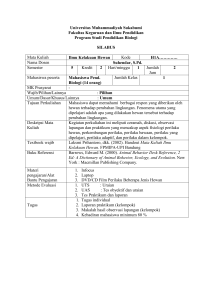

praktikum sistem digital dan mikroprosesor

advertisement