1 bab 2 - SAP Gunadarma

advertisement

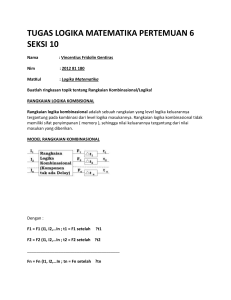

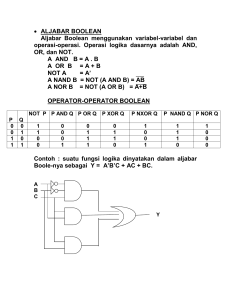

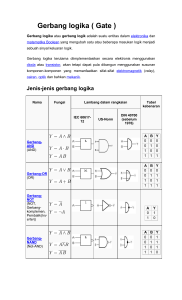

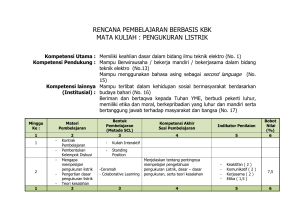

RENCANA PEMBELAJARAN SEMESTER PROGRAM STUDI xxxxx – FAKULTAS - yyyy UNIVERSITAS GUNADARMA Tanggal Penyusunan Fakultas Program Studi Jenjang Kode dan Nama MK SKS dan Semester Prasyarat Status Mata Kuliah Dosen Pengampu 07/09/2016 Tanggal revisi TEKNIK KOMPUTER Kode Prodi: DIPLOMA (D3) IT014345 SISTEM DIGITAL SKS 3 Semester 3 (TIGA) Telah mengikuti mata kuliah Matematika Diskrit 1 dan Elektronika Dasar [ ] Wajib [... ] Pilihan 1. Capaian Pembelajaran Mata Kuliah Deskripsi Umum (Silabus) Metode Pembelajaran Pengalaman 24/02/2017 Menunjukkan sikap bertanggungjawab atas pekerjaan di bidang keahliannya secara mandiri; 2. Menginternalisasi nilai, norma, dan etika akademik; Sikap 3. Menginternalisasi semangat kemandirian, kejuangan, dan kewirausahaan. (KKNI_Aptikom L-11) 1. Mampu menyelesaikan pekerjaan berlingkup luas dan menganalisis data dengan beragam metode yang sesuai, baik yang belum maupun yang sudah baku; 2. Mampu menunjukkan kinerja bermutu dan terukur; 3. Mampu memecahkan masalah pekerjaan dengan sifat dan konteks yang sesuai dengan bidang keahlian terapannya didasarkan pada pemikiran logis, inovatif, dan bertanggung jawab atas hasilnya secara mandiri; 4. Mampu menyusun laporan hasil dan proses kerja secara akurat dan sahih serta mengomunikasikannya secara efektif kepada pihak lain yang membutuhkan; 5. Mampu bekerja sama, berkomunikasi, dan berinovatif Ketrampilan dalam pekerjaannya; Umum 6. Mampu bertanggungjawab atas pencapaian hasil kerja kelompok dan melakukan supervisi dan evaluasi terhadap penyelesaian pekerjaan yang ditugaskan kepada pekerja yang berada di bawah tanggungjawabnya; 7. Mampu melakukan proses evaluasi diri terhadap kelompok kerja yang berada dibawah tanggung jawabnya, dan mengelola pengembangan kompetensi kerja secara mandiri; 8. Mampu mendokumentasikan, menyimpan, mengamankan, dan menemukan kembali data untuk menjamin kesahihan dan mencegah plagiasi. (KKNI_Aptikom. L-11) 1. Menguasai konsep sistem digital dan mampu untuk mengembangkan dan mengimplementasikan ke dalam Pengetahuan sistem komputer khususnya sistem tertanam. (KKNI_Aptikom. L-11) 1. Mampu menganalisis, merancang, dan mengimplementasikan perangkat keras (device) berbasis Ketrampilan teknologi komputer sistem tertanam (embedded) pada Khusus bidang terkait sesuai kebutuhan. Isian borang (5.1.1.1) Mata kuliah ini ditujukan agar mahasiswa maapu merancang rangkaian digital dan mengaplikasikan ke dalam sistem komputer. 1. Ceramah/Kuliah Pakar 4. Praktik Laboratorium ..... 2. Problem Based Learning/FGD .... 5. Self-Learning (V-Class) ..... 3. Project Based Learning ..... 6. Lainnya: diskusi, Praktek, tugas a. Tayangan Presentasi . c. Online exercise/kuiz (V-class) Belajar/Tugas Referensi / Sumber Belajar b. Review textbook/Jurnal e. Lainnya: .......... [1]. [2]. [3]. [4]. [5]. [6]. ..... d. Laporan Malvino, Elektronika Komputer Digital, terj. Dali S Naga, Gunadarma Suryadi, Agus S, Dasar Rangkaian Logika, jilid I, Gunadarma Bartee, Thomas C, Dasar Komputer Digital, terj. The How Liong, ed. 6, Penerbit Erlangga, 1994 Wakerle, John F, Digital Principles and Practices, Prentice Hall, 1994 Lee, Samuel C, Rangkaian Digital dan Rancangan Logika, terj. Sutisno, Erlangga, 1991 Mano M, Morris and Kime R, Charles, Logic and Computer Design Fundamentals, Prentice Hall, 1997 [7]. Malvino and Leach, Digital principles and Applications, ed 5, Mc Graw Hill, 1995 [8]. Tocci, Ronald J, Digital Systems Principles and Applications, ed 6, Prentice Hall, Minggu Kemampuan Akhir yang Diharapkan Bahan Kajian (Materi Pelajaran) Metode/Bentuk Pembelajaran Waktu (Menit) Belajar 1. 2. 3. 4. Mahasiswa mampu mengkonversikan dan mengkodean sistem bilangan Belajar : (CE-DIG-3 Number systems and data encoding) Konversi bilangan Biner, Hex ASCII Code Exces-3 Code Gray Code Mahaiswa mampu mengoperasikan Aljabar boolean serta Karnaugh Map untuk penyederhanaan rangkaian Belajar : Dasar operasi boolean AND, OR dan NOT serta NAND, NOR dan XOR (CE-DIG-4 Boolean algebra applications ) Praktek : Penyederhanaan ekspresi Boolean dengan peta Karnaugh Penerapan rangkaian digital setelah disederhanakan peta karnaugh Mahasiswa mampu menjelaskan jenis-jenis gerbang digital serta impementasi kedalam operasi Boolean. Belajar : Rangkaian gerbang digital AND, OR dan NOT serta NAND, NOR dan XOR (CE-DIG-5 Basic logic circuits) Praktek : Implementasi ekspresi boolean kedalam rangkaian digital Mahasiswa mampu Belajar : Ceramah Diskusi Kriteria Penilaian (Indikator) Praktek 3 x 160 Bobot Nilai (%) Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan Ceramah Diskusi Praktek 1 x 160 Ceramah Diskusi Praktek 1 x 160 Ceramah 1 x 160 2 x160 5% Tanya-jawab Dimensi : Pemahaman 5% Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan 2 x160 Tanya-jawab 1 bab 2 ; 2 bab 8,10 ; 5 bab 3 ; 6 bab 2 ; 8 bab 3 ; 5% 1 bab 2 ; Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan Tanya-jawab Dimensi : Pemahaman 1 bab1 ; 2 bab 1 ; 3 bab 2 ; 4 bab 2 ; 5 bab 2 ; 6 bab 1 ; 7 bab 5 ; 8 bab 2 . 1 bab 2 ; 2 bab 8,10 ; 5 bab 3 ; 6 bab 2 ; 8 bab 3 ; 5% Dimensi : Pemahaman 2 x160 Sumber belajar mengoperasikan rangkaian gerbang digital dua tingkat (CE-DIG-5 Basic logic circuits) Rangkaian gerbang digital AND-OR, OR_AND, NAND-NAND dan NORNOR Diskusi Praktek Ceramah Diskusi Praktek 1 x 160 Ceramah Diskusi Praktek 1 x 160 Ceramah Diskusi Praktek 1 x 160 Implementasi ekspresi boolean kedalam rangkaian digital 5. Mahasiswa mampu menjelaskan dan mendisain rangkaian kombinasional multiplexer dan demultiplexer (CE-DIG-6 Modular design of combinational circuits) 6. Mahasiswa mampu menjelaskan dan mendisain rangkaian kombinasional decoder dan encoder (CE-DIG-6 Modular design of combinational circuits) 7. Mahasiswa mampu menjelaskan dan mendisain operasi Binary : Adder, Subtrator, Multiplier dan Divider (CE-DIG-6 Modular design of combinational circuits) Belajar : Multiplexer dan demultiplexer Praktek : Menganalisis dan merancang sirkuit kombinasional (misalnya, aritmatika logic unit, ALU) Belajar : Decoder dan encoder Menganalisis dan merancang sirkuit kombinasional (misalnya, aritmatika logic unit, ALU) Belajar : Binary Adder & Subtractor Binary Multiplier & Divider Praktek : Menganalisis dan merancang sirkuit kombinasional (misalnya, aritmatika logic 2 bab 8,10 ; 5 bab 3 ; 6 bab 2 ; 8 bab 3 ; Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan 2 x160 Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan 2 x160 5% Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan 2 x160 5% Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan 10 % I bab 3 II bab 2,6 III bab 3 IV bab 4,6 V bab 3 VI bab 3 VII bab 3 VIII bab 4 I bab 3 II bab 2,6 III bab 3 IV bab 4,6 V bab 3 VI bab 3 VII bab 3 VIII bab 4 I bab 5 II bab 11 III bab 4 IV bab 7 V bab 4,5,6 VI bab 4 unit, ALU) 8. 9. 10. Mahasiswa mampu menjelaskan dan merancang operasi latch (D, RS) Belajar : Latch D, RS: definisi , cara kerja (CE-DIG-7 Modular design of sequential circuits) Menganalisis dan membuat diagram waktu untuk operasi Latch D, RS Mahasiswa mampu menjelaskan dan merancang operasi filp-flops (D,JK,T) Belajar : Flip-flops D, JK, T : definisi , cara kerja (CE-DIG-7 Modular design of sequential circuits) Praktek : Menganalisis dan membuat diagram waktu untuk operasi flip-flops D, JK, T. Mahasiswa mampu menjelaskan dan merancang operasi rangkaian sekuensial register, register geser (CE-DIG-7 Modular design of sequential circuits) 11. 12. Belajar : Register : definisi , cara kerja , jenis-jenis Ceramah Diskusi Praktek 1 x 160 2 x160 Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Ceramah Diskusi Praktek 1 x 160 2 x160 Ceramah Diskusi Praktek Kurang memuaskan Tanya-jawab Dimensi : Pemahaman 10 % Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas 5% 1 x 160 2 x160 Kurang memuaskan Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Praktek : Menganalisis dan membuat diagram waktu untuk sekuensial operasi Register Kurang memuaskan 5% VII bab 8 VIII bab 5 I bab 3 II bab 2,6 III bab 3 IV bab 4,6 V bab 3 VI bab 3 VII bab 3 VIII bab 4 I bab 3 II bab 2,6 III bab 3 IV bab 4,6 V bab 3 VI bab 3 VII bab 3 VIII bab 4 I bab 5 II bab 11 III bab 4 IV bab 7 V bab 4,5,6 VI bab 4 VII bab 8 VIII bab 5 UJIAN TENGAH SEMESTER Mahasiswa mampu menjelaskan operasi rangkaian sekuensial Belajar : Counter: definisi , cara kerja, Ceramah Diskusi 1 x 160 2 x160 Tanya-jawab Dimensi : Pemahaman I bab 5 II bab 11 jenis-jenis counter counter (CE-DIG-7 Modular design of sequential circuits) 13. Mahasiswa mampu menggunakan dasar operasi perangkat lunak Xilinx sebagai perancangan sistem digital (dalam bentuk skematik) 14. Mahasiswa mampu menggunakan bahasa pemrograman VHDL untuk menghasilkan rangkaian digital dasar 15. Mahasiswa mampu menggunakan bahasa pemrograman Xilinx dan VHDL untuk menghasilkan rangkaian digital dasar Praktek Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Praktek : Menganalisis dan membuat diagram waktu untuk sekuensial operasi Counter. Belajar : Perangkat lunak Xilinx : implementasi rangkaian digital menggunakan Xilinx Ceramah Diskusi Praktek 1 x 160 Belajar : Perangkat lunak VHDL : implemantasi rangkaian digital menggunakan VHDL Ceramah Diskusi Praktek 1 x 160 Ceramah Diskusi Praktek 1 x 160 Tanya-jawab 2 x160 Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan Dimensi : Pemahaman 10 % 10 % Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan Praktek : Simulasi rangkaian digital menggunakan VHDL Belajar dan Praktek Simulasi rangkaian digital menggunakan Xilinix dan VHDL Kurang memuaskan 2 x160 Tugas 11 Praktek : Simulasi rangkaian digital menggunakan Xilinx 10 % 2 x160 Tanya-jawab Dimensi : Pemahaman Penilainan kompetensinya : Sangat memuaskan Memuaskan Batas Kurang memuaskan 10 % III bab 4 IV bab 7 V bab 4,5,6 VI bab 4 VII bab 8 VIII bab 5 I bab 5 II bab 11 III bab 4 IV bab 7 V bab 4,5,6 VI bab 4 VII bab 8 VIII bab 5 I bab 5 II bab 11 III bab 4 IV bab 7 V bab 4,5,6 VI bab 4 VII bab 8 VIII bab 5 I bab 5 II bab 11 III bab 4 IV bab 7 V bab 4,5,6 VI bab 4 VII bab 8 VIII bab 5 16. UJIAN AKHIR SEMESTER 100 % Keterangan : 1 SKS = 160 menit terdiri dari:, 60 menit kegiatan mandiri 50 menit kegiatan terstruktur 50 menit tatap muka Catatan : Sistem Digital adalah mata kuliah kerja mandiri, dimana mahasiswa akan mempraktekan teori. Kegiatan dilakukan di kelas dengan membawa perlengkapan praktek sendiri per kelompok kerja Kebutuhan sarana praktek No 1 2 3 4 5 6 7 8 9 10 11 Nama Komponen Protoboard Multitester Kabel isi tunggal Battery 9 V dan Konektor Voltage Regulator / 7805 LED Seven segment common cathoda IC 7408&7409 (Gerbang AND) IC 7400 (Gerbang NAND) IC 7416 (Inverter) IC 7417 (Buffer) Jumlah 1 1 15 2 2 12 2 1 4 1 1 Catatan Terdiri dari 5 warna Beragam warna No 12 13 14 15 16 17 18 19 20 21 22 Nama Komponen IC 7432 (OR) IC 7428 (NOR) IC 74135 (EXOR) IC 7474 (D-Flip Flop) JK Flip Flop IC 7447 (Decoder Seven Segment) IC 74190 (Counter) IC 74181 (ALU) Tool Set Gunting Resistor 1 K Ohm Jumlah 1 1 1 1 1 2 1 1 1 1 20 Catatan GRADING SCHEME COMPETENCE KRITERIA 1 : Kelengkapan isi rangkuman DIMENSI Sangat Memuaskan Kelengkapan konsep Lengkap dan terpadu Memuaskan Batas Kurang Memuaskan Di bawah standard SKOR Lengkap Masih kurang beberapa aspek yang belum terungkap Hanya menunjukkan sebagian konsep saja Tidak ada konsep Memuaskan Diungkap dengan tepat tetapi deskriptif Batas Sebagian besar konsep sudah terungkap, namun masih ada yang terlewatkan Kurang Memuaskan Kurang dapat mengungkapkan aspek penting, melebihi halaman, tidak ada proses merangkum hanya mencontoh Di bawah standard Tidak ada konsep yang disajikan SKOR 2 KRITERIA 3a : Komunikasi tertulis DIMENSI Sangat Memuaskan Bahasa Paper Bahasa menggugah pembaca untuk mencari tahu konsep lebih dalam Memuaskan Bahasa menambah informasi pembaca SKOR 1 Paper cukup menarik, Kurang Memuaskan Informasi dan data yang disampaikan tidak menarik dan membingungkan Dijilid namun kurang Di bawah standard Tidak ada hasil Kerapian Paper Batas Bahasa deskriptif, tidak terlalu menambah pengetahuan Dijilid biasa KRITERIA 2 : Kebenaran isi rangkuman DIMENSI Sangat Memuaskan Kebenaran Diungkapkan dengan konsep tepat, terdapat aspek penting, analisis dan membantu memahami konsep 2 KRITERIA 3 : Daya tarik komunikasi/presentasi Paper dibuat dengan Tidak ada hasil 1 sangat menarik dan menggugah semangat membaca KRITERIA 3b : Komunikasi lisan DIMENSI Sangat Memuaskan Isi Memberi inspirasi pendengar untuk mencari lebih dalam Organisasi Gaya Presentasi Sangat runtut dan integratif sehingga pendengar dapat mengkompilasi isi dengan baik Menggugah semangat pendengar walau tidak terlalu mengundang Memuaskan Menambah wawasan Cukup runtut dan memberi data pendukung fakta yang disampaikan Membuat pendengar paham, hanya sesekali saja memandang catatan rapi Batas Pembaca masih harus menambah lagi informasi dari beberapa sumber Tidak didukung data, namun menyampaikan informasi yang benar Lebih banyak membaca catatan Kurang Memuaskan Informasi yang disampaikan tidak menambah wawasan bagi pendengarnya Informasi yang disampaikan tidak ada dasarnya Di bawah standard Informasi yang disampaikan menyesatkan atau salah Tidak mau presentasi Selalu membaca catatan (tergantung pada catatan) Tidak berbunyi SKOR 2 1 1

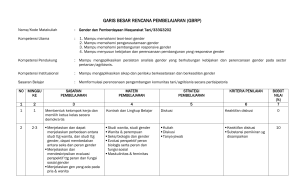

![garis-garis besar program pengajaran [gbpp]](http://s1.studylibid.com/store/data/000328347_1-8bbd90f4538915768028fd059c159009-300x300.png)