disain komparator presisi teknologi cmos ams

advertisement

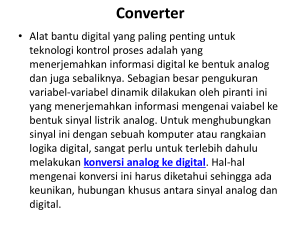

DISAIN KOMPARATOR PRESISI TEKNOLOGI CMOS AMS-0,35J.1ID UNTUK ADC-PIPELINE 80 MSPS Any K. Yapie', Dyah Nur+ainingsih'', Suci Br. Kembaren", Hamzah Afandi". Teknik Elektro, 3Teknik Informatika, Fakultas Teknologi Industri,Universitas Gunadarma JI. Margonda Raya 100 Depok, 16424 1 [email protected], 2 [email protected], 3suci [email protected] [email protected] ',2,4 Abstrak Disain ADC-pipeline (analog to digital converter) yang diaplikasikan untuk kamera kecepatan tinggi mengambil bagian yang penting pada sistem akusisi piksel kolom secara paralel sebagai pengkonversi piksel analog ke digital. Karena sinyal analog dari sensor kamera CMOS kecepatan tinggi 10,000 frame/s yang dilakukan dengan menggunakan matrik 64x64 piksel (4096 piksellframe) memerlukan pemrosesan sinyallebih lanjut. Untuk mendukung kinerja kamera tersebut, diperlukan 64 ADC yang dipasang paralel dengan spesifikasi ADC yang harus memiliki laju konversi tinggi, daya dan tegangan rendah, serta resolusi tinggi. Pemilihan ADC jenis pipeline dengan resolusi keluaran 8 bit 80 MSPS sangat tepat. Setiap stage ADC-Pipeline dibangun oleh komparator bersama dengan penguat operasional dan sakelar kapasitor, serta clock non-overlapping dan sistem delay untuk menghasilkan resolusi 8 bit yang seirama. Fungsi komporator sangat signifikan yaitu menghasilkan digital biner dari proses DAC pada saklar kapasitor. Kemampuan komparator yang memiliki kecepatan, tegangan histerisis yang presisi dan daya rendah digunakan untuk mengurangi kesalahan DNL, INL dan tegangan residu. Untuk kebutuhan itu dibutuhkan komparator presisi tinggi dengan spesifikasi Vos "" OV, tegangan set poin VSP = 1,65V dan konsumsi daya rendah < ImW. Disain dan sirnulasi Komparator Presisi pada ADC-Pipeline dilakukan dengan perangkat lunak Mentor Graphics dengan teknologi CMOS AMS-0,35Ilm. Kata kunci : ADC pipeline, I bit per stage, komparator 1. Pendahuluan. .lC"'ixei CMOS untuk sensor gambar telah berkembang dalam beberapa tahun terakhir sebagai altematif yang menjanjikan untuk menggantikan teknologi yang konvensional, yaitu Charge Coupled Devive (CCD). CMOS menawarkan konsumsi daya yang rendah, lebih fungsional dan memungkinkan untuk mengintegrasikan sistem terpadu ke dalam chip tunggal. Proyek penelitian dalam pengembangan kamera kecepatan tinggi 10.000 frames/s pada Gambar 1 memerlukan ADC jenis Pipeline 64 buah secara parallel[41[6][71. Disain ADC pada Gambar 2 dengan kecepatan tinggi yaitu 80 MSPS harus memiliki akurasi dan resolusi yang tinggi. Untuk mendukung kinerja ADC terse but diperlukan komponen penyusun yang valid pada setiap stagenya[1][21.Salah satu komponen tersebut adalah komparator yang berfungsi untuk membandingkan sinyal masukan dengan tegangan acuan (sub-ADC) dan mengubahnya ke dalam biner digital. Spesifikasi komparator harus memiliki tegangan histerisis yang presisi, kecepatan tinggi dan daya rendah. • • 64 64 :eamlkJ Digital Processors Elernenrs Gambar I. Blok kamera CMOS 10.000 frames/s One Ek1 Per SIage ADC One Ek1 Per SIage ADC ~------------------f · . ·· h--il >-----<{}-!-----;-J· .. Vres(N ... D(N-2) Gambar 2. Diagram ADC Pipeline I-bit! stage 369 2. Komparator Presisi Komparator presisi diimplementasikan pada setiap stage dari ADC. Disain ini menggunakan komparator presisi dengan pengkoreksi digital untuk meminimalkan kesalahan offset komparator dan untuk memperoleh output yang lebih baik. Komparator berfungsi sebagai pembanding sinyal masukan dengan tegangan acuan (sub-ADC). Keluaran komparator merupakan logika biner 0 atau I. Simbol dan blok diagram komparator presisi ditampilkan pada Gambar 3[1][2][3][5]. Masing-masing Blok diperlihatkan pada Gambar 4. Blok pertama adalah Pre-arnplifier jenis differensial dan diatur untuk input kapasitansi dengan beban aktif. Ukuran transistor M 1 dan M2 ditetapkan dengan mempertimbangkan transkonduktansi diff-arnp dan input kapasitansi. Blok ke-dua adalah umpan balik yang positif atau rangkaian decision, yang merupakan jantung (inti) dari komparator yang berfungsi untuk mengubah arus ke tegangan. Rangkaian ini menggunakan umpan balik positif dari hubungan silang gerbang M8 dan M9 untuk meningkatkan gain dari elemen decision. Dan blok yang ke-tiga adalah output buffer, yang mengubah output dari rangkaian decision menjadi sinyal logika. Inverter (MI8 dan M19) ditambahkan untuk mengisolasi apapun beban kapasitansi dari bias penguat diferensialnya. 3. Perancangan Gambar 3. Diagram Komparator Presisi Komparator ini terdiri dari tiga blok, yaitu Preamplifier, rangkaian decision (keputusan) dan output buffer (penyangga). s-- 30 - -,i Presisi ADC l-bit/stage memerlukan sub-ADC yang teliti dan memiliki ketepatan dan kecepatan tinggi. Komparator ini adalah komparator presisi yang memiliki Vos ""OV seperti Gambar 5. l - M3 Komparator I V0I+ i V0I-) U V0l0lJT) --i 15·,·· 20_ IS ------- .~- _ // ---- VSP 10 __ r.r~ - , '/ ,t-:·~I t. _ ~!. '. - Co,TI.".,.:""",1 00_.,/ 1~~'~i~~I~'-'1 ~'-'I~' '1-"-'1- .,,"'J _I 00 (a) Rangkaian Pre-amplifier - -- .J . t- ~~, I ~t) 1; M1 ~_ ....,-- t- - .1, M'IO ~ I 1 -, '>-\ v,> I -- 10 IS 2' 0 2' 5 ) 0 Gambar 5. Transient DC Offset Komparator Presisi. Disain komparator presisi dapat dimulai dengan langkah sebagai berikut; ! I "!v~ r$htr[1?r t-ils!-:reSI5 I 05 (of') (b) Rangkaian Decision • Mendisain blok pre-amp yang berfungsi mengubah level tegangan ke level arus seperti pada Gambar 6, dengan menentukan penguatan komparator A v ::::::5 untuk meminimalkan offset error dengan Iss = 30J-lA supaya mendapatkan mode bersama pada tegangan= 1,65V. MI4 MI3 [ ] L J .j{~ •• --.--...: I /,fl'-, I.n'} ,....J ---,- L _ (c) Rangkaian Penyangga Gambar 4. Rangkaian Komparator Presisi 370 Gambar 6. Rangkaian Pre-Arnp Diketahui VOS3= 1,6SV dan IDJ = ISflA maka ukuranM3 adalah: P B v SPH I Kp W D3=--(VCSJ +Vmp) 2 2L 2 = v". -vo, (1) _I Iss PA =-'n- jorP B ~PA (6) ' gm ~+I P.• ---) VSPH= VSPL= 40m V dari V sp. ~ (W )3=1,2 L jika L3=O,3Sflm maka W3 = O,4flm J2.kp.: I DJ= 48flAN Dangm3 = (2) sehingga dapat diketahui nilai gm I; W1 -JKn LI Av= gml- (3) gm3CW3 • Mendisain blok penyangga (buffer) seperti pada Gambar 8 yang merupakan rangkaian pengubah level tegangan differensial ke logika biner (0 dan I), dengan menerapkan pembiasan sendiri dan menambahkan penyangga not untuk meningkatkan penguatan dan mengisolasi dari beban kapasitifterhadap pembiasan sendiri. l~PL3 VDD ~S=gml ---)dangml=248flAN 48 dan dapat untuk menentukan ukuran MI ; (W)I=IO,8 L M15 ~.)- Jt I i -c---r--J-' r M7- I [M3 -"------J.------"-----r-- Gnd Gambar 7. Rangkaian Decision Untuk menentukan ukuran M7 sampai dengan MII, harus diketahui spesifikasi dari rangkaian decision, VSP = 1,6SV. Dengan catatan level Vo+ dan Vo- dibatasi pada 2VTHN= 0,92V. Sehingga VOS7,!O = 0,6S9V dan Vosu = 0,73V dan ukuran M7=MI0, M8=M9 dan Mll adalah sebagai berikut; 10+ ID7=IDJO=T W M~ Gnd Gambar 8. Rangkaian Penyangga . i. Tab e 11 P er hirtungan Manua IK omparator Pr esrs Arus Komponen Parameter MOS Ml 3,S/O,35 NMOS 15 M2 3,S/O,35 NMOS 15 M3 0,4/0,35 PMOS 15 0,4/0.35 M4 PMOS 15 0,4/0,35 M5 PMOS 15 M6 0,4/0,35 PMOS 15 0,7/0,35 M7 NMOS 7,5 MS 1,4/0,35 NMOS 7,5 M9 1,4/0,35 NMOS 7,5 0,710,35 MIO NMOS 7,5 MII 1,54/0,35 NMOS 30 MI2 4,210,35 PMOS 30 MJ3 2,1/0,35 PMOS 15 MI4 2,1/0,35 PMOS 15 MI5 0,7/0,35 NMOS 15 MI6 0,7/0,35 NMOS 15 MI7 1,4/0,35 NMOS 30 MIS 4,2/0,35 PMOS 30 MI9 1,4/0,35 NMOS 30 PD Disipasi 19MOS 396,SuW (4) =7,S flA dan ukuran (-)7,10=2 OVo ill • Mendisain blok decision, sebagai jantung komparator yang mengubah arus menjadi tegangan dengan menambahkan penggeser level histeresis untuk meminimalkan noise yang terjadi seperti pada Gambar 7. ".. M13 V~~ danjika Ll= 0,3Sf.1mmaka Wl = 3,8flm. Sehingga ukuran M 1=M2 dan M3=M4=MS=M6. Besar 10+ = 10- = IS flA (awaI). 10+ i L=O,3Sflm, W=O,7 um L Dengan syarat fl7 = fll0 = flA dan fl8 = fl9 = JlB liB> 2flA sehingga ukuran M8 dan M9 adalah L=O,3SflID,W=I,4 urn, Diketahui ID!! = 30flA, maka ukuran M 11; (W)II [DII *2 = 4,4 L Kn*(Vcs -vmNi sehingga nilai L=0,3Sflm, W=I,S4 urn. Dan (S) Dimana VO+ dan Vo- bergerak dari titik tengah 1,6SV atau VDD/2 maka dapat ditentukan ukuran M 12 sampai M 19 dengan aturan dari gerbang NOT. M18 dan M19 membentuk gerbang NOT, sehingga ukuran transistor PMOS = 2/3 dan NMOS = 1/3 jika Ll8,19 = 0,3Sflm, W18= 1,4 urn dan W19= 4,2flm. Dengan cara yang sama maka dapat ditentukan ukuran ; M12 ; Ll2 = 0,3Sf.1m,W18= 4,2 urn MI3 dan M14; L13,14 = 0,3Sflm, W13, 14 = 2, I urn MIS dan MI6; LlS,16 = 0,3Sf.1m, W15, 16= 0,7 urn M17; Ll7 = 0,3Sf.1m,W17= 1,4 urn 371 4. Simulasi Komparator Presisi Pada unit komparator presisi (sub-ADC), simulasi ditekankan pada offset komparator dan level histerisis untuk menekan noise. Simulasi pengujian tersebut adalah : • Simulasi Pengujian tegangan offset Vos. ,.___ • •••• __ , __ °r ..- __ "· • _H rr __ .~_. - __ ._ -s -~~":".,~~;o;.;.:':~-: ~::-:-..:~;.~ Gambar 11. Hasil Simulasi Karakteristik Penyangga ~_ !'U ... Tegangan set point penyangga (NOT) pada posisi 1,66V mendekati level setpoint perhitungan : 1,65V., dengan level keluaran pada logika biner (0= OV dan 1 = 3,3V). Pergerakan tegangan bias dari O,72V sampai dengan 2,6V . _-_._--_ ... _-----.-------" 's >" • Pengujian transient komparator presisi. " ----_._----' .'. J Gambar 9. Hasil Simulasi Karakteristik Vos r . : \I r''\ ~:: i\r' N !\ ' : : : 1 .. .£. j : r ii I] U LJ f'\ \ ~ \1 ' , :' 1.,~ i i i ~ ' \ r r f t/I illI jj I: I ,! ~! 1! •••••• I I I i: I Dengan memberikan masukan Vin- dengan tegangan DC 1,65V dan masukan Vin+ variabel DC dari OV sampai dengan 3,3V, didapatkan perubahan keluaran (Vout) dengan titik setpoint pada 1,65V. Saat Vin OV s/d 1.65V maka Vout = OV (0) kemudian saat Vin bergerak dari 1,65V s/d 3,3V maka Vout = 3,3V (I) n r-r- .' ;1 - i , , l< -, I~ I1 I) : 1 j ,; fl I I, :1 if j! I fJ I - (a) Sinusoidal • Simulasi Pengujian tegangan setpoint VSP. Hasilnya diperlihatkan pada Gambar 10 dan Tabel 2. tu -" - -: - - - - i- - - - - - - - " :: ~ •• _ •• ':i .•.-- /' m'''''~~'''h i~ ·1 , (b) (kotak) r-" i Gambar 12. Hasil Simulasi Karakteristik Delay ! :\ ~'_ Gambar 10. Hasil Simulasi ;!illB Karakteristik VSP Tabel 2. Perbandingan Hasil Perhitungan Manual dan Simulasi VSP No I 2 3 372 Parameter Vo+ VoVSP Manual 0,73V s/d 2,57V 0,73V s/d 2,57V 1,65V Simulasi 0,84V s/d 2,48V 0,1 V s/d 2,43V 1,18V Gambar 12 adalah hasil pengujian dengan melihat efek delay perbandingan antara Vin- dan Vin+ dengan keluaran Vout. Frekuensi yang diberikan adalah 80MHz. Pada gelombang kotak dihasilkan perbedaan periode tinggi dan rendah dan ini tidak dijumpai pada simulasi dengan gelombang sinus. Tabel3. Perubahan Nilai WfL Pada Komparator Presisi Simul-2 Keterangan Simul-I No I 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 MI M2 M3 M4 M5 M6 M7 M8 M9 MIO MII MI2 MI3 MI4 MI5 MI6 MI7 MI8 MI9 PD VSP 3,8/0,35 3,8/0,35 0,4/0,35 0,4/0.35 0,4/0,35 0,4/0,35 0,7/0,35 1,4/0,35 1,4/0,35 0,7/0,35 1,54/0,35 4,2/0,35 2,1/0,35 2,110,35 0,7/0,35 0,7/0,35 1,4/0,35 4,2/0,35 1,4/0,35 396,8uW 1,18V 21/0,35 21/0,35 0,4/0,35 0,4/0.35 0,4/0,35 0,4/0,35 0,4/0,35 1,4/0,35 1,4/0,35 0,4/0,35 mendekati 1,65V, dengan arus bergerak dari Ml l , dengan perbandingan dari MI2 s/d MI5 yaitu ~12 x ~15 = ~A dan ~13 x ~14 = ~B ~B> 2~A., M3 s/d M7 membentuk cermin arus yang berfungsi menghasilkan 10+ dan 10- dan mengkontrol nilai Vo+ dan Vo-. M8 s/d MlO sebagai sumber arus tetap untuk bias M5 dan menghasilkan arus Iss. Perubahan nilai W/L komparator presisi ditampilkan pada Tabel3. 5. Kesimpulan Hasil perancangan komparator presisi diperoleh nilai komsumsi daya 410,5611W (di bawah I m W). Tegangan set point (VSP) terdapat perbaikan dari 1,18V menjadi 1,36V mendekati 1,65V, perubahan nilai W/L dari perancangan simulasi-I menjadi simulasi-2 untuk mendapatkan kinerja komparator yang memiliki presisi yang tinggi dalam mengkonversikan biner digital. Disain Lay-out komparator presisi sebesar 781lm x 981lm. 14/0,35 2,110,35 2,110,35 2,110,35 1,4/0,35 1,4/0,35 1,4/0,35 2,110,35 1,4/0,35 41O,56uW 1,36V Gambar 13. Rangkaian Simulasi -2 Komparator Presisi. Vt •.•. •..•v ••• .. :...;. Gambar 14. Lay Out Komporator Presisi. Gambar 14 adalah lay-out komparator presisi dengan ukuran 78llm x 981lm. Perubahan hasil simulasi pada tegangan VSP diperoleh 1,59V dan perubahan delay saat diberikan masukan.gelombang sinus dan kotak. Hal ini dikarenakan perubahan arah arus 10+ dan 10- yang menghasilkan Vo+ dan Vountuk menentukan tegangan setpoint pada level 7. Daftar Pustaka [I] Afandi, Hamzah; K, Any; Prasetyo Eri; Heruseto, Brahmantyo, 2009," Design Low Power 130mW Pipeline ADC With Speed 80 MSPS 8-bif' Industrial Electronics Seminar 2009 of Electronics Engineering Polytechnic Institute of Surabaya. [2] Afandi, Harnzah; Prasetyo Eri; Paindavoine, Michel, 2007," A 8-bits Pipeline ADC Design For High Speed Camera Application" Industrial Electronics Seminar 2007 of Electronics Engineering Polytechnic Institute of Surabaya [3] Baker, Jacob; Boyce, D. E., 1998, "CMOS Circuit Design, Layout and Simulation." IEEE Press on Microelectronic Systems. [4] Dubois, Jerome; Ginhac, Dominique; Paindavoine, Michel; Heyrman, Barthelemy, March 2008, "A 10 OOO/ps CMOS Sensor with Massively Parallel Image Processing", IEEE Journal of Solid-State Circuits, 43(3) :706-717. [5] Purnomo, Joko; Nur'ainingsih, Dyah; Afandi, Hamzah; Prasetyo, Eri, 2009" Disain Penguat Operasional (Op-amp) Dua Stage Untuk Aplikasi ADC Sigma Delta @) Dengan Kecepatan Tinggi Menggunakan CMOS Teknologi AMS 0,35pm". Industrial Electronics Seminar 2009 of Electronics Engineering Polytechnic Institute of Surabaya. [6] Prasetyo, Eri; Ginhac, Dominique; M. Paindavoine; July 2005 ,"Principles of CMOS sensors dedicated to face tracking and recognition", In IEEE CAMP05 International Workshop on Computer Architecture for Machine Perception [7] Paindavoine, Michel, June 2006, "High-speed camera with embedded real time image processing', in seminar information technology of Gunadarma University. 373