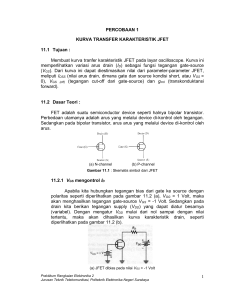

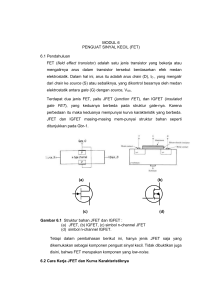

Prinsip kerja FET

advertisement

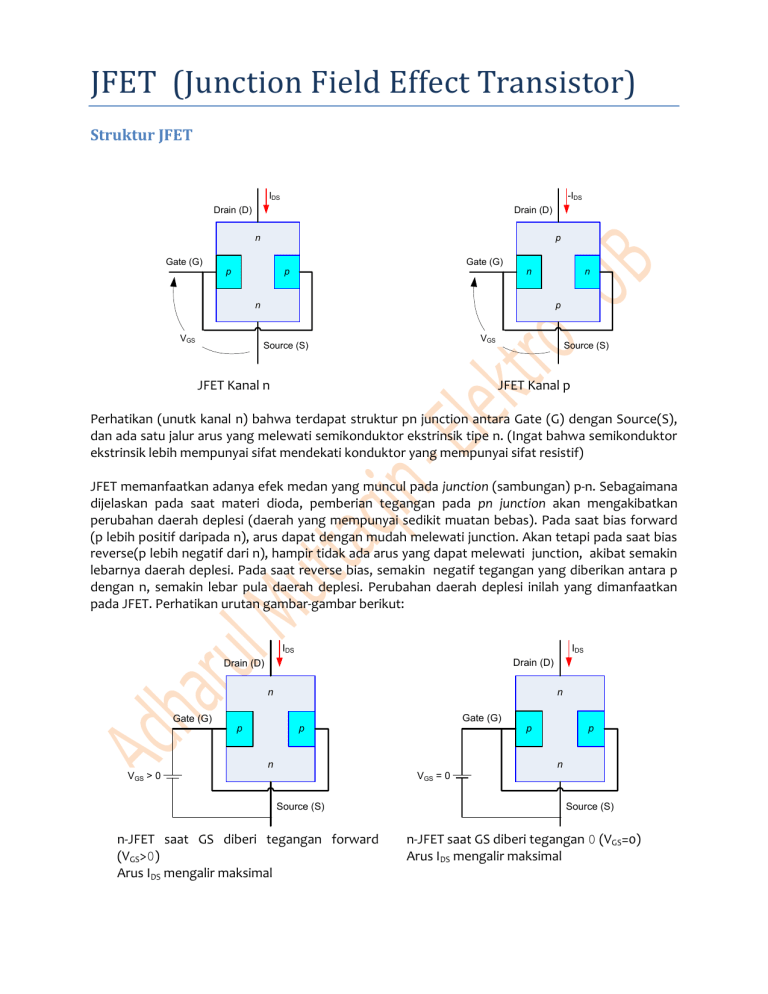

JFET (Junction Field Effect Transistor) Struktur JFET IDS -IDS Drain (D) Drain (D) n p Gate (G) Gate (G) p p n n VGS n p VGS Source (S) JFET Kanal n Source (S) JFET Kanal p Perhatikan (unutk kanal n) bahwa terdapat struktur pn junction antara Gate (G) dengan Source(S), dan ada satu jalur arus yang melewati semikonduktor ekstrinsik tipe n. (Ingat bahwa semikonduktor ekstrinsik lebih mempunyai sifat mendekati konduktor yang mempunyai sifat resistif) JFET memanfaatkan adanya efek medan yang muncul pada junction (sambungan) p-n. Sebagaimana dijelaskan pada saat materi dioda, pemberian tegangan pada pn junction akan mengakibatkan perubahan daerah deplesi (daerah yang mempunyai sedikit muatan bebas). Pada saat bias forward (p lebih positif daripada n), arus dapat dengan mudah melewati junction. Akan tetapi pada saat bias reverse(p lebih negatif dari n), hampir tidak ada arus yang dapat melewati junction, akibat semakin lebarnya daerah deplesi. Pada saat reverse bias, semakin negatif tegangan yang diberikan antara p dengan n, semakin lebar pula daerah deplesi. Perubahan daerah deplesi inilah yang dimanfaatkan pada JFET. Perhatikan urutan gambar-gambar berikut: IDS IDS Drain (D) Drain (D) n n Gate (G) Gate (G) p p p p n n VGS = 0 VGS > 0 Source (S) n-JFET saat GS diberi tegangan forward (VGS>0) Arus IDS mengalir maksimal Source (S) n-JFET saat GS diberi tegangan 0 (VGS=0) Arus IDS mengalir maksimal IDS Drain (D) n Gate (G) pp pp IG n VGS < 0 Source (S) n-JFET saat GS diberi tegangan reverse (VGS<0) Terjadi pelebaran daerah depelesi di sekitar junction. Arus IDS terhambat, sehingga arus yang mengalir tidak dapat maksimal IDS IDS Drain (D) n pp Drain (D) n Gate (G) IG IDS Drain (D) pp pp IG n VGS1 < 0 n Gate (G) pp IG n VGS2 < 0 Source (S) Gate (G) pp pp n VGS3 < 0 Source (S) Source (S) n-JFET saat GS diberi tegangan reverse (VGS3<VGS2 <VGS1<0) Semakin lebar daerah deplesinya, arus semakin sulit lewat. Pada VGS tertentu, arus yang lewat adalah nol. VGS pada kondisi ini desibut VGS(OFF) atau VP. Apa yang terjadi ketika VGS makin negatif? Ya benar, arus I tidak akan mengalir. DS Karakteristik IDS -- VGS n-JFET IDS IDSS V GS VP Hubungan antara arus IDS dan tegangan VGS memenuhi suatu persamaan 2 𝑉𝐺𝑆 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝑃 IDS= arus dari Drain ke Sourve VGS=tegangan antara Gate dan Source IDSS= arus maksimum dari Drain ke Source (suatu konstanta) VP= tegangan yang mengakibatkan arus IDS menjadi nol (suatu konstanta) Arus yang mengalir dari Drain ke Source: 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 𝑉𝐺𝑆 1− 𝑉𝑃 2 Arus Gate-Source (IGS) Bias tegangan apakah yang diberikan pada junction Gate-Source yang dapat mengatur arus IDS? reverse bias. Bagaimana arus yang lewat junction ketika kondisi reverse bias? Arus pada saat reverse bias adalah nol. Sehingga arus IG pada JFET adalah nol IG=0 Struktur MOS (Metal Oxide Semiconductor) Struktur MOS membentuk suatu lapisan metal (konduktor), oksida (isolator), dan semikonduktor, sebagaimana ditunjukkan gambar berikut: METAL OXIDE SEMICONDUCTOR Struktur MOS M ++++++++++++ O ----------------S p Suatu MOS ketika diberikan suatu tegangan antara metal dengan semikonduktornya. Perhatikan adanya muatan yang mungkin terkumpul di bawah lapisan oksida ketika pada metal terdapat muatan! Mengapa bisa terjadi? Apa pembawa muatan mayoritas pada semikonduktor tipe p? hole Apa yang terkumpul pada lapisan di bawah oksida pada gambar di atas? elektron Apakah terjadi perubahan sifat semikonduktor di bawah lapisan oksida? Ya, ada. Lapisan dibawah oksida menjadi semikonduktor tipe n, pembawa mayoritas sekarang adalah elektron. MOSFET (Metal Oxide Semiconductor Field Effect Transistor) Struktur MOSFET Gate (G) Source (S) Drain (D) n+ n n p Lapisan tipis tipe n, dibuat pada saat fabrikasi n-MOSFET Depletion Pada n-MOSFET depletion, sudah dibuatkan suatu lapisan tipe n (berlawanan dengan tipe semikonduktornya) dibawah lapisan oksida. Sehingga terdapat suatu jalur dengan type sama antara Drain dan Source. Jalur ini selanjutnya disebut channel. Pemberian tegangan VGS nantinya akan dapat mempengaruhi keberadaan channel ini, dari channel yang lebar menjadi channel yang sempit bahkan hilang. Gate (G) Source (S) Drain (D) n n p n-MOSFET Enhancement Pada n-MOSFET Enhancement, pembentukan channel akan terjadi saat VGS diberi tegangan (terjadi penambahan chanel, to enhance) Pengaruh Pemberian Tegangan pada MOSFET Arus yang pada MOSFET Arus ke Gate (IG) Perhatikan bahwa antara gate dengan lapisan lainnya dibatasi oleh silikon yang merupakan isolator yang sangat baik, sehingga arus yang dapat menembus (melewati) gate adalah nol. IG=0 Arus Drain Source (IDS) n-MOSFET Depletion. Prinsip kerja n-MOSFET Depletion sangat mirip dengan JFET, yaitu pemberian tegangan negatif antara Gate dan source dapat mengurangi lebar channel. Persamaan arus yang berlaku adalah sama yaitu 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 1 − 2 𝑉𝐺𝑆 𝑉𝑃 IDS= arus dari Drain ke Source VGS=tegangan antara Gate dan Source IDSS= arus maksimum dari Drain ke Source (Konstanta) VP= tegangan yang mengakibatkan arus IDS menjadi nol (konstanta) Arus yang mengalir dari Drain ke Source pada D-MOSFET: 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 𝑉𝑃 2 n-MOSFET Enhancement Prinsip kerja n-MOSFET Enhancement berbeda dengan kedua tipe FET sebelumnya. Pemberian tegangan VGS dimaksudkan untuk menambahkan adanya suatu channel dibawah lapisan oksida sehingga nantinya terdapat jalur arus dari Drain menuju Source. 𝐼𝐷𝑆 = 𝐾 𝑉𝐺𝑆 − 𝑉𝑇 2 IDS= arus dari Drain ke Source VGS=tegangan antara Gate dan Source K= Konstantan MOSFET (Ampere/Volt2) VT= tegangan VGS yang mengakibatkan arus IDS menjadi nol. Konstanta. Simbol-simbol FET JFET D D G G S S JFET kanal P JFET kanal N D-MOSFET D Bulk (Semikonduktor) Bulk (Semikonduktor) G S D-MOSFET kanal P D-MOSFET kanal N E-MOSFET D D Bulk (Semikonduktor) G S E-MOSFET kanal N Bulk (Semikonduktor) G S E-MOSFET kanal P Perhatikan bahwa simbol-simbol FET sangat mirip dengan struktur-struktur FET! Setuju? Pada simbol MOSFET, sering kali digambarkan tanpa menggunakan kaki Bulk. Jadi hanya terdapat D, G, dan S. Umumnya Bulk pada n terhubung dengan tegangan terendah, sedangkan Bulk tipe p terhubung dengan tegangan yang tertinggi. Pemberian Tegangan Bias pada JFET (Rangkaian dengan FET) Pada JFET kanal n, untuk membuat JFET aktif (arus dapat dikontrol oleh VGS) tegangan pada Drain lebih positif dibandingkan tegangan pada Source. Drain terhubung dengan VDD sedangkan Source terhubung dengan VSS atau Ground. Voltage Source Biasing 1k RD G VGS=-2V D Vp= -4V IDSS =12 mA S (1) Diketahui suatu rangkaian yang menggunakan JFET n-channel dengan IDSS=12mA dan VP=-4V seperti ditunjukkan gambar di atas. Antara VDD dengan Drain terdapat RD= 1k ohm Berapakah arus IDS dan tegangan VDS yang terjadi? Jawab: Sesuai dengan persamaan arus pada JFET n-channel bahwa : 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 𝑉𝑃 2 Maka 𝐼𝐷𝑆 −2𝑉 2 𝐼𝐷𝑆 = 12𝑚𝐴 1 − −4 1 2 1 = 12𝑚𝐴 1 − = 12𝑚𝐴 𝑥 = 3𝑚𝐴 2 4 Loop tegangan yang dibentuk oleh VDD, RD, FET, dan Ground mempunyai persamaan: 𝑉𝐷𝐷 = 𝐼𝐷 𝑅𝐷 + 𝑉𝐷𝑆 sehingga 10𝑉 = 3𝑚𝐴 𝑥 100𝑘Ω + 𝑉𝐷𝑆 Diperoleh 𝑉𝐷𝑆 = 10𝑉 − 3𝑚𝐴 𝑥 1𝑘Ω = 7𝑉 Self Bias Dengan RS VDD = +10V RD 1k IDS D IG Vp= -4V IDSS = 8 mA G RG 1M S RS 1,5k IDS (2) Diketahui suatu rangkaian yang menggunakan JFET n-channel dengan IDSS=8mA VP=-4V seperti ditunjukkan gambar di atas. Berapakah arus IDS dan tegangan VDS yang terjadi? Jawab: Persamaan arus yang terjadi pada JFET adalah 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 2 …………………… (i) 𝑉𝑃 Arus IG pada JFET adalah 0 A (Mengapa? Jika tidak bisa menjawab berarti halaman sebelumnya ada yang terlewat membacanya). VG=-IG RG = 0V Sementara itu, VGS=VG-VS Diperoleh VS=-VGS (Mengapa?) (Mengapa? Saudara pasti tahu) …………………… (ii) Arus IDS mengalir pada RS dan RD. VS=IDS RS Subtitusi Vs dengan (ii) diperoleh -VGS=IDS RS 𝐼𝐷𝑆 = − 𝑉𝐺𝑆 𝑅𝑆 …………….. (iii) 9 8 7 6 IDS 5 4 3 2 1 0 -5 -4 -3 -2 -1 0 VGS Diperoleh dua persamaan IDS dari (i) dan (ii), kita dapat mencari nilai VGS dari sini. Diperoleh: − 𝑉𝐺𝑆 𝑅𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 2 𝑉𝑃 Dengan RS=1.5kΩ, IDSS=8mA, dan VP=-4V diperoleh VGS=-2.26V atau VGS=-7.07V. (Hitunglah sendiri secara rinci, it’s about “persamaan kuadrat”) Karena rentang kerja arus IDS dapat mengalir jika VGS berada diantara VP dan 0V maka VGS yang mungkin adalah VGS=-2.26 Dengan demikian 𝑉 −2.26𝑉 𝐼𝐷𝑆 = − 𝐺𝑆 = − = 1.5𝑚𝐴 𝑅𝑆 VDD = +10V RD 1k IDS D IG VDS dapat dicari dengan menyelesaikan persamaan loop yang terbentuk dari VDD, RD, DS, RS, dan Ground 𝑽𝑫𝑫 = 𝑰𝑫𝑺 𝑹𝑫 + 𝑽𝑫𝑺 + 𝑰𝑫𝑺 𝑹𝑺 𝟏𝟎𝑽 = 𝟏. 𝟓𝒎𝑨 𝟏𝒌Ω + 𝑽𝑫𝑺 + 𝟏. 𝟓𝒎𝑨 𝟏. 𝟓𝒌Ω 𝑽𝑫𝑺 = 𝟔. 𝟐𝟓𝑽 Vp= -4V IDSS = 8 mA G RG 1M 1.5𝑘Ω S RS 1,5k IDS Mudah ya? Bias Pembagi Tegangan VDD = +15V RD 1k RG1 200k IDS D IG Vp= -4V IDSS =8 mA G RG2 100k RS 1,5k S IDS (3) Carilah IDS dan VDS untuk rangkaian di atas! Jawab: Persamaan arus yang terjadi pada JFET adalah 𝐼𝐷𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 2 𝑉𝑃 …………………… (i) Arus IG pada JFET adalah 0 A. VG= 𝑉𝐷𝐷 𝑅𝐺 1 +𝑅𝐺 2 𝑅𝐺2 (Mengapa? Karena IG=0 maka arus yang melewati RG1 dan RG2 adalah sama, sehingga …… silahkan dilanjutkan) VG= 5V Sementara itu, VGS=VG-VS Diperoleh VS=5V-VGS (Mengapa? Saudara pasti tahu) …………………… (ii) Arus IDS mengalir pada RS dan RD. VS=IDS RS Subtitusi Vs dengan (ii) diperoleh 5V-VGS=IDS RS 𝐼𝐷𝑆 = 5𝑉−𝑉𝐺𝑆 𝑅𝑆 …………….. (iii) 9 8 7 6 IDS 5 4 3 2 1 0 -5 -4 -3 -2 -1 0 VGS Diperoleh dua persamaan IDS dari (i) dan (ii), kita dapat mencari nilai VGS dari sini. Diperoleh: 5−𝑉𝐺𝑆 𝑅𝑆 = 𝐼𝐷𝑆𝑆 1 − 𝑉𝐺𝑆 2 𝑉𝑃 Dengan RS=1.5kΩ, IDSS=8mA, dan VP=-4V diperoleh VGS=-1.1 atau VGS=-8.2 V. (Hitunglah sendiri secara rinci, it’s about “persamaan kuadrat”) Karena rentang kerja arus IDS dapat mengalir jika VGS berada diantara VP dan 0V maka VGS yang mungkin adalah VGS=-1.1V Dengan demikian 𝐼𝐷𝑆 = 5−𝑉𝐺𝑆 𝑅𝑆 = 5−(−1.1𝑉) VDD = +15V RD 1k RG1 200k D IG = 4.07𝑚𝐴 VDS dapat dicari dengan menyelesaikan persamaan loop yang terbentuk dari VDD, RD, DS, RS, dan Ground 𝑽𝑫𝑫 = 𝑰𝑫𝑺 𝑹𝑫 + 𝑽𝑫𝑺 + 𝑰𝑫𝑺 𝑹𝑺 𝟏𝟓𝑽 = 𝟒. 𝟎𝟕𝒎𝑨 𝟏𝒌Ω + 𝑽𝑫𝑺 + 𝟒. 𝟎𝟕𝒎𝑨 𝟏. 𝟓𝒌Ω 𝑽𝑫𝑺 = 𝟒. 𝟖𝑽 Vp= -4V IDSS =8 mA G RG2 100k IDS 1.5𝑘Ω RS 1,5k S IDS Mudah juga ya? Tugas: 1. 2. 3. 4. 5. Ulangi contoh-contoh di atas dengan tulisan tangan saudara. Ulangi contoh (1) dengan VDD=12 V, VGS=-2V, VP=-3V, IDSS= 6mA, RD=1kΩ Ulangi contoh (2) dengan VDD=22 V, RG=1MΩ, VP=-2.5V, IDSS= 6mA, RD=1kΩ, RS=1.5kΩ Ulangi contoh (3) dengan VDD=21 V, RG1=500kΩ, RG2=1MΩ,VP=-3V, IDSS= 9mA, RD=1kΩ, RS=1.5kΩ Diketahui rangkain JFET bias pembagi tegangan. JFET yang digunakan adalah mempunyai IDSS=9mA dan VP=-3V. VDD yang digunakan adalah 15V dan RG2 yang terpasang adalah 100kΩ. Berapakah RG1, RS, RD yang harus dipasang agar diperoleh VG=5V, IDS=4mA, dan VD=11V? 6. Diketahui Rangkain Self Bias JFET dengan menggunakan VDD 22V. JFET yang digunakan mempunyai karakteristik VP=-2.5V dan IDSS=6mA. Pada rangkaian juga sudah terpasang RG=1MΩ. Jika diinginkan IDS=5mA dan VDS=15, berapakah nilai RD dan RS yang harus dipasang? Kumpulkan langsung tugas pada hari Senin, 13 Desember 2010, antara jam 10 s.d 14.00 (kecuali yang sedang kuliah penuh pada jam tersebut silahkan konfirmasi langsung dengan saya). Saya tunggu di ruangan saya di depan Lab. Infomatika dan Komputer. Tugas ini harus dikumpulkan sendiri, karena sekaligus akan dilakukan evaluasi untuk masing-masing mahasiswa. Pertanyaan dapat dilakukan lewat sms atau email. Terima kasih.