Field Effect Transistor (FET) - Danny Kurnianto

advertisement

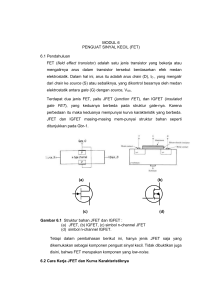

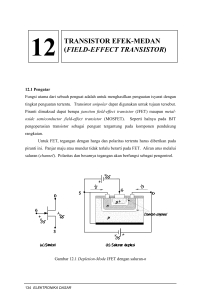

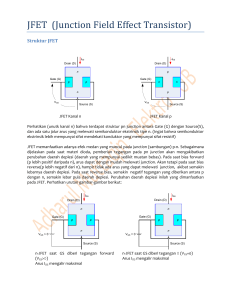

Field Effect Transistor (FET) Oleh Danny Kurnianto,ST.,M.Eng ST3 Telkom Purwokerto A. Transistor BJT vs Transistor FET 1. Transistor BJT adalah devais yg dikendalikan oleh arus, dengan kata lain arus kolektor (Ic) yg merupakan fungsi dari arus basis (Ib). Sedangkan transistor FET adalah devais yg dikendalikan oleh tegangan, dengan kata lain arus (Id) merupakan fungsi dari tegangan VGS yg tercatu pada masukan. Untuk lebih jelasnya, lihat Gambar 1 dibawah ini. Gambar 1. Pengendali pada BJT dan FET 2. BJT merupakan transistor bipolar, artinya bahwa proses konduksi pada transistor ini tergantung pada dua jenis pembawa muatan, yaitu elektron dan hole. Sedangkan FET merupakan transistor unipolar, artinya konduksi tergantung hanya pada salah satu dari elektron (saluran-n) atau hole (saluran-p) 3. Impedansi masukan BJT lebih rendah dari FET, ini berarti impedansi masukan FET tinggi. (impedansi masukan tinggi mrp karakteristik penting dlm desain penguat ac linear) 4. Karena BJT lebih sensitif terhadap perubahan sinyal yg diterapkan, maka penguatan tegangan ac pada penguat BJT lebih besar daripada FET. 5. Secara umum, suhu FET lebih stabil dan kontruksinya lebih kecil daripada BJT. Jenis transistor FET FET JFET Gambar 2. Jenis transistor FET MOSFET B. Kontruksi dan Karakteristik JFET Gambar 3. Kontruksi JFET Transistor JFET terdiri dari 2 jenis, yaitu JFET saluran-n dan JFET saluran-p. Pada Gambar 3 ditunjukkan kontruksi dasar dari JFET saluran-n. Bagian utama dari struktur ini adalah bahan tipe n yang membentuk saluran diantara 2 saluran tipe-p yang ditanamkan. Bagian atas dari saluran tipe-n ini terhubung dengan terminal yg disebut drain (D). Sedangkan bagian bawah terhubung dengan terminal yg disebut source (S). 2 bahan tipe-p dihubungkan bersama membentuk terminal gate (G). Dalam kondisi tanpa bias, maka 2 junction bahan tipe-p dan tipe-n akan membentuk lapisan pengosongan (depletion layer) pada kedua sisi dari bahan tipe-p, seperti yg ditunjukkan pada Gambar 3. Saluran yg terletak diantara 2 lapisan pengosongan inilah yang digunakan elektron bebas untuk bergerak dari source ke drain. Analogi pengontrolan aliran arus elektron pada JFET tipe-n ditunjukkan pada Gambar 4. Gambar 4. analogi pengontrolan aliran elektron pada JFET tipe-n Jika tegangan VGS = 0 maka tegangan VDS bernilai positif Gambar 5. VGS = 0 Mengapa daerah pengosongan (depletion layer) pada bagian atas bahan tipe-p lebih luas dari pada bagian bawahnya? Maka perhatikanlah Gambar 6 dibawah ini Grafik yg menunjukkan hubungan arus drain (ID) dengan tegangan drain-source (VDS) ditunjukkan pada Gambar 7. Gambar 7 Pada daerah dengan nilai-nilai VDS rendah, maka arus drain meningkat secara linear dan hal ini menunjukkan bahwa resistansi saluran-n konstan. Saat VDS meningkat dan mencapai nilai Vp, maka kedua daerah pengosongan (depletion layer) akan melebar dan akan saling bersentuhan dan hal ini menyebabkan lebar saluran-n akan semakin berkurang dan tertutup. Ketika kedua daerah pengosongan saling bersentuhan (saluran-n tertutup) maka kondisi ini disebut dengan pinch-off Tegangan VDS yg menyebabkan kondisi pinchoff disebut dengan tegangan pinch-off dan dinotasikan dengan Vp. Gambar 8. Kondisi pinch-off Sebenarnya, istilah pinch-off ini kurang tepat karena hal ini menunjukkan bahwa arus drain (ID) terjepit dan menurun hingga 0 ampere. Hal ini tidak mungkin terjadi, karena pada kenyataannya masih tetap ada saluran yg sangat kecil yg memungkinkan arus tetap mengalir yg disebut arus saturasi (IDSS). Saat VDS > Vp, maka JFET berfungsi sebagai sumber arus, dimana arus drain (ID) tetap sebesar IDSS. IDSS adalah arus drain (ID) maksimum dan didefinisikan pada kondisi VGS = 0 dan VDS > Vp Kondisi VGS < 0 Tegangan VGS adalah tegangan pengendali pada JFET. Seperti halnya pada transistor BJT, yg mana terdapat grafik IC terhadap VCE dengan nilai IB yg berbeda-beda, maka pada JFET juga terdapat grafik hubungan antara ID dan VDS dengan berbagai nilai VGS seperti yang ditunjukkan pada Gambar 9. Pada JFET tipe saluran-n, tegangan pengendali (VGS) dibuat lebih negatif daripada VGS = 0 V. Dengan kata lain, terminal gate (G) dibuat lebih negatif daripada terminal source (S). Semakin kecil (negatif) tegangan VGS-nya, maka arus drain saturasi (IDSS) juga semakin kecil. Sampai ketika nilai VGS = Vp, dengan nilai Vp adalah negatif untuk tipe saluran-n maka arus saturasi (IDSS)sama dengan nol (0 ampere). Gambar 10. Aplikasi tegangan VGS negatif Resistansi yang dikontrol tegangan Daerah disebelah kiri titip pinch-off disebut sebagai daerah ohmik. Resistansi didaerah ini tergantung dari nilai VGS. Semakin negatif nilai VGS, hal ini akan meningkatkan nilai resistansi. Berikut ini adalah persamaan untuk menentukan besarnya resistansi tersebut ………………….1 ro = resistansi saat VGS = 0 rd = resistansi saat VGS tertentu JFET Tipe Saluran-P Tipe saluran-p dibuat dengan kontruksi sama dengan tipe saluran-n, Cuma bedanya pada kebalikan bahan tipe-p dan tipe-n seperti yang ditunjukkan pada Gambar 11. Gambar 11. JFET saluran-p Arah arus juga terbalik, yaitu arus keluar melalui terminal drain (D) dan masuk melalui terminal source (S) Saluran akan menyempit dengan meningkatnya tegangan positif VGS. Tegangan VDS tercatu dengan tegangan negatif sehingga nilai VDS negatif. Gambar 12 ditunjukkan grafik hubungan antara ID terhadap VDS dengan nilai VGS yg berbeda-beda. Simbol Transistor JFET Pada Gambar 13 ditunjukkan simbol dari transistor JFET. Gambar 13.a) simbol JFET saluran –n . b) simbol JFET saluran-p Kesimpulan Arus maksimum IDSS terjadi saat VGS = 0 Volt dan VDS >= |Vp|. (lihat gambar 14.a) Tegangan VGS yang lebih atau sama dengan tegangan Vp, maka arus drain (ID) sama dengan nol. (ligat gambar 14.b) Untuk semua nilai VGS antara 0 sampai Vp, maka arus ID akan bervariasi antara IDSS sampai 0 ampere. (lihat gambar 14.c) Gambar 14. 3. Karakteristik Transfer Hubungan antara ID dan VGS didefinisikan oleh persamaan Shockley berikut ini: ……….(2) Bentuk kuadratik pada persamaan (2) diatas menunjukkan bahwa hubungan tsb tidak linear, tapi berbentuk eksponensial meningkat dengan menurunnya nilai VGS. Kurva transfer (grafik ID terhadap VGS) dapat diperoleg dari grafik ID terhadap VDS seperti pd Gambar 15 dibawah ini: Gambar 15. Kurva transfer ID terhadap VGS Selain menggunakan grafik pada Gambar 15, maka dapat kita juga langsung menggunakan persamaan Shockley (2) untuk mendapatkan titik-titik pada kurva transfer sebagai berikut. Masukkan nilai VGS = 0, memberikan : Masukkan nilai VGS = Vp , maka didapatkan: Masukkan nilai VGS = - 1 V, maka didapatkan: Dari persamaan (2), kita juga bisa mendapatkan nilai VGS sebagai berikut: …………………(3) Latihan soal : 1. Gambarkan grafik ID terhadap VGS dengan nilai IDSS = 12 mA dan Vp = -6 V. Jawab: Nilai IDSS = 12 mA terjadi saat nilai VGS = 0 dan nilai ID = 0 A saat VGS = Vp. Sekarang, tinggal mencari 2 titik saja agar bisa digambarkan grafik ID terhadap VGS. Misalkan , cari nilai ID saat VGS = 0,5 Vp ? Dan cari nilai VGS saat ID = 0,5 IDSS Hubungan Penting JFET dg BJT