GATE – GATE LOGIKA

advertisement

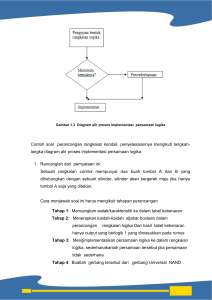

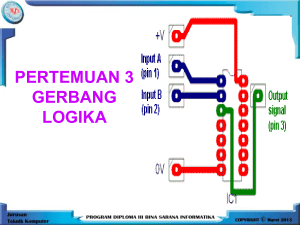

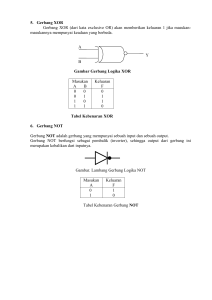

MODUL II GATE – GATE LOGIKA I. Tujuan instruksional khusus 1. Menyelidiki operasi logika dari gate-gate logika 2. Membuktikan dan mengamati oiperasi logika dari gate-gate logika. II. Dasar Teori Gerbang Logika merupakan dasar pembentuk sistem digital. Gerbang Logika beroperasi dengan bilangan biner, karenanya disebut Gerbang Logika Biner. Tegangan yang digunakan dalam gerbang logika adalah High (berarti "1" atau "+5V") atau Low (berarti "0" atau "0 V" ). Semua sistem digital disusun dengan hanya menggunakan tiga gerbang logika dasar: gerbang AND, gerbang OR dan gerbang NOT. Empat gerbang logika lain dapat dibuat dari gerbang-gerbang dasar ini, yakni: gerbang NAND, gerbang NOR, gerbang eksklusif OR, gerbang eksklusif NOR . Gerbang-gerbang logika tersebut disusun dengan menggunakan dioda dan resistor (Diode Logic), dengan menggunakan resistor dan transistor (Resistor Transistor Logic), atau dengan menggunakan kombinasi transistor (TransistorTransistor Logic - TTL). Kelompok logika lain dinamakan berdasar konfigurasi rangkaiannya dan tersedia sebagai suatu IC (Integrated Circuit). Contohnya PMOS (Positive-Metal Oxide Semiconductor), CMOS (Complementary Metal Oxide Semiconductor), ECL (Emitter-Coupled Logic), I2L (Integrated Injection Logic). Yang paling populer adalah keluarga TTL yang dikenal dengan seri 74/54 yang masih terbagi lagi dalam kelompok-kelompok: standar (74/54), High-speed TTL (74H/54H), Low-power TTL (74L/54 L), Schottky TTL (74S/54S), Lowpower Schottky TTL (74LS/54LS). Selain itu juga cukup banyak dipakai keluarga CMOS yang ditandai dengan HC, HCT, AC atau ACT. Umumnya TTL dipilih karena mempertimbangkan kecepatannya, sedang CMOS disukai karena pemakaian dayanya yang relatif rendah. 8 Jika dilihat dari literatur pabrik, kita akan menemukan bahwa gerbang NAND merupakan gerbang yang paling banyak tersedia dan digunakan. Karena itu gerbang NAND sering juga digunakan untuk membangun gerbang-gerbang lain, sehingga disebut gerbang universal. Pada percobaan ini kita akan mengenal gerbang-gerbang logika dasar dengan memanfaatkan gerbang NAND sebagai gerbang universal. Gerbang NOR sebagaimana gerbang NAND juga merupakan gerbang universal. Semua rangkaian logika bagaimanapun kompleksnya dapat dibangun hanya dengan gerbang NAND atau hanya gerbang NOR saja. Operasi logika dari OR gate dapat dinyatakan bahwa output OR gate berlogika 1 apabila satu atau lebih inputnya berlogika ”1”. Atau dengan kata lain bahwa output OR gate berlogika 0 apabila semua inputnya berlogika 0. Untuk OR gate 2 input operasi logikanya ditunjukkan dalam bentuk tabel yang disebut tabel kebenaran (truth table) pada gambar 3(a). Output dari suatu AND gate akan berlogika ”0” apabila salah satu inputnya berlogika ”0”. atau dengan kata lain output AND gate berlogika ”1” hanya apabila semua inputnya berlogika ”1”. Tabel kebenaran dan simbol untuk gate inbi diperlihatkan pada gambar 3b. A B F 0 0 0 A 0 1 1 B 1 0 1 1 1 1 Simbol Logika OR F A B F 0 0 0 A 0 1 0 B 1 0 0 1 1 1 F Simbol Logika AND Tabel Tabel kebenaran kebenaran Gambar 2.1 Simbol logika dan table kebenaran gerbang AND dan OR Berbeda dengan gate yang lain, NOT gate hanya mempunyai 1 input dan 1 output gate ini selalu akan berkebalikan dengan logika inputnya. Apabila inputnya berlogika 1 maka outputnya berlogika 0. Simbol dari tabel kebenaran untuk gate ini diperlihatkan pada gambar 4a. 9 Operasi logika NOR gate sama dengan kebalikan operasi OR gate karena gate ini merupakan kombinasi dari gate dasar NOT dan OR gate oleh karena itu output NOR gate akan berlogika 0 apabila salah satu inputnya berlogika ”1”. Tabel kebenaran dan simbolnya diperlihatkan pada gambar 4b. NAND gate merupakan kombinasi dari NOT dan AND gate. Karena itu operasi NAND gate adalah sama dengan operasi AND gate dan diikuti operasi NOT gate. Jadi dapat dinyatakan bahwa output dari NAND gate akan berlogika ”1” apabila salah satu inputnya berlogika 0. Simbol NAND gate diperlihatkan pada gambar 4c. A B A B F 0 1 0 0 1 A 1 0 0 1 0 B 1 0 0 1 1 0 A B Simbol logika NOT Tabel kebenaran Tabel kebenaran A B F 0 0 1 0 1 1 1 0 1 1 1 0 F Simbol logika NOR A B F Simbol logika NAND Tabel kebenaran Gambar 2.2 Simbol Logika dan table kebenaran gerbang NOT, NOR dan NAND Dua rangkaian logika yang lain adalah EX-OR dan EX-NOR. Kedua gate ini merupakan kombinasi dari gate-gate dasar dan hanya mempunyai dua input. Output EX-OR berlogika 0 apabila kedua inputnya berlogika sama 0 atau 1, atau dengan kata lain output EX-OR gate berlogika 1 apabila kedua inputnya 10 berbeda (gambar 2.3). Oleh karena itu keadaan outputnya dapat ditulis sebagai berikut : F A B A B F 0 0 0 0 1 1 1 0 1 1 1 0 A B F Simbol logika EXOR Tabel kebenaran A B F 0 0 1 0 1 0 1 0 0 1 1 1 A B F Simbol logika EXNOR Tabel kebenaran Gambar 2.3 Simbol logika dan table kebenaran gerbang XOR dan XNOR Operasi logika EX-NOR gate berkebalikan dengan operasi EX-OR gate. Apabila kedua inputnya berlogika berbeda maka outputnya berlogika 0, sebaliknya bila kedua inputnya sama 0 atau 1 maka outputnya berlogika 1, seperti terlihat pada gambar 2.3. III. Daftar alat dan bahan 1. Catu daya 5V : 1 buah 2. Volmeter : 1 buah 3. Modul socket IC : 1 buah 4. Modul LED : 1 buah 5. IC : SN74LS00 : 1 buah SN74LS02 : 1 buah SN74LS04 : 1 buah SN74LS08 : 1 buah SN74LS32 : 1 buah SN74LS86 : 1 buah 6. Kabel penghubung secukupnya. 11 IV. Diagram Rangkaian 5V A B Vo (a) A B A B F F (b) (c) Gambar 2.4 Rangkaian percobaan gate-gate logika V. Keselamatan Kerja 1. Pastikan seluruh hubungan ataupun kabel yang digunakan tidak ada yang terkelupas, terbuka dan tidak longgar. 2. Hubungkan catu daya dengan rangkaian secara benar dan pastikan nilai tegangan yang diatur sesuai dengan spesifikasi kebutuhan rangkaian dan komponen yang digunakan. 3. Perhatikan polaritas tegangan yang digunakan, baik sumber tegangan DC maupun tegangan AC. 4. Pastikan pentanahan telah dilakukan dengan benar. 5. Laporkan kepada instruktur setelah selesai merakit rangkaian untuk diperiksa kembali pengawatan yang telah dilakukan. 6. Atur posisi alat ukur seperti multimeter, osiloskop, dan generator fungsi sesuai dengan skala besaran yang digunakan. 7. Matikan seluruh panel dan sumber tegangan setelah melakukan praktikum. 12 VI. Langkah Kerja 1. Catu daya dalam keadaan mati, buatlah rangkaian seperti diagram rangkaian gambar 2.4a. 2. Bila telah benar laporkan kepada instruktur 3. Hidupkan catu daya 4. Berikan data input sesuai dengan tabel pengamatan dan amati tegangan output Vo dan indikator LED. 5. Ulangi prosedur (1) s/d (4) untuk gate AND, NAND, NOR, NOT, dan EXOR. 6. Buatlah rangkaian seperti diagram rangkaian gambar 2.4b dan 2.4c. 7. Ulangi prosedur (2) s/d (4) dan catat hasilnya pada tabel. 8. Buka rangkaian dan kembalikan peralatan dan komponen. VII. Data Hasil Percobaan Tabel Pengamatan – 2.1 Tabel data hasil percobaan gate-gate logika Tabel kebenaran AND Gate A B 0 Vo(volt) F Tabel kebenaran NOR Gate A B 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Tabel kebenaran NAND Gate A B 0 Vo(volt) F Vo(volt) F Tabel kebenaran OR Gate A B 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Vo(volt) F 13 Tabel untuk gambar 6 (b) A A 0 Vo(volt) Tabel untuk gambar 6 (c) B A B 0 0 0 0 1 0 1 1 0 1 0 1 1 1 1 Vo(volt) F Tabel kebenaran NOT Gate A Vo(volt) B 0 1 VIII. Tugas dan Pertanyaan 1. Tuliskan kode IC yang digunakan dan jelaskan artinya secara singkat! 2. Dari data hasil pengamatan, berapakah tegangan logika rata-rata untuk logika ”0” dan ”1” dari semua gate? 3. Tulislah persamaan output dari gambar-6b dan 6c! 4. Dapatkah suatu NAND gate digunakan sebagai NOT gate?, gambarkan! 5. Berapa jumlah NAND gate 2 input dibutuhkan untuk membuat fungsi OR gate 2 input? gambarkan! 14