3-3-3-1

advertisement

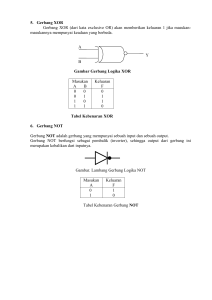

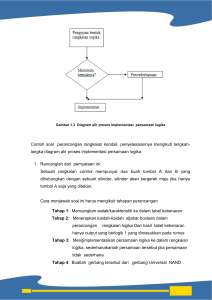

SISTEM DIGITAL CMOS DISUSUN OLEH : KELOMPOK 3 YUSNIAH NIM 161401038 REZEKI DAMAI ARIGA RAWIE NIM 161401041 ADE KURNIA AHMAD NIM 161401044 SULAIMAN NIM 161401047 MUCHLIS SAPUTRA NIM 161401050 HILDA SUCI ARDIANTI NIM 161401053 PRODI S1 ILMU KOMPUTER FAKULTAS ILMU KOMPUTER DAN TEKNOLOGI INFORMASI UNIVERSITAS SUMATERA UTARA 2017 Latar belakang CMOS adalah salah satu rangkaian terintegrasi yang banyak digunakan pada mikroprosesor,pengontrol mikro,RAM statis dan sirkuit digital lainnya.Teknologi CMOS juga digunakan dalam banyak sirkuit analog, seperti sensor gambar, pengubah data, dan trimancar terintegrasi untuk berbagai jenis komunikasi. Frank Wanlassberhasil mematenkan CMOS pada tahun 1967 (Patent US 3,356,858).CMOS juga sering disebutcomplementary-symmetry metal–oxide–semiconductor or COSMOS(semikonduktor–logam–oksida komplementer-simetris). Kata komplementer-simetris merujuk pada kenyataan bahwa biasanyadesain digital berbasis CMOS menggunakan pasangan komplementer dan simetris dari MOSFETsemikonduktor tipe-p dansemikonduktor tipe-n untuk fungsi logika. Perancangan Rangkaian Digital Teknologi IC Digital dan Jenis Rangkaian Logika Gambar 1.Teknologi IC Digital dan Jenis Rangkaian Logika Konsep jenis rangkaian logika artinya: • setiap anggota jenis dibuat dengan teknologi yang sama • mempunyai struktur rangkaian yang serupa • mempunyai ciri-ciri dasar yang sama, Setiap jenis rangkaian logika mempunyai kelebihan dan kekurangan. Pada perancangan sistem yang konvensional, perancang memilih jenis logika yang sesuai dan berusaha untuk mengimplementasikan sistem sebanyak mungkin dengan menggunakan modul dari jenis yang sama. Hal ini memudahkan interkoneksi dari modul Jika dalam suatu sistem digunakan lebih dari satu jenis rangkaian logika, perancang harus merancang rangkaian antarmuka (interface). Pemilihan jenis rangkaian logika berdasarkan: • fleksibilitas logika • kecepatan operasi • ketersediaan fungsi kompleks • kepekaan terhadap derau • kemampuan beroperasi pada selang suhu tertentu • disipasi daya • harga Teknologi IC Digital: • CMOS • Bipolar • BiCMOS • GaAs CMOS Teknologi CMOS adalah yang paling dominan dalam teknologi IC untuk rancangan rangkaian digital. Dibandingkan dengan teknologi bipolar, CMOS mempunyai: • disipasi daya yang kecil, sehingga dapat menempatkan lebih banyak rangkaian pada satu chip • mempunyai impedansi masukan yang tinggi, sehingga dapat digunakan untuk penyimpan sementara dari informasi baik pada rangkaian logika maupun rangkaian memory. • mempunyai ukuran yang semakin kecil, sehingga memungkinkan untuk mempunyai tingkatan integrasi yang sangat tinggi. Yang paling banyak dipakai adalah rangkaian CMOS komplementer yang berdasarkan struktur inverter. Dari segi banyaknya gerbang logika pada satu chip: • SSI (small scale integrated) – 1 – 10 gerbang: • MSI (medium scale integrated) – 10 – 100 gerbang • VLSI (very large scale integrated) – sampai jutaan gerbang Dalam beberapa aplikasi, CMOS komplementer dapat ditunjang oleh dua rangkaian logika MOS lainnya, yaitu pseudo-NMOS dan pass-transistor. CMOS dinamik digunakan jika diperlukan kecepatan operasi yang tinggi dan disipasi daya yang rendah. Bipolar Dua jenis rangkalain logika yang berdasarkan BJT: TTL dan ECL. Sebelum era VLSI, TTL banyak digunakan.Sekarang TTL muncul kembali dengan daya yang rendah dan kecepatan yang tinggi. Kecepatan tinggi diperoleh dengan mencegah BJT memasuki daerah jenuh. Jenis TTL ini menggunakan dioda Schottky, sehingga disebut Schottky TTL. ECL atau CML dibuat berdasarkan implementasi ‘current-switch’ pada inverter. Elemen dasarnya adalah penguat differential. Pada operasi ECL ini, keadaan jenuh selalu dihindari sehingga menghasilkan kecepatan operasi yang tinggi, Dari semua jenis rangkaian logika, ECL mempunyai kecepatan operasi tertinggi, BiCMOS BiCMOS menggabung kecepatan operasi yang tinggi dari BJT dengan disipasi daya yang rendah dan karakteristik lainnya dari CMOS. BiCMOS dapat dipakai untuk implementasi rangkaian analog dan digital dalam chip yang sama. Gallium Arsenide (GaAs) Mobilitas pembawa yang tinggi dari GaAs menghasilkan kecepatan operasi yang tinggi, Teknologi ini belum berkembang dengan matang, tetapi mempunyai potensi yang sangat besar. Karakterisasi Rangkaian Logika • noise margin • propagation delay • power dissipation • delay-power product • silicon area • fan-in dan fan-out Noise Margin Gambar 2. Voltage Transfer Characteristik (VTC) sebuah inverter. Operasi statik dari jenis rangkaian logika ditentukan karakteristiknya oleh karakteristik voltage transfer (VTC) dari inverter dasarnya. Pada VTC terdapat 4 parameter, VOH, VOL, VIH dan VIL. VIH dan VIL didefinisikan sebagai titik di mana arah kemiringan kurva = -1. VM didefinisikan sebagai tegangan ambang di mana vO = vI. VIL adalah harga maksimum sinyal masukan vi yang masih dianggap oleh inverter sebagai logika 0. VIH adalah harga minimum sinyal masukan vi yang masih dianggap oleh inverter sebagai logika 1. VOH adalah harga sinyal keluaran logika 1 VOL adalah harga sinyal keluaran logika 0 Ketahanan (robustness) dari jenis rangkaian logika ditentukan oleh kemampuannya untuk menolak derau yang dinyatakan dengan ‘noise margin’ NMH ≡ VOH – VIH NML ≡ VIL – VOL Sebuah inverter yang ideal mempunyai: NMH = NML = VDD/2 VM = VDD/2 Propagation Delay Kinerja dinamik dari jenis rangkaian logika ditentukan oleh waktu tunda propagasi dari inverter dasarnya. tPLH adalah waktu tunda propagasi dari masukan logika rendah ke keluaran logika tinggi. tPHL adalah waktu tunda propagasi dari masukan logika tinggi ke keluaran logika rendah. tp ≡ ½ (tPLH + tPHL) Makin pendek waktu tunda propagasi, makin tinggi kecepatan operasi jenis rangkaian logika. Power Dissipation Ada dua macam disipasi daya. Disipasi daya statik didefinisikan sebagai daya yang didisipasikan oleh gerbang jika tidak ada proses perubahan (switching). Disipasi daya ini disebabkan oleh adanya hubungan pada rangkaian gerbang ke catu daya dan ground pada saat keluaran tinggi atau rendah. Disipasi daya dinamik didefinisikan sebagai daya yang didisipasikan oleh gerbang jika ada proses perubahan. Hal ini terjadi karena transistor beroperasi dari catu daya VDD dan mengisi kapasitor beban. f = frekuensi PD=1/2fCV2DD Persamaan di atas dturunkan dengan asumsi bahwa keluaran rendah = 0 V dan keluaran tinggi = VDD Gambar 3.Definisi dari waktu tunda propagasi dan waktu perubahan (switching times) dari sebuah inverter Delay-Power Product Idealnya dalam perancangan sebuah rangkaian logika adalah mempunyai kecepatan tinggi tetapi disipasi daya yang rendah. Tetapi kedua persyaratan ini bertentangan, karena jika disipasi daya diturunkan dengan menurunkan catu tegangan atau catu arus, atau keduanya, ‘current-driving capability’ dari gerbang akan menurun. Hal ini disebabkan semakin lama waktu untuk ‘charge’ dan ‘discharge’ pada beban dan kapasitor parasit, sehingga waktu tunda propagasi meningkat. DP = PDtp [joule] Semakin kecil PD, semakin efektif rangkaian logika. Silicon Area Tujuan dari perancangan rangkaian VLSI digital adalah minimisasi luas silikon per gerbang. Hal ini dapat dicapai dengan: • teknologi proses yang canggih sehingga memungkinkan pengurangan ukuran minimum dari divais. • teknik perancangan rangkaian yang canggih. • tata letak chip yang teliti. Semakin sederhana rangkaian, semakin kecil luas silikon yang diperlukan. Dengan memilih divais yang kecil maka akan mengurangi kapasitor parasit sehingga dapat meningkatkan kecepatan. Tetapi, divais kecil mempunyai ‘current driving capability’ yang rendah sehingga waktu tunda meningkat. Jadi di sini diperlukan kompromi antara semua kendala dan keunggulan yang ada untuk mendapatkan perancangan yang optimum. Fan-in dan Fan-out Fan-in sebuah gerbang adalah jumlah masukannya. Fan-out adalah jumlah maksimum dari gerbang serupa yang dapat di ‘drive’oleh gerbang tersebut dengan mempertahankan kualitas yang diinginkan. Teknik Perancangan Sistem Digital - custom design - semi custom design dengan menggunakan gate array. Salah satu jenis gate array yang banyak digunakan adalah field programmable gate array (FPGA) Design Abstraction and Computer Aids Perancangan sistem digital yang sangat kompleks, apakah pada satu chip IC atau menggunakan komponen yang sudah ada dapat dilakukan dengan menggunakan beberapa tingkat abstraksi yang berbeda dengan bantuan bermacam-macam alat bantu komputer. Dalam perancangan IC ada beberapa rangkaian yang sudah tersimpan dalam pustaka yang disebut ‘standard cells’. Rangkaian-rangkaian ini disebut sel, dapat digunakan untuk merancang subsistem yang lebih besar.yang akan ditentukan karakterisasinya dan disimpan sebagai blok fungsional yang kemudian digunakan untuk merancang sistem yang lebih besar lagi, Jadi tingkat abstraksinya: - Standard cell - Functional block - Subsystem atau system Pada setiap tingkat abstraksi perlu dilakukan simulasi dan program komputer lainnya yang dapat membantu perancangan secara otomatis,misal ‘place-and-route’. Sayangnya untuk perancangan sistem analog, banyak hal yang harus dilakukan secara manual. Analisa Perancangan dan Kinerja Inverter CMOS Struktur Rangkaian Gambar 4.(a) Inverter CMOS (b) dinyatakan sebagai sepasang saklar yang bekerja secara bergantian Source dari masing-masing MOSFET dihubungkan dengan body, sehingga menghilangkan ‘body effect’ Vtn = |Vtp| = Vt yang mempunyai harga berkisar antara 0,2 V – 1 V. Inverter dapat digantikan dengan sepasang saklar yang bekerja secara bergantian seperti yang terlihat pada gambar 10(b) W rDSN 1 kn' VDD Vt L n W rDSP 1 k p' VDD Vt L p Operasi Statik vI = 0, vO = VOH = VDD → simpul keluaran terhubung ke VDD melalui resistansi rDSP dari transistor ‘pull-up’ QP. vI = VDD, vO = VOL= 0 → simpul keluaran terhubung ke ground melalui resistansi rDSN dari transistor ‘pull-down’ QN. Jadi dalam keadaan ‘steady state’, tidak ada jalur arus antara VDD dan ground, dan arus statik dan disipasi daya statik sama dengan nol. Gambar 5. VTC dari inverter CMOS dengan QN dan QP yang ‘matched’ Pada gambar 5 terlihat bahwa keluaran dari inverter CMOS adalah 0 dan VDD. Jadi simpangan tegangan keluaran merupakan simpangan maksimum. Ternyata VOL dan VOH tidak tergantung dari ukuran divais, sehingga CMOS sangat berbeda dengan bentuk logika MOS lainnya Inverter CMOS dapat dibuat agar perpindahan kondisi (switched) terjadi pada titik tengah dari simpangan logika yaitu VDD/2 dengan memilih ukuran transistor yang tepat. Tegangan ambang perpindahan adalah: Vth VDD Vtp k n k p Vtn 1 kn k p k n k n' W L n k p k p' W L p Untuk kasus khusus dimana Vtn = |Vtp|, Vth = VDD/2 untuk kn = kp yaitu:pada keadaan: kn' W Ln k p' W Lp Jadi VTC yang simetris dapat diperoleh jika divais dirancang mempunyai parameter transkonduktansi yang sama. Kondisi ini disebut ‘matching’. Karena μn. 2 – 4 kali lebih besar dari μp, maka keadaan ‘matching’ dapat diperoleh dengan membuat (W/L)p 2 – 4 kali (W/L) W W n L p p L n Biasanya kedua divais mempunyai panjang kanal yang sama yaitu di-set pada panjang minimum. Lebar minimum untuk kanal –n biasanya 1½ - 2 kali panjang minimum dan untuk kanal –p 3 – 4 kali panjang minimum. Jika inverter harus men-drive beban kapasitif yang besar, transistor dibuat lebih lebar. Tetapi untuk menghemat area chip, sebagian besar inverter dibuat dengan ukuran minimum. Untuk selanjutnya (W/L) minimum untuk transistor NMOS disebut n dan (W/L) minimum untuk transistor PMOS disebut p. Luas inverter dapat dinyatakan dengan WnLn + WpLp = (Wn + Wp)L, maka luas minimum inverter adalah (n+p)L2, maka (n+p) dapat digunakan ‘proxy’ luas. Contoh: n = 1,5 dan p = 4,5 maka faktor luas = n+p = 6 Dengan menempatkan tegangan ambang pada tengah simpangan, matching parameter transkonduktansi QN dan QP akan memberikan: n - Kemampuan ‘current- driving’ yang sama pada ke dua arah (pull-up dan pull-down). - rDSN = rDSP - tPLH = tPHL - NMH = NML = ⅜(VDD + ⅔Vt) - Biasanya Vt = 0,1 sampai 0,2 VDD, ‘noise margin’ ≈ 0,4 VDD - Harga ini membuat inverter CMOS hampir ideal dilihat dari sisi kekebalan derau. - Hal lain, karena arus dc masukan inverter sama dengan nol, noise margin tidak tergantung dari fan-out gerbang. - Jika kn > kp → Vth lebih dekat ke nol. - Jika kp > kn → Vth lebih dekat ke VDD. - Kemiringan VTC inverter pada daerah transisi adalah g mN g nP roN // roP Operasi Dinamik Pada gambar 6, kita akan menganalisa waktu tunda propagasi dari inverter yang terdiri dari Q1 dan Q2 yang di’drive’ oleh sumber vI yang berimpedansi rendah dan mempunyai beban inverter yang terdiri dari Q3 dan Q4. Pada gambar 6 terlihat kapasitansi internal dari transistor yang terhubung pada simpul keluaran inverter (Q1, Q2).. Gambar 6. Rangkaian untuk menganalisa waktu tunda propagasi dari inverter Q1 dan Q2 yang men-drive inverter Q3 dan Q4. Perhatikan konstribusi masing-masing kapasitansi pada gambar 6 pada harga kapasitansi beban ekivalen C • Kapasistansi overlap gate-drain dari Q1 dan Q2, Cgd1 dan Cgd2. Kedua kapasitansi ini dapat diganti dengan kapasitansi ekivalen antara simpul keluaran dengan ground yaitu 2Cgd1 dan 2Cgd2. • Kapasitansi antara body dan drain, Cdb1 dan Cdb2. Kedua kapasitansi ini dapat digantikan dengan kapasitansi ekivalen antara simpul keluaran dan ground. • Karena inverter kedua sebagai beban, kapasitansi masukan dari Q3 dan C4 tetap konstan dan sama dengan kapasitansi total dari gate (WLCox + Cgsov + Cgdov). Jadi kapasitansi masukan dari inverter beban: • Komponen terakhir dari C adalah kapasitansi kawat Cw. Jadi harga total C adalah: C g 3 C g 4 WL 3 Cox WL 4 Cox C gsov3 C gbov3 C gsov4 C gbov4 C 2C gd1 2C gd 2 Cdb1 Cdb2 C g 3 C g 4 Cw Gunakan gambar 7 untuk menentukan tPHL dan tPLH. Perhatikan gambar 7(a) di mana vI menuju VDD dan QN mengosongkan C dari nilai awalnya VDD ke nilai akhir 0. Dari analisa sebelumnya didapatkan: t PHL 1,6C k W L n VDD ' n Dengan asumsi Vt ≈ 0,2 VDD. Cara lain untuk menganalisa rangkaian pada gambar 7(a) yaitu dengan menghitung harga rata-rata dari arus pengosongan iDN selama selang t= 0 sampai t = tPHL. Gambar 7. Rangkaian ekivalen untuk menentukan waktu tunda propagasi (a) t\PHL dan (b) tPLH dari sebuah inverter. Pada t = 0, QN akan jenuh, dan iDN(0) adalah: W 2 iDN 0 12 kn' VDD Vt L n Pada t = tPHL , QN akan berada pada daerah trioda, dan iDN(tPHL) adalah: 2 VDD 1 VDD W iDN t PHL k VDD Vt 2 2 L n 2 ' n Harga rata-rata arus pengosongan: iDN av t PHL 1 2 iDN 0 iDN t PHL CV CVDD 2 iDN av iDN av Vt 0,2VDD 1,7C W k n' VDD Harga ini mendekati harga hasil perhitungan sebelumnya. L n t PHL Dengan cara yang sama dapat diperoleh tPLH: Waktu tunda propagasi adalah nilai rata-rata dari tPHL dan tPLH t PHL 1,7C W kn' VDD L n tp 1 2 t PHL t PLH Dari persamaan-persamaan di atas memungkinkan kita untuk membuat beberapa kesimpulan: 1. Kedua komponen tp dapat mempunyai harga yang sama dengan membuat kedua transistor ‘matched’ 2. Karena tp sebanding dengan C, perancang harus mengurangi C dengan cara memakai panjang kanal minimum dan meminimalkan kawat dan kapasitansi parasitik lainnya dengan membuat tata letak yang optimal. 3. Dengan menggunakan teknologi proses yang mempunyai parameter transkonduktansi k’ yang lebih besar dapat mengurangi waktu tunda propagasi, tetapi hal ini akan menaikkan Cox yang berarti akan menaikkan harga C. 4. Dengan menggunakan (W/L) yang lebih besar dapat mengurangi tp, tapi cara ini akan meningkatkan harga C. Cara ini hanya efektif kalau komponen C yang dominan tidak berkaitan langsung dengan ukuran divais ‘driving’. 5. Menggunakan catu tegangan VDD yang lebih tinggi, tetapi VDD ditentukan oleh teknologi yang digunakan, Disipasi daya dinamik PD = f C VDD Rangkaian Gerbang Logika CMOS Gambar 8. Representasi gerbang logika CMOS 3 masukan. PUN terdiri dari transistor PMOS dan PDN terdiri dari transistor NMOS Gerbang logika CMOS terdiri dari dua rangkaian: rangkaian pull-down (PDN) yang terdiri dari transistor NMOS dan rangkaian pull-up yang terdiri dari transistor PMOS. Kedua rangkaian ini beroperasi dengan variabel masukan yang sifatnya komplementer. Pada gambar 8 terlihat gerbang dengan 3 masukan. PDN akan terhubung (‘conduct’) untuk semua kombinasi ketiga masukan yang memerlukan keluaran ‘rendah’ (Y = 0) dan akan menarik simpul keluaran menuju ground, sehingga pada keluaran tampak vY = 0. Pada saat yang sama PUN akan ‘off’ dan tidak ada jalur dari VDD ke ground. Sebaliknya, semua masukan yang memerlukan keluaran ‘tinggi’ (Y = 1) akan menyebabkan PUN terhubung (‘conduct’), dan PUN akan menarik simpul keluaran ke VDD, sehingga vY = VDD. Pada saat yang sama PDN akan ‘off’ dan tidak ada jalur dari VDD ke ground. PDN terdiri dari NMOS dan NMOS ‘conduct’ jika sinyal masukan pada gate-nya ‘tinggi’. Jadi PDN ‘aktif’ jika masukannya ‘tinggi’. Sebaliknya PUN terdiri dari PMOS dan PMOS ‘conduct’ jika sinyal masukan pada gate-nya ‘rendah’. Jadi PUN aktif jika masukannya ‘rendah. PUN dan PDN menggunakan divais secara paralel untuk membentuk fungsi ‘OR’ dan menggunakan divais secara seri untuk membentuk fungsi ‘AND’. Contoh PDN dapat terlihat pada gambar 9. Gambar 9. Contoh rangkaian ‘pull-down’ (PDN) Pada gambar 9(a), QA akan ‘conduct’ jika A ‘tinggi’ (vA = VDD) dan rangkaian akan menarik simpul keluaran ke ‘ground’ (vY = 0, Y = 0). Sama halnya QB ‘conduct’ dan ,menarik simpul Y ke ground jika B ‘tinggi’. Jadi Y akan rendah jika A atau B ‘tinggi’ Y A B Y A B PDN pada gambar 9(b) akan ‘conduct’ hanya kalau A dan B ‘tinggi’ pada saat bersamaan. Jadi Y ‘low’ jika A dan B ‘tinggi’ Y AB Y AB PDN pada gambar 9(c) akan ‘conduct’ dan menyebabkan Y = 0 jika A ‘tinggi’ atau jika B dan C keduanya ‘tinggi’. Jadi Y A BC Y A BC Gambar 10 Contoh rangkaian ‘pull-up’ (PUN) PUN pada gambar 10(a) akan ‘conduct’ dan menghasilkan keluaran ‘tinggi’ (vY = VDD, Y = 1) jika A ‘rendah’ atau B ‘rendah’, jadi Y A B PUN pada gambar 10(b) akan ‘conduct’ dan menghasilkan keluaran ‘tinggi’ (vY = VDD, Y = 1) jika A dan B kedua ‘rendah’, jadi Y AB PUN pada gambar 10(c) akan ‘conduct’ dan menghasilkan keluaran ‘tinggi’ (vY = VDD, Y = 1) jika A ‘rendah’ atau B dan C kedua ‘rendah’, jadi Y A BC Simbol rangkaian untuk transistor MOS yang biasa dipakai oleh perancang rangkaian digital. Gambar 11 menunjukkan simbol yang biasa dipakai (sebelah kiri) dan simbol yang dipakai pada rangkaian digital (sebelah kanan). Gambar 11. Simbol dari MOSFET Simbol transistor PMOS dengan lingkaran kecil pada terminal gate menunjukkan bahwa gate harus ‘rendah’ untuk menbuat divais aktif. Jadi dalam istilah digital transistor PMOS adalah ‘active low’ Pada simbol untuk rangkaian digital, tidak ada indikasi dari terminal divais, yang mana terminal source dan yang mana terminal drain. Untuk memudahkannya, untuk transistor NMOS, terminal drain mempunyai tegangan yang lebih tinggi, dan untuk transistor PMOS, terminal source mempunyai tegangan yang lebih tinggi. Gerbang NOR dua masukan Y A B AB Gambar 12. Gerbang NOR dua masukan CMOS Y ‘rendah’, jika A ‘tinggi’ atau B ‘tinggi’. Jadi PDN terdiri dari dua transistor NMOS terhubung paralel dengan A dan B sebagai masukannya. Untuk PUN, Y ‘tinggi’ jika A dan B ‘rendah’. Jadi PUN terdiri dari dua transistor PMOS yang terhubung seri dengan A dan B sebagai masukannya. Gambar 12 adalah gerbang NOR yang merupakan gabungan PUN dan PDN Gerbang NAND dua masukan Y AB A B Gambar 13. Gerbang NAND dua masukan CMOS Y ‘rendah’, jika A dan B ‘tinggi’. Jadi PDN terdiri dari dua transistor NMOS terhubung seri dengan A dan B sebagai masukannya. Untuk PUN, Y ‘tinggi’ jika A ‘rendah’ atau B ‘rendah’. Jadi PUN terdiri dari dua transistor PMOS yang terhubung paralel dengan A dan B sebagai masukannya. Gambar 13 adalah gerbang NAND yang merupakan gabungan PUN dan PDN Y AB CD Gerbang Kompleks Y AB CD Untuk mendapatkan PDN, perhatikan Y akan ‘rendah’ jika A ‘tinggi’ dan B ‘tinggi’ atau C dan D kedua-duanya ‘tinggi’. Untuk mendapatkan PUN, nyatakan Y dalam variabel komplemennya dengan menggunakan hukum DeMorgan Y AB CD A B CD A BCD A B C D Y akan ‘tinggi’ jika A ‘rendah’ atau B ‘rendah’ dan C ‘rendah’ atau D ‘rendah’. Rangkaian fungsi ini terlihat pada gambar 14 Gambar 14. Realisasi CMOS dari sebuah fungsi kompleks Mendapatkan PUN dari PDN dan sebaliknya. Dari rangkaian gerbang CMOS (seperti pada gambar 14), ternyata PDN dan PUN adalah rangkaian dual: dimana hubungan seri terdapat pada satu rangkaian, hubungan paralel terdapat pada rangkaian lainnya. Jadi, kita bisa mendapatkan satu rangkaian dari rangkaian lainnya. Proses ini akan lebih sederhana jika dibandingkan dengan mensintesa masing-masing rangkaian secara terpisah dari ekspresi Boolean-nya. Contohnya pada rangkaian pada gambar 14. Kita dengan mudah mendapatkan PDN, karena kita sudah mempunyai Y’ dengan masukan yang tidak dikomplemenkan. Sebaliknya untuk mendapatkan PUN, kita harus memanipulasi fungsi Boolean yang diberikan dengan untuk menyatakan Y sebagai fungsi dari komplemen masukannya. Cara lain: kita dapat memakai sifat ‘duality’ untuk mendapatkan PUN dari PDN. Fungsi Exclusive-OR Y AB AB Karena yang diberikan adalah fungsi Y, maka lebih mudah untuk mensintesa PUN. Tetapi Y bukan dari variabel komplemen saja, maka diperlukan inverter. Dari persamaan di atas diperoleh PUN seperti yang terlihat pada gambar 15(a). Dalam hal ini diperlukan dua buah inverter untuk menghasilkan variabel komplemen. Untuk PDN gunakan hukum DeMorgan untuk mendapatkan Y’. Y A B AB A B AB A B A B AB A B Realisasi fungsi XOR dengan CMOS memerlukan 12 transistor, seperti yang terlihat pada gambar 15(b). Catatan: rangkaian XOR bukan rangkaian dual Gambar 15. Realisasi fungsii XOR dengan CMOS (Inverter tidak disertakan) Ringkasan dari Metoda Sintesa: 1. Hampir semua PDN dapat disintesa langsung dari ekspresi Y’ sebagai fungsi dari variabel non-komplemen. Jika ada variabel komplemen muncul pada ekspresi ini, maka diperlukan tambahan inverter. 2. Hampir semua PUN dapat disintesa langsung dari ekspresi ’ sebagai fungsi dari variabel komplemen.and memasangkan variabel non komplemen pada gate dari transistor PMOS. Jika ada variabel non komplemen muncul pada ekspresi ini, maka diperlukan tambahan inverter. 3. PDN dapat diperoleh dari PUN (dan sebaliknya) dengan menggunakan sifat dualiti Ukuran Transistor Pemilihan ukuran transistor (W/L) mempunyai tujuan agar gerbang mempunyai kemampuan ‘current-driving’ pada kedua arah yang sama dengan kemampuan ‘current-driving’ dari inverter dasar. (W/L)n = n dan (W/L)p = p, dimana n biasanya 1,5 – 2, dan supaya ‘matched’, p = (μn/μp)n. Jadi kita ingin memilih W/L semua transistor pada sebuah gerbang logika sehingga PDN dapat mempunyai arus pengosongan kapasitor yang sama dengan arus pengosongan kapasitor dari sebuah transistor NMOS dengan W/L = n, dan PUN dapat mempunyai arus pengisian kapasitor yang sama dengan arus pengisian kapasitor dari sebuah transistor PMOS dengan W/L = p. Syarat ini akan menjamin waktu tunda gerbang pada kasus terburuk sama dengan waktu tunda sebuah inverter. Kasus terburuk artinya dalam memilih ukuran transistor, harus dicari kombinasi masukan yang menghasilkan arus keluaran yang terendah, kemudian pilih ukuran transistor yang akan membuat besaran arus ini sama dengan arus dari sebuah inverter dasar. Untuk menentukan kemampuan ‘current-driving’ dari sebuah rangkaian yang terdiri dari beberapa divais MOS, perlu dicari W/L ekivalen dari rangkaian transistor MOS. Penentuan W/L ekivalen berdasarkan pada resistansi sebuah MOSFET yang berbanding terbalik dengan W/L. Jika beberapa MOSFET mempunyai (W/L)1, (W/L)2, …. dihubungkan seri, maka resistansi ekivalen adalah jumlah dari masing-masing resistansi Rseri rDS1 rDS 2 ... konstanta konstanta ... W/L 1 W/L 2 1 1 konstanta ... W / L 1 W / L 2 konstanta W/L ek (W/L)ek untuk transistor yang dihubungkan secara seri: W / L ek 1 1 1 ... W / L 1 W / L 2 (W/L)ek untuk transistor yang dihubungkan secara paralel: W / Lek W / L1 W / L2 ... Contoh: 2 transistor MOS yang identik dengan masing-masing (W/L) = 4, akan menghasilkan (W/L) = 2 jika dihubungkan seri dan mempunyai (W/L) = 8 jika dihubungkan paralel. Gambar 16. Ukuran transistor untuk gerbang NOR empat masukan Gambar 17. Ukuran transistor untuk gerbang NAND empat masukan Karena p biasanya 2 – 3 kali lebih besar dari n maka gerbang NOR memerlukan area yang lebih besar dari NAND. Itulah sebabnya gerbang NAND lebih disukai dalam implementasi sebuah fungsi logika kombinasional dengan menggunakan teknologi CMOS Pengaruh Fan-In dan Fan-Out pada Waktu Tunda Propagasi Pada CMOS, setiap variabel masukan memerlukan 2 transistor, NMOS dan PMOS. Penambahan transistor menyebabkan: - penambahan area yang digunakan - penambahan kapasitansi efektif setiap gerbang → kenaikan waktu tunda propagasi. Waktu tunda propagasi juga akan bertambah dengan meningkatnya jumlah masukan dan meningkatnya ukuran divais karena akan meningkatkan C. Oleh karena itu jumlah variabel masukan harus dibatasi maksimum 4. Kenaikan jumlah keluaran juga akan meningkatkan waktu tunda propagasi karena akan meningkatkan kapasitansi beban. Rangkaian Logika Pseudo-NMOS Inverter Pseudo-NMOS Gambar 19 (a). Inverter Logika Pseudo –NMOS (b) Inverter NMOS dengan beban MOS enchancement (c) Inverter NMOS dengan beban MOS depletion Rangkaian inverter pada gambar 19(a) terdiri dari sebuah transistor pengendali QN dan sebuah transistor beban (QP); itulah sebabnya disebut pseudo-NMOS. Gambar 19(b) dan (c) menunjukkan inverter NMOS versi terdahulu, yang terdiri dari transistor pengendali Q1 dan transistor beban Q2, di mana beban adalah (b) MOSFET kanal –n ‘enchancement’ dan (c) MOSFET kanal –n depletion. Ternyata inverter NMOS dengan menggunakan MOSFET enchancement sebagai beban mempunyai beberapa kelemahan yaitu simpangan logika yang kecil, noise margin yang kecil,dan disipasi daya statik yang tinggi. Untuk inverter NMOS dengan menggunakan MOSFET depletion sebagai beban mempunyai kelemahan yaitu body effect pada transistor depletion menyebabkan karakteristik i – v nya bergeser cukup banyak dari karakteristik sumber arus konstan. Walaupun demikian rangkaian ini memperbaiki kelemahan-kelemahan pada rangkaian inverter NMOS yang menggunakan MOSFET enchancement sebagai beban. Karakteristik Statik: Untuk QN: W iDN k n' vI Vtn vO 12 vO2 L n W 2 iDN 12 k n' vI Vtn L n Untuk QP: untuk vO vI Vtn untuk vO vI Vtn W 2 iDP k p' VDD vI Vtp VDD vO 12 VDD vO L p untuk vO vI Vtp W iDP 12 k p' VDD vI Vtp L p 2 untuk vO vI Vtp Untuk mendapatkan VTC, kita tumpangkan kurva beban (transistor QP) pada karakteristik iDN – vDS dari QN, yang dalam hal ini ditulis iDN – vO. Pada gambar 20 hanya ada kurva karakteristik iDN –vO dari QN untuk vGS = vI = 0 dan vI = VDD. Gambar 20. Konstruksi grafik untuk menentukan VTC dari inverter pada gambar 19 Perhatikan: 1. Kurva beban menunjukkan arus jenuh yang rendah daripada yang ditunjukkan oleh kurva untuk QN, terutama untuk vI = VDD. Ini disebabkan pada perancangan inverter pseudo-NMOS, kn lebih besar dari kp dengan faktor 4 – 10. Inverter ini disebut ‘ratioed type’ dan ratio r ≡ kn/kp menentukan semua titik penting pada VTC, VOL, VIL, VOH dan sebagainya sehingga menentukan noise margin. Dengan r yang tinggi, mengurangi VOL dan melebarkan noise margin. 2. Walaupun ada yang menganggap Qp sebagai sumber arus yang konstan, sebenarnya transistor ini bekerja pada keadaan jenuh hanya pada selang vO yang kecil yaitu vO < vI, sedangkan pada selang yang lain, QP bekerja pada daerah trioda. Ketika vI = 0, QN ‘off’, QP bekerja pada daerah trioda. → arus = 0; tegangan drain-source = 0 (titik A) dimana vO = VOH = VDD, arus statik = 0, disipasi daya statik = 0. Ketika vI = VDD inverter bekerja pada titik E, VOL ≠ 0. Kelemahan: 1. vOL ≠ 0. 2. Gate melalukan arus (Isat) pada keluaran rendah sehingga akan ada disipasi daya statik (PD = Isat x VDD Gambar 21. VTC untuk inverter pseudo-NMOS Daerah Operasi Inverter Pseudo-NMOS Daerah Operasi Inverter Pseudo-NMOSv Daerah I (segmen AB): vO = VOH = VDD Daerah II (segmen BC): iDN ( jenuh) iDP ( trioda) 1 2 k n vI Vt 12 k p VDD Vt VDD vO 12 VDD vO 2 2 k n rk p vO Vt VDD Vt 2 r vI Vt 2 Harga VIL dapat diperoleh dengan men-deferensiasikan persamaan di atas dan gantilah vO vI 1 dan vI VIL VDD Vt r r 1 VIL Vt Tegangan ambang VM didefinisikan harga vI untuk vO = vI VM Vt VDD Vt r 1 Titik C dapat diperoleh dengan menggantikan vO = vI – Vt Daerah III (segmen CD): iDN ( trioda) IiDP ( jenuh) vO = Vt 1 2 Daerah IV (segmen DE): k n vI Vt vO 12 vO 12 k p VDD Vt 2 2 k n rk p vO vi Vt v Vt 2 1 VDD Vt 2 r Harga VIH dapat diperoleh dengan men-deferensiasikan persamaan di atas dan gantilah vO vI 1 dan vI VIH VIH Vt VOL dapat dihitung dengan menggantikan vI = VDD 2 VDD Vt 3r 1 VOL VDD Vt 1 1 r Arus statik yang mengalir pada inverter ketika keluaran ‘rendah’ adalah I sat 12 k p VDD Vt 2 Dari persamaan-persamaan di atas dapat diperoleh NML dan NMH. 1 1 NM L Vt VDD Vt 1 1 r r r 1 2 NM H VDD Vt 1 3r Operasi Dinamik Analisa respons transient dari inverter untuk menentukan tPLH dengan cara memberi beban C pada inverter sama dengan analisa pada inverter CMOS komplementer. Kapasitansi akan diisi dengan arus iDP; kita dapat menentukan harga estimasi tPLH dengan menggunakan harga rata-rata dari iDP pada vO = 0 sampai vO = VDD/2. Hasilnya adalah sebagai berikut (dengan asumsi Vt ≈ 0,2VDD): t PLH 1,7C k pVDD Pada saat kapasitor dikosongkan keadaannya agak berbeda karena, iDN harus dikurangi dengan iDP untuk menentukan arus pengosongan. Hasilnya adalah: t PLH 1,7C 0,46 k n 1 VDD r Untuk harga r yang besar: t PLH 1,7C k nVDD Walaupun harga-harga ini sama dengan harga-harga pada inverter CMOS komplementer, inverter pseudoNMOS mempunyai masalah tersendiri. Karena kp r kali lebih kecil kp, tPLH akan r kali lebih besar dari tPHL. Jadi rangkaian akan mempunyai waktu tunda yang tidak simetris. Untuk gerbang yang dengan fan-in yang besar, pseudo-NMOS memerlukan jumlah transistor yang lebih kecil, sehingga C dapat lebih kecil daripada gerbang yang sama yang menggunakan CMOS komplementer. Perancangan Perancangan berarti pemilihan ratio r dan W/L salah satu transistor. Harga W/L dari transistor lainnya dapat diperoleh dengan menggunakan r. Parameter perancangan yang harus diperhatikan: VOL, NML, NMH, Isat,PD, tPLH dan tPHL. Hal-hal penting yang harus diperhatikan pada perancangan adalah sebagai berikut: 1. Harga ratio r menentukan semua titik penting pada VTC: makin besar r, makin kecil VOL dan makin lebar noise margin. Tetapi makin besar r akan meningkatkan ketidaksemetrian respons dinamik. Juga ratio r yang besar akan menyebabkan ukuran transistor lebih besar. Jadi pemilihan r merupakan kompromi antara noise margin dengan luas silikon dan tp. Biasanya r berkisar antara 4 – 10. 2. Setelah r dipilih, harga (W/L)n dan harga (W/L)p dapat ditentukan. Kita dapat memilih (W/L)n yang kecil untuk menjaga luas gerbang yang kecil sehingga mendapatkan harga C yang kecil, Dengan (W/L)n yang kecil menjaga Isat dan PD yang kecil. Di sisi lain dengan memilih (W/L) yang lebih besar diperoleh tp yang rendah sehingga mendapatkan respons yang cepat. Untuk aplikasi kecepatan tinggi, (W/L)p dipilih sedemikan sehingga Isat berkisar 50 – 100 μA, dan untuk VDD = 5 V menghasilkan PD berkisar 0,25 mW – 0,5 mW. Rangkaian gerbang. Selain divais beban, rangkaian grbang pseudo-NMOS identik dengan PDN pada gerbang CMOS komplementer. Rangkaian gerbang 4-masukan NOR dan NAND pseudo-NMOS dapat dilihat pada gambar 22. Setiap gerbang memerlukan hanya 5 transistor, dibandingkan transistor pada CMOS komplementer. Pada pseudo-NMOS, gerbang NOR lebih disukai daripada gerbang NAND, karena pada NOR tidak menggunakan transistor yang dihubungkan secara seri, sehingga dapat dirancang cengan luas yang minimum untuk divais NMOS. Gambar 22. Gerbang NOR dan NAND jenis pseudo-NMOS Pseudo-NMOS cocok digunakan untuk aplikasi yang mempunyai keluaran tinggi hampir setiap saat. Pada aplikasi yang demikian, disipasi daya statik akan rendah. Transisi keluaran dari tinggi ke rendah, waktu tundanya dapat dibuat kecil. Aplikasi jenis ini dapat didapat dalam perancangan ‘address decoder’ untuk ‘memory chip’ dan pada read-only memories (ROM).. Rangkaian Logika Pass Transistor Gambar 23. Gerbang logika pass-transistor (a) Dua saklar yang dikendalikan oleh variabel masukan B dan C yang dihubungkan secara seri pada jalur antara simpul masukan di mana variabel masukan A dipasangkan dan simpul keluaran yang mempunyai fungsi Y=ABC. (b) Dua saklar yang dihubungkan secara paralel, sehingga mempunyai fungsi keluaran Y= A(B+C) (c) Untuk mengimplementasikan fungsi logika dengan menggunakan kombinasi seri dan paralel dari saklar yang dikendalikan oleh variabel masukan logika untuk menghubungkan simpul masukan dan keluaran. (lihat gambar 23) Gambar 24. Dua kemungkinan implementasi dari sebuah saklar yang dikendalikan oleh tegangan yang menghubungkan simpul A dan Y. (a) Transistor NMOS (b) gerbang transmisi CMOS. (c) Setiap saklar dapat diimplementasikan dengan sebuah transistor NMOS atau oleh sepasang transistor MOS komplementer yang dihubungkan dalam konfigurasi gerbang transmisi CMOS.(CMOS transmission gate) (lihat gambar 24b) (d) Konfigurasi ini menggunakan transistor MOS secara seri dari jalur masukan ke keluaran, untuk melalukan atau menghalangi transmisi sinyal. Konfigurasi ini disebut ‘pass-transistor logic’ (PTL) (e) Syarat penting dalam perancangan. (f) Syarat penting dalam perancangan rangkaian PTL adalah memastikan bahwa setiap simpul rangkaian pada setiap saat mempunyai jalur beresistansi rendah ke VDD atau ke ground. (g) Gambar 25. (a) Pada saat B ‘rendah’ dan S1 terbuka tidak ada jalur beresistansi rendah ke ground atau ke VDD. (b) jalur ini tersedia dengan memberikan saklar S2 Pada gambar 25(a), saklar S1 dipakai untuk membuat fungsi AND dari variabel pengendali B dan variabel A yang terdapat pada keluaran inverter CMOS. Keluaran Y dari rangkaian PTL dihubungkan ke masukan inverter lainnya, Jika B ‘tinggi’, S1 tertutup dan Y = A. Simpul Y akan terhubung ke VDD (jika A ‘tinggi’) melalui Q2 atau ke ground (jika A ‘rendah’) melalui Q1. Jika B ‘rendah’ dan S1 terbuka, Y menjadi simpul dengan impedansi tinggi (high-impedance node). Jika pada mulanya vY = 0, simpul ini akan tetap bertegangan nol. Tetapi jika pada mulanya vY = VDD, tegangan ini akan dipertahankan dengan isi pada kapasitor parasitik C, hanya untuk sesaat saja. Karena ada arus bocor, kapasitor C akan dikosongkan dan vY akan berkurang. Jadi rangkaian tidak dapat lagi dianggap sebagai rangkaian logika kombinasional statik. Masalah ini dapat diselesaikan dengan membuat jalur beresistansi rendah pada simpul Y ketika B ‘rendah’ seperti pada gambar 25(b). Di sini saklar S2 yang dikendalikan oleh dihubungkan antara simpul Y dan ground. Jika B ‘rendah’, S2 menutup dan membuat jalur beresistansi rendah antara Y dan ground. Operasi dengan transistor NMOS sebagai saklar. Implementasi saklar pada rangkaian PTL dengan transistor NMOS menghasilkan rangkaian yang sederhana dengan area yang kecil dan kapasitansi simpul yang kecil. Keunggulan ini didapat dengan adanya kekurangan baik dalam karakteristik statik maupun kinerja dinamik dari rangkaian. Pada gambar 26, transistor NMOS Q dipakai untuk mengimplementasikan sebuah saklar menghubungkan simpul masukan dengan tegangan vI dan simpul keluaran. Kapasitansi total antara simpul keluaran dan ground dinyatakan dengan kapasitor C. Saklar digambarkan dalam keadaan tertutup dengan sinyal kendali yang dipasangkan pada gate = VDD. Kita akan menganalisa cara kerja rangkaian pada saat tegangan masukan vI menuju VDD pada t = 0. Asumsikan tegangan mula pada simpul keluaran vO = 0 dan kapasitor C terisi penuh. Ketika vI menuju ‘tinggi’, transistor bekerja pada mode jenuh dan mengalirkan arus iD untuk mengisi kapasitor. iD 12 k n VDD vO Vt 2 k n k n' W L Vt ditentukan oleh body effect karena source mempunyai tegangan vO relatif ke body Vt Vt 0 vO 2 f 2 f Jadi, pada mulanya (t = 0), Vt = Vt0 dan arus iD secara relatif besar. Tetapi, dengan C terisi dan vO meningkat, Vt meningkat dan iD menurun. Penurunan iD disebabkan oleh kenaikan vO dan Vt. Akibatnya proses pengisian kapasitor akan lebih lambat. Dan iD akan turun menjadi nol ketika vO mencapai (VDD –Vt). Jadi tegangan keluaran ‘tinggi’ VOH ≠ VDD tetapi akan lebih rendah sebesar vt. Dan yang akan memperburuk keadaan, vt dapat mempunyai harga 1,5 – 2 kali vt0. Sebagai tambahan untuk mengurangi kepekaan gerbang terhadap derau, harga VOH yang rendah (biasa disebut ‘poor 1’) mempunyai efek yang merusak. Perhatikan apa yang terjadi bila simpul keluaran dihubungkan ke masukan inverter CMOS komplementer (lihat gambar 39). Harga VOH yang rendah akan menyebabkan QP pada inverter beban akan terhubung. Jadi inverter mempunyai arus statik dan disipasi daya statik. Waktu tunda propagasi tPLH dari gerbang PTL pada gambar 40 dapat ditentukan sebagai untuk vO mencapai VDD/2. Sebuah transistor PMOS QR, yang gatenya dikendalikan oleh tegangan keluaran dari inverter, vO2, ditambahkan pada rangkaian. Perhatikan pada saat keluaran dari gerbang PTL, vO1, ‘rendah’ (=0), vO2 akan ‘tinggi’ (=VDD), dan QR akan ‘off’. Sebaliknya jika vO1 ‘tinggi’ tetapi ≠ VDD keluaran dari inverter akan ‘rendah’ dan Q’R akan ‘on’, mencatu arus untuk mengisi C sampai VDD. Proses ini akan berhenti pada saat vO1 = VDD. Fungsi pengembalian level yang dilakukan oleh QR sering dipakai pada perancangan rangkaian digital MOS. Karena QR ada pada jalur umpan balik, jadi QR tidak mempunyai peranan yang besar pada cara kerja rangkaian, selain untuk mengembalikan level VOH ke VDD, kp dipilih lebih kecil dari kn (1/5 – 1/3). Transistor QR disebut ‘transistor PMOS yang lemah’ Cara lain untuk memperbaiki level sinyal VOH adalah dengan cara penyelesai secara teknologi yaitu dengan mengurangi Vtn, idealnya menggunakan divais yang mempunyai Vtn = 0 Penggunaan Gerbang Transmisi CMOS sebagai Saklar Perbaikan kinerja statik dan dinamik pada saklar dapat diperoleh dengan menggunakan gerbang transmisi CMOS. Gerbang transmisi menggunakan sepasang transistor komplementer yang dihubungkan secara paralel. Saklar ini mempunyai aliran arus dua arah dan menunjukkan resistansi yang hampir konstan untuk selang level tegangan masukan yang lebar. Karakteristik ini membuat gerbang transmisi merupakan saklar yang baik untuk pemakaian digital dan analog. Gambar 29(a) menunjukkan saklar gerbang transmisi pada posisi ‘on’ dengan masukan, vI, menuju VDD pada t=0. Asumsikan, keadaan awal tegangan keluaran = 0, QN akan bekerja pada daerah jenuh dan mencatu arus pengisian: iDN 12 k n VDD vO Vtn 2 k n k n' W L Vt ditentukan oleh body effect karena source mempunyai tegangan vO relatif ke body Vtn Vt 0 vO 2 f 2 f Transistor QN akan mengalirkan arus yang akan berkurang menuju nol pada vO = VDD – Vtn. Tetapi QP bekerja dengan VSG = VDD dan pada awalnya dalam keadaan jenuh. iDP 12 k p VDD Vtp 2 Karena body dari QP terhubung ke VDD, |Vtp| akan tetap konstan = |Vt0| dan asumsikan harganya sama dengan Vtn. Arus total pengisian kapasitor adalah jumlah iDN dan iDP. Sekarang QP akan memasuki daerah trioda pada vO = |Vtp|, tetapi akan terus mengalir sampai C terisi penuh dan vO= VOH= VDD. Jadi divais kanal –p akan memberikan gerbang ‘good 1’. Ketika vI menuju ‘rendah’, seperti pada gambar 29(b), QN dan QP bertukar peran. Analisa rangkaian pada gambar 29(b) akan menunjukkan bahwa QP akan berkurang konduksinya jika vO turun sampai |Vtp|, di mana |Vtp| adalah: Transistor QN terus ‘conduct’ sampai V Cterisi V penuh Vdan vOv= VOL2= 0 V, ‘good 2 0’ tp t0 DD O f f Perbaikan kinerja ini didapat dengan rangkaian yang lebih rumit, area dan kapasitansi yang lebih besar. Contoh Rangkaian PTL Rangkaian Logika Dinamik (Dynamic Logic Circuits) Rangkaian logika statik: - Setiap simpul, pada setiap saat, mempunyai jalur beresistansi rendah ke VDD atau ke ground. - Setiap simpul, pada setiap saat, mempunyai tegangan tertentu. - Tidak ada simpul yang mengambang (floating) - Tidak memerlukan clock untuk mengoperasikannya. Rangkaian logika dinamik: - Tergantung dari penyimpanan tegangan sinyal pada kapasitor parasitik pada simpul tertentu. - Karena ada kebocoran, sehingga rangkaian perlu di ‘refresh’ secara periodik, akibatnya diperlukan clock. Perbandingan beberapa jenis rangkaian logika. CMOS: - Mudah dirancang - Mempunyai simpangan logika maksimum - Tahan terhadap derau - Tidak ada disipasi daya statik - Dapat dirancang untuk mempunyai tPLH = tPHL. - Memerlukan 2 transistor untuk setiap variabel masukan. - Untuk fan-in yang besar, diperlukan area yang besar, dan akibatnya meningkatkan kapasitansi, disipasi daya dinamik dan waktu tunda propagasi Pseudo-NMOS: - Mengurangi jumlah transistor yang diperlukan pada jenis CMOS - Ada disipasi daya statik. - Area silikon kecil - Pemakaian terbatas - Memerlukan inverter komplementer untuk mengembalikan level sinyal, terutama jika saklar hanya terdiri dari NMOS transistor, PTL Logika Dinamik: - Mempunyai jumlah transistor yang kecil, - Tidak ada disipasi daya statik - Rangkaian lebih kompleks dan kurang ‘tahan’. Prinsip Dasar Rangkaian Logika Dinamik Terdiri dari PDN yang menjalankan fungsi yang sama dengan PDN pada CMOS dan pseudo-NMOS dan dua saklar yang dioperasikan oleh clock φ yang mempunyai bentuk gelombang seperti pada gambar 33(b). Ketika φ ‘rendah’, Qp ‘on’, rangkaian pada tahap ‘setup’ atau ‘precharge phase’ Ketika φ ‘tinggi’, Qe ‘on’, rangkaian pada ‘evaluation phase’. CL adalah kapasitansi total antara simpul keluaran dan ground. Selama ‘precharge’, Qp terhubung dan mengisi kapasitansi CL sehingga pada akhir interval ‘precharge’, tegangan pada Y = VDD. Selama ‘precharge’, masukan A, B dan C boleh berubah dan mempunyai nilai tertentu. Karena Qe ‘off’, tidak ada jalur ke ground. Selama ‘evaluation phase’, Qp ‘off’ dan Qe ‘on’. Jika kombinasi masukan adalah yang berkaitan dengan keluaran tinggi, PDN tidak terhubung dan keluaran tetap tinggi pada VDD, jadi VOH = VDD. Tidak ada tPLH yang diperlukan, jadi tOLH = 0. Sebaliknya jika kombinasi masukan berkaitan dengan keluaran rendah, transistor NMOS pada PDN akan terhubung dan membentuk jalur antara simpul keluaran dan ground melalui Qe. Jadi CL akan dikosongkan melalui PDN, dan tegangan keluaran akan berkurang ke VOL = 0 V. Waktu tunda propagasi tPHL dapat dihitung seperti untuk rangkaian CMOS dengan ada tambahan transistor Qe yang diserikan. Penambahan transistor akan menambah waktu tunda. Contoh rangkaian pada gambar 33(c) merealisasikan fungsi: Y A BC Pemilihan ukuran transistor sama seperti pada CMOS. Untuk Qp pilih W/L yang besar untuk memastikan bahwa CL dapat terisi penuh selama selang ‘precharge’ Ukuran Qp tidak terlalu besar supaya tidak menambah kapasitansi CL. Efek non-ideal Noise Margin. Karena selama fasa evaluasi, transistor NMOS mulai terhubung untuk vI = VIH Jadi noise margin menjadi: NM L Vtn NM H VDD Vtn Pengurangan Tegangan Keluaran karena Efek Kebocoran Karena tidak ada jalur ke ground melalui PDN, tegangan keluaran tetap tinggi = VDD. Hal ini berdasarkan asumsi bahwa muatan pada CL tetap ada. Kenyataannya akan ada arus bocor yang menyebabkan CL dikosongkan secara perlahan dan vY berkurang. Sumber utama dari kebocoran adalah arus balik dari reverse-biased junction antara drain dari transistor yang terhubung ke simpul keluaran dan substrate. Arus itu dapat berkisar antar 10-15 – 10-12 A, dan meningkat dengan naiknya suhu ( hampir dua kali setiap kenaikan suhu 10°C). Jadi rangkaian bisa salah bila clock dioperasikan pada frekuensi yang sangat rendah dan tegangan keluaran tidak di’refresh’ secara berkala. Charge Sharing Ada satu cara yang lebih penting yang menyebabkan CL berkurang muatannya dan menyebabkan vY turun di bawah VDD. Perhatikan gambar 48(a) yang menunjukkan hanya Q1 dan Q2, bagian atas dari PDN, dan transistor precharge Qp. C1 adalah kapasitansi antara simpul bersama Q1 dan Q2 dengan ground. Pada awal fasa evaluasi, setelah Qp ‘off’ dan CL terisi sampai VDD, asumsikan CL dikosongkan dan masukan pada gate Q1 ‘tinggi’ dan masukan pada gate Q2 ‘rendah’ Q1 akan ‘on’ dan arus drain-nya, iD1, akan mengalir seperti yang ditunjukkan.pada gambar. Jadi iD1 akan mengosongkan CL dan mengisi C1. iD1 akan berkurang sampai nol, CL akan kehilangan sebagian muatannya yang akan ditransfer ke C1. Gejala ini disebut ‘charge sharing’. Untuk mengurangi pengaruh ‘charge sharing’ dapat dilakukan dengan menambah divais kanal –p yang selalu ‘on’ dan mengalirkan arus yang kecil untuk menggantikan muatan yang hilang pada CL seperti yang ditunjukkan pada gambar 34(b). Hal ini menyebabkan adanya disipasi daya statik. Di sisi lain, penambahan transistor ini akan menurunkan level impedansi pada simpul keluaran dan membuat simpul ini tidak rentan terhadap derau. Pendekatan lain untuk menyelesaikan masalah charge sharing adalah mengisi dulu simpul internal yaitu mengisi kapasitor C1. Cara ini akan meningkatkan kerumitan rangkaian dan kapasitansi simpul. Perhatikan gambar 35, dua gerbang dinamik dengan satu masukan dihubungkan secara cascade. Selama fasa precharge, CL1 dan CL2 akan diisi melalui Qp1 dan Qp2. Jadi pada akhir interval precharge vY1 = VDD dan vY2 = VDD. Apa yang terjadi pada fasa evaluasi untuk kasus masukan A tinggi. Keluaran Y1 ‘rendah’ (vY1 = 0 V) dan Y2 tinggi (vY2 = VDD). Kenyataannya sedikit berbeda. Pada saat fasa evaluasi dimulai, Q1 ‘on’ dan CL1 mulai dikosongkan. Pada waktu bersamaan Q2 ‘on’ dan CL2 juga mulai dikosongkan. Hanya saja ketika vY1 turun di bawah Vtn akan menyebabkan Q2 ‘off’. Sayangnya pada saat itu CL2 akan kehilangan jumlah muatan yang cukup banyak dan vY2 akan berkurang dari harga yang diharapkan, VDD. Hal ini cukup serius yang membuat masalah sederhana untuk men-cascade gerbang menjadi tidak praktis. Domino CMOS Logic Logika CMOS domino adalah bentuk logika dinamik yang menghasilkan gerbang yang dapat di-cascade-kan. Logika CMOS domino terdiri dari gerbang logika dinamik dihubungkan dengan inverter CMOS pada keluarannya. Perhatikan gambar 37(a). Pada akhir precharge, X1 = VDD, Y1 = 0 V, X2 = VDD dan Y2 = 0 V. Asumsikan A ‘tinggi’ pada awal evaluasi. Jadi pada saat φ, kapasitor CL1 akan mulai proses pengosongan, menarik X1 turun. Bersamaan dengan itu, masukan ‘rendah’ pada gate dari Q2 menjaga Q2 tetap ‘off’, dan CL2 tetap terisi penuh. Ketika vX1 turun di bawah tegangan ambang dari inverter I1, Y1 akan naik dan Q2 ‘on’, yang akan mulai mengosongkan CL2 dan menarik X2 ‘rendah’. Akibatnya Y2 akan naik ke VDD. Dari penjelasan di atas terlihat bahwa karena keluaran dari gerbang domino ‘rendah’ pada awal evaluasi, tidak ada pengosongan kapasitor yang prematur yang akan timbul karena gerbang yang di-cascade. Seperti pada gambar 37(b), keluaran Y1 membuat transisi 0-ke-1 tPLH detik sesudah ‘rising edge’ dari clock. Akibatnya keluaran Y2 membuat transisi 0-ke-1 sesudah satu interval tPLH lainnya. Propagasi dari ‘rising edge’ melalui gerbang yang dicascade menyerupai domino yang jatuh satu persatu. Logika domino CMOS ditemukan pada ‘address decoder’ pada ‘memory chips’ Emitter Coupled Logic (ECL) ECL adalah jenis rangkaian logika yang paling cepat. Kecepatan yang tinggi ini diperoleh dengan: - mencegah semua transistor memasuki daerah jenuh → mencegah waktu tunda penyimpanan. - menjaga simpangan logika yang relatif kecil (kira-kira 0,8 V atau kurang) → mengurangi waktu pengisian atau pengosongan kapasitansi beban atau kapasitansi parasitik lainnya. Keadaan jenuh pada ECL dapat dihindari dengan menggunakan pasangan differential BJT sebagai saklar arus. Prinsip Dasar ECL berdasarkan pada penggunaan saklar kendali arus yang realisasinya menggunakan pasangan differential seperti yang terlihat pada gambar 38. Pasangan transistor di-bias dengan sumber arus yang konstan I,dan satu sisi dihubungkan dengan sumber tegangan rujukan VR. Arus I dapat diarahkan ke Q1 atau Q2 di bawah kendali sinyal masukan vI. Level logika keluaran: VOH = VCC dan VOL = VCC –IRC, sehingga simpangan logika keluaran = IRC. Catatan: - Sifat rangkaian differential membuat rangkaian kurang sensitif terhadap derau. - Arus yang ditarik dari catu daya tetap konstan selama proses switching. - Level logika keluaran keduanya merujuk ke VCC sehingga dapat dibuat stabil dengan mengoperasikan rangkaian dengan VCC = 0, artinya menggunakan catu daya negatif. - Perlu disediakan beberapa cara untuk membuat level sinyal keluaran kompatibel dengan sinyal pada masukan sehingga satu gerbang dapat men-drive gerbang lainnya. - Adanya keluaran komplementer menyederhanakan perancangan logika dengan ECL. Jenis ECL - ECL 100K dengan karakteristik: - .Waktu tunda gerbang pada orde 0,75 ns - disipasi daya kira-kira40 mW/gerbang, untuk DP = 30 pJ. - ECL 10K dengan karakteristik: - .-Waktu tunda gerbang pada orde 2 ns - -disipasi daya kira-kira 25 mW/gerbang, untuk DP = 50 pJ. - Walaupun DP pada ECL 10K lebih tinggi daripada pada ECL 100K, ECL 10K lebih mudah digunakan. Hal ini disebabkan oleh waktu naik dan turun dari pulsa masukan dibuat panjang untuk mengurangi ‘crosstalk’ antara saluran sinyal yang berdekatan. - ECL disebut juga Current Mode Logic (CML) yang banyak digunakan pada aplikasi VLSI. - Rangkaian Gerbang Dasar - Rangkaian gerbang dasar jenis ECL 10K terlihat pada gambar 39. - Rangkaian terdiri dari 3 bagian: - Rangkaian yang terdiri dari Q1, D1, D2, R1, R2 dan R3 membangkitkan tegangan rujukan VR = -1,32 V pada suhu kamar. Harga tegangan rujukan ini dibuat bervariasi terhadap suhu dengan cara tertentu sehingga noise margin konstan. Tegangan inipun dibuat tidak sensitif terhadap variasi pada VCC. - Satu sisi pada penguat differential terdiri dari transistor rujukan QR yang base-nya terhubung ke tegangan rujukan VR. Sisi yang lain terdiri dari beberapa transistor yang terhubung paralel, dengan base terpisah, dan masing-masing terhubung pada gerbang masukan. - Jika tegangan yang terpasang pada A dan B pada level logika 0, kira-kira 0,4 V di bawah VR, QA dan QB akan ‘off’ dan arus IE akan mengalir melalui QR. Akibatnya ada penurunan tegangan pada RC2, sehingga tegangan collector QR ‘rendah’. - Jika tegangan yang terpasang pada A atau B pada level logika 1, kira-kira 0,4 V di atas VR, QA atau QB, atau dua-duanya akan ‘on’ dan arus IE akan mengalir melalui QA atau QB atau dua-duanya dan arus mengalir melalui RC1. Akibatnya ada penurunan tegangan pada RC1, sehingga tegangan collector akan turun. Sementara itu, karena QR ‘off’, tegangan collector-nya akan naik. - Jadi tegangan collector QR akan ‘tinggi’ jika A atau B atau dua-duanya ’tinggi’, sehingga pada collector QR terealisasi fungsi logika A+B. - Sebaliknya, tegangan collector bersama dari QA dan QB akan ‘tinggi’ jika A dan B secara bersamaan ‘rendah’. Jadi pada collector bersama QA dan QB terealisasi fungsi logika - Jadi gerbang dua masukan pada gambar 39 merealisasikan fungsi OR dan NOR. Tersedianya keluaran komplementer adalah keunggulan yang penting pada ECL; hal ini menyederhanakan perancangan logika dan mencegah penggunaan inverter tambahan yang akan menambah waktu tunda. - Catatan: resistansi pada terminal gate masukan yang terhubung dengan catu negatif memungkinkan pemakai untuk membiarkan terminal masukan yang tidak terpakai ‘terbuka’. Terminal masukan yang terbuka akan ditarik ke catu tegangan negatif dan transistor yang terhubung akan ‘off’. - Bagian ketiga dari rangkaian gerbang ECL terdiri dari dua emitter follower, Q2 dan Q3. Emitter follower tidak mempunyai beban ‘on-chip’ karena pada banyak aplikasi dari rangkaian logika kecepatan tinggi, gerbang keluaran men-drive saluran transmisi yang berakhir pada sisi lain, seperti yang terlihat pada gambar 40. - Emitter follower mempunyai 2 fungsi: - 1. Sebagai level shifter dengan menurunkan tegangan keluaran sebanyak VBE. Tujuannya agar kompatibel dengan level tegangan gerbang yang lain - - - Gambar 42 adalah sketsa dari karakteristik transfer OR vOR versus vI, dengan parameter VOL, VOH, VIL dan VIH. - Untuk menyederhanakan perhitungan VIL dan VIH, kita gunakan definisi unity-gain. Terutama kira akan berasumsi bahwa pada titik x, transistor QA melalukan 1% dari IE sedangkan transistor QR melalukan 99% dari IE. Hal sebaliknya diasumsikan untuk titik y. - Pada titik x kita mempunyai IE QR IE QA Gunakan hubungan eksponensial iE – vBE, diperoleh: 99 VBE Q VBE Q VT ln 99 115 mV R Yang memberikan: VIL = -1,32 – 0,115 = -1,435 V Asumsikan QA dan QR ‘matched’, maka dapat ditulis: A VIH – VR = VR – VIL VIH = -1,205 V Beberapa pengamatan: Untuk vI = VIH menghasilkan tegangan keluaran sedikit lebih tinggi dari VOL. Hal ini disebabkan karena RC1 dipilih lebih kecil dari RC2 supaya dengan vI sama dengan harga normal logika 1, keluaran akan sama dengan VOH yang didapat untuk keluaran OR. Dengan vI melebihi VIH, transistor QA bekerja pada mode aktif dan rangkaian pada gambar 45 dapat dianalisa untuk menghitung penguatan dari penguat, yaitu kemiringan dari segmen yz dari karakteristik transfer. Pada titik z, QA ‘jenuh’ Jika vI dinaikkan melebihi vI = VS akan menyebabkan tegangan pada collector, vNOR, meningkat. Kemiringan pada segmen melebihi titik z pada karakteristik transfer tidak lagi unity, kira-kira 0,5 karena QA terdorong jauh ke daerah jenuh. Fan-Out Ketika sinyal masukan pada gerbang ECL rendah, arus masukan sama dengan arus yang melalui resistor pull-down 50-kΩ. Jadi Beberapa pengamatan: Untuk vI = VIH menghasilkan tegangan keluaran sedikit lebih tinggi dari VOL. Hal ini disebabkan karena RC1 dipilih lebih kecil dari RC2 supaya dengan vI sama dengan harga normal logika 1, keluaran akan sama dengan VOH yang didapat untuk keluaran OR. Dengan vI melebihi VIH, transistor QA bekerja pada mode aktif dan rangkaian pada gambar 45 dapat dianalisa untuk menghitung penguatan dari penguat, yaitu kemiringan dari segmen yz dari karakteristik transfer. Pada titik z, QA ‘jenuh’ Jika vI dinaikkan melebihi vI = VS akan menyebabkan tegangan pada collector, vNOR, meningkat. Kemiringan pada segmen melebihi titik z pada karakteristik transfer tidak lagi unity, kira-kira 0,5 karena QA terdorong jauh ke daerah jenuh. Fan-Out Ketika sinyal masukan pada gerbang ECL rendah, arus masukan sama dengan arus yang melalui resistor pull-down 50-kΩ. Jadi Hal ini disebabkan pada tepi naik (rising edge) dari pulsa keluaran emitter follower, arus keluaran diperlukan untuk mengisi kapasitansi beban dan kapasitansi parasitik, Sebaliknya pada saat sinyal pada base dari emitter follower ‘turun’, emitter follower ‘off’ dan kapasitansi beban dikosongkan melalui kombinasi resistansi beban dan resistansi pull-down. Untuk memperoleh keuntungan penuh dari kecepatan operasi ECL, harus diperhatikan cara interkoneksi berbagai gerbang logika dalam sistem. Disipasi Daya Karena sifat penguat differential dari ECL, arus gerbang tetap konstan dan hanya dikendalikan dari satu sisi ke sisi lain dari gerbang tergantung dari sinyal masukan. Jadi arus catu dan disipasi daya dari gerbang ECL yang tidak terterminasi tetap konstan tidak tergantung dari status logika dari gerbang. Jadi tidak ada tegangan spike pada saluran catu. Efek Termal Titik tengah dari simpangan keluaran bervariasi dengan suhu pada ‘rate’ yang sama seperti pada tegangan rujukan.