24_Analisis Dan Perancangan Integrated Circuit AND OR INVERTER

advertisement

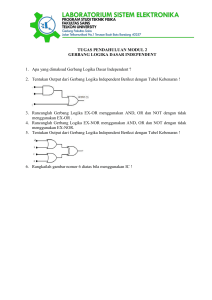

SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 Analisis Dan Perancangan Integrated Circuit AND OR INVERTER (AOI) Berteknologi HCMOS (High Speed Complementary Metal Oxide Semiconductor) Agung Darmawansyah Teknik Elektro Universitas Brawijaya - Mayjen Haryono 167 Malang [email protected] ABSTRAK Penelitian ini bertujuan untuk menganalisa dan merancang IC AOI HCMOS menggunakan teknologi High Speed Complementary Metal Oxide Semiconductor (HCMOS) dan membandingkannya dengan spesifikasi IC berteknologi CMOS yang ada. Teknologi HIGH SPEED CMOS (HCMOS) sangat penting untuk mengurangi desipasi daya rangkaian dan meningkatkan kecepatan operasi tanpa mengubah karakteristik yang lain. Digunakan progam PSPICE untuk menguji spesifikasi rangkaian dan ukuran dimensi komponen. Sedangkan penggambaran tataletak IC AOI HCMOS menggunakan program Mikrowin. Langkah pertama adalah menentukan spesifikasi dan tipe rangkaian sesuai dengan parameter proses yang ada di dalam AOI HCMOS. Langkah berikutnya mengevaluasi secara manual hubungan bentuk dimensi antar komponen di dalam rangkaian. Hasil yang optimal didapatkan dari perhitungan dan simulasi berdasarkan spesifikasi Karakteristik Transfer Tegangan (VTC) yang terdiri atas VOH,VOL,VIH dan VIL, waktu tunda (tpLH dan tpHL), dan desipasi daya serta penggambaran berupa layout suatu IC AOI HCMOS. Simulasi dari IC AOI HCMOS menunjukkan hasil yang sesuai dengan spesifikasi yang direncanakan. Perancangan IC AOI HCMOS dapat digunakan tegangan catu 5V dengan kapasitor kopling sebesar 50pF. Spesifikasi karakteristik transfer tegangan menghasilkan tegangan output keadaan tinggi (VOH) 4,95V, tegangan input keadaan tinggi (VIH) 2,8V, tegangan input keadaan rendah (VIL) 0V, tegangan output keadaan rendah (VOL) 0V. Waktu tunda kondisi tinggi ke rendah (tpHL) sebesar 6 ns sedangkan waktu tunda kondisi rendah ke tinggi (tpLH) sebesar 5,8 ns. Desipasi daya yang dihasilkan sebesar 1,25mW. Dari hasil simulasi dan perancangan menunjukkan bahwa spesifikasi IC AOI HCMOS mempunyai kecepatan yang baik dibandingkan dengan IC CMOS biasa. Kata kunci: Rangkaian terpadu, Teknologi HCMOS, Simulasi, Spesifikasi 1. PENDAHULUAN Penggabungan rangkaian elektronik dan keluarga rangkaian terpadu, memungkinkan terbentuknya rancangan chips yang kecil dengan unjukkerja yang tinggi. Penggunaan chips digital memiliki peranan yang sangat penting dalam perangkat elektronik. Kehandalan dan kemudahan dalam pengembangan menjadi pilihan perangkat elektronik banyak dirancang untuk bekerja secara digital. Sistem digital bekerja pada logika “1” dan logika “0” dengan batas tegangan (VIL, VOL, VOH, VIH) yang terkadang berbeda antara satu jenis IC dengan yang lain. Implementasi dari suatu logika digital dalam bentuk rangkaian elektronik terpadu menggunakan gerbang digital. Ada berbagai jenis famili gerbang digital diantaranya adalah DTL, RTL,TTL, ECL, IIL dan CMOS. Pada saat awal perkembangan sistem digital, logika TTL sangat populer. Sifat dari transistor bipolar sebagai penyusun utama logika TTL yang berdisipasi daya tinggi membuat logika TTL mulai ditinggalkan dalam teknologi rangkaian terpadu. Sebagai gantinya dipilih logika CMOS. Keunggulan CMOS terletak pada desipasi daya tiap gerbang yang sangat rendah (dalam orde µW), fan out yang tinggi serta noise margin yang baik (sekitar 0,45VDD). Kelemahan CMOS adalah bila dipergunakan untuk menggerakkan beban kapasitif. Propagation delay CMOS menjadi lambat bila menggerakkan beban dengan kapasitansi besar sedangkan TTL jauh lebih cepat. Untuk mengatasi hal ini telah dikembangkan teknologi lain, seperti HCMOS. Teknologi HCMOS adalah teknologi CMOS yang didesain secara khusus sehingga memiliki propagation delay yang sama dengan LS-TTL, terutama untuk menggerakkan beban dengan kapasitansi besar. Dasar permasalahan proses analisis dan perancangan IC AOI HCMOS ini adalah, dalam setiap perancangan piranti pemroses sinyal,dikehendaki suatu output yang ideal. Kondisi ideal mencakup beberapa aspek diantaranya ; VTC (Voltage Transfer Characteristic), propagation delay yang kecil, dan disipasi daya yang kecil. Untuk mendapatkan suatu kondisi yang ideal, maka dalam A2-124 SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 analisis digunakan parameter – parameter yang berpengaruh dalam proses perancangan. Semua parameter akan dieliminasi pada suatu parameter paling utama yaitu nilai rasio L/W dari CMOS sebagai driver. Perbandingan nilai L (Length) dan W (Width) inilah yang akan menentukan suatu kondisi ideal pada VTC AOI HCMOS. 2. LANDASAN TEORI 2.1. MOSFET MOSFET (Metal Oxide Semiconductor Field Effect Transistor) adalah suatu transistor dari bahan semikonduktor (silikon) dengan tingkat konsentrasi ketidakmurnian tertentu. Ketidakmurnian ini akan menentukan jenis transistor tersebut, yaitu transistor MOSFET tipe-N (NMOS) atau transistor MOSFET tipe-P (PMOS). Bahan silikon ini pula yang akan digunakan sebagai landasan dari penguras (drain), sumber (source), dan gerbang (gate). Selanjutnya dibuat sedemikian rupa sehingga antara substrat dan gerbangnya dibatasi oleh bahan oksida silikon yang sangat tipis. Oksida ini diendapkan di atas sisi kiri dari kanal, dengan demikian transistor MOSFET akan mempunyai kelebihan jika dibandingkan dengan transistor BJT (Bipolar Junction Transistor), yaitu menghasilkan disipasi daya yang lebih kecil (Norbert, 1995:307). 2.2. Jenis – Jenis MOSFET Bila dilihat dari cara kerjanya, Transistor MOS dapat dibagi dua, yaitu: (1). Transistor Mode Pengosongan (Depletion Mode Transistor) Pada Transistor Mode Pengosongan, antara drain dan source terdapat saluran yang menghubungkan dua terminal tersebut, yang mempunyai fungsi sebagai saluran tempat mengalirnya elektron bebas. Lebar saluran dapat dikendalikan oleh tegangan gerbang. (2). Transistor Mode Peningkatan (Enhancement Mode Transistor) Transistor mode ini pada fisiknya tidak memiliki saluran antara drain dan source-nya karena lapisan body meluas dengan lapisan SiO2 pada terminal gate. Dilihat dari jenis saluran yang digunakan, MOSFET dapat dikelompokkan menjadi tiga, antara lain: 1). NMOS (Negative MOS) Negatif MOS adalah MOSFET yang mengalirkan arus penguras sumber menggunakan saluran dari bahan elektron, sehingga arus akan mengalir jika tegangan gerbang lebih positif dari substrat dan nilai mutlaknya lebih besar dari VT (Voltage Threshold). 2). PMOS (Positive MOS) Positif MOS adalah MOSFET yang mengalirkan arus penguras sumber melalui saluran positif yang berupa hole, dimana arus akan mengalir jika A2-125 tegangan gerbang lebih negatif terhadap tegangan substrat dan nilai mutlaknya lebih besar dari VT . 3). CMOS (Complementary MOS) MOSFET tipe complementary ini mengalirkan arus penguras sumber melalui saluran tipe-n dan tipe-p secara bergantian, sesuai dengan tegangan yang dimasukkan pada gerbangnya (gate). 2.3. Karakteristik MOSFET Grafik karakteristik MOSFET arus ID sebagai fungsi VDS dengan parameter VGS dalam Gambar 1 dan grafik karakteristik alih dapat dilihat dalam Gambar 2. Gambar 1. Grafik karakteristik MOSFET arus ID sebagai fungsi VDS dengan parameter VGS Di sebelah kiri garis putus-terjepit (pinch off) transistor berlaku sebagai tahanan (resistor) yang dikendalikan tegangan tak linier. Ini disebut sebagai daerah kerja linier atau tak jenuh (non-saturation) atau disebut juga daerah ohmic. Untuk daerah disebelah kanan putus-terjepit (pinch off) grafik mendekati sumber arus yang dikendalikan tegangan. Gambar 2. Grafik karakteristik alih tipe-n dan tipe-p Untuk transistor NMOS tipe pengosongan, VT adalah negatif dan arus penguras (drain) dapat mengalir bahkan untuk VGS = 0. Untuk transistor PMOS semua polaritas tegangan dan arus dibalik sehingga akan didapat grafik karakteristik arustegangan i-v. SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 2.4. Tegangan Ambang (Threshold Voltage) Tegangan ambang dapat didefinisikan sebagai tegangan minimal yang diperlukan suatu sistem (dalam hal ini transistor MOS) untuk mulai mengalir atau dalam sebuah MOS adalah tegangan antara gate dan ground yang menyebabkan arus antara drain dan source maksimal (saturasi). Tegangan Ambang ini diatur dengan menggunakan pengubah konsentrasi doping. Tegangan ambang untuk MOSFET dapat dinyatakan dengan persamaan untuk Tegangan ambang (VT). VT = VTo + γ dengan : ( 2φ + V B − 2φ ) (2.1) VT = tegangan threshold tegangan body (bulk) Dengan body (bulk) dihubungkan ground (VB = 0V). Dalam analisis teknologi CMOS effect bias body tidak perlu dimasukkan dalam perhitungan (Haznedar,1990), logika dasar CMOS dapat dibias dengan VT = VTo, sehingga untuk memudahkan penulisan, VT akan digunakan untuk menyatakan Tegangan ambang jika VT = VTo. γ = 2 qε s N a C OX p) (Semikonduktor tipe- (2.3) kT n φF = ln q ni − Q0 (2.5) C ox dengan C ox adalah kapasitansi per satuan luas φox = dielektris gerbang seperti yang didefinisikan oleh: C ox = silikon, COX adalah kapasitansi dalam farad. φ F potensial fermi atau potensial keseimbangan elektrostatik (equilibrium electrostatic). Besarnya dapat ditentukan dengan persamaan: kT ni ln q p potensial gerbang terhadap substrat melalui SiO2 besarnya potensial ini adalah: (2.2) q adalah besar muatan, Na adalah jumlah pembawa muatan mayoritas akseptor, ε s adalah permitivitas φF = terintegrasi NMOS, substrat selalu dihubungkan dengan tegangan paling negatif dalam sistem, sehingga analisis karakteristik fungsi alih akan mendekati keakuratannya. Pada kebanyakan chip MOS, untuk mengubah tegangan ambang dilakukan dengan mengubah konsentrasi doping saluran yang diatur oleh banyaknya ion yang ditanamkan (implant) ke saluran. Penambahan implant tipe P menyebabkan tegangan ambang lebih positif dan sebaliknya penambahan implant tipe N menyebabkan tegangan ambang lebih negatif. Tegangan ambang disimbolkan dengan VTN untuk implant tipe N dan VTP untuk implant tipe P. 2.5. Persambungan MOSFET Dalam persambungan MOSFET, untuk membedakan dengan terminal sumber S, terminal gerbang diberi simbol G dan terminal substrat diberi simbol B (bulk). Potensial di atas silikon dioksida φ ox adalah VTo = tegangan ambang γ = efek bias badan ( V1/2) VB = A2-126 tipe- n) (2.4) k adalah konstanta Boltzman, T adalah temperatur dalam Kelvin, q besaran muatan dalam Coulomb, dan p atau n adalah konsentrasi pembawa muatan mayoritas (dianggap sama dengan konsentrasi doping Na pada persamaan 2.2), ni adalah konsentrasi pembawa muatan dalam semikonduktor intrinsik. Jika VSB MOSFET adalah positif, maka akan meningkatkan tegangan ambang efektif untuk MOSFET kanal-n. Ini disebut efek bias body VT terdapat dalam Persamaan 2.1. Dalam rangkaian (2.6) dengan: Cox = kapasitansi per satuan luas tox = ketebalan silikon dioksida ε ox = permitivitas ruang hampa = 8.86E-12 F/m Untuk muatan maupun kapasitasnya dinyatakan dalam Qo C dan ox . A adalah luas melintang dioksida A A silikon. Potensial oksida silikon φ ox = (Semikonduktor ε ox t ox − Q0 C ox φ ox dapat dinyatakan: (2.7) 2.6. Karakteristik Arus Tegangan Bila VGS lebih besar dari VT, terdapat sebuah saluran penghantar dan VDS menyebabkan arus hanyut ID mengalir dari drain ke source. Tegangan VDS menyebabkan prategangan balik (reverse bias) yang besar dari drain ke body daripada yang ada dari source ke body, jadi terdapat lapisan pengosongan yang lebih lebar pada drain. ID = k' W L VGS =VT 2 VDS ( V − V ) V − GS T DS 2 SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 VDS=(VGS-VT) (2.8) Dimana parameter transkonduktansi adalah k = k’(W/L). Substitusi di atas menghasilkan persamaan: ID = [ k 2 2(VGS − VT )VDS − VDS 2 VGS =VT VDS = (VGS-VT) ] (2.9) k 2 I D = (VGS − VT ) 2 VGS=VT VDS = (VGS-VT) (2.10) 3. PERANCANGAN 3.1. Materi Penelitian Lingkup materi penelitian ini merancang rangkaian terintegrasi AOI HCMOS melalui spesifikasi yang ditentukan melalui kajian atas beberapa data book yang ada, selanjutnya dioptimasikan dengan program simulasi. Studi perancangan ini dibatasi sampai pada gambar tata letak komponen rangkaian sesuai dengan spesifikasi yang diharapkan. Adapun materi kajian terdiri atas empat hal berikut. 1. Perancangan rangkaian serta pemilihan spesifikasi . 2. Penentuan parameter proses dan aturan penggambaran tata-letak, selanjutnya digunakan sebagai perhitungan untuk mendapatkan dimensi komponenkomponen dari rancangan rangkaian terintegrasi AOI HCMOS. 3. Optimasi hasil perhitungan melalui program simulator PSPICE 8 dengan memberi perintah elemen dan kontrol. 4. Penggambaran sesuai dengan aturan gambar yang dipilih tata-letak rancangan rangkaian terintegrasi AOI HCMOS yang sesuai dengan hasil pengoptimasian. 3.2. Spesifikasi Rangkaian A2-127 Gambar 3 menunjukkan konfigurasi gerbang AOI HCMOS. Inisial W U menunjukkan pull up transistor MOSFET tipe-p dan W D menunjukkan pull down transistor MOSFET tipe-n keduanya tersusun dalam konfigurasi CMOS pada tiap gerbang. CL adalah semua kapasitansi baik internal maupun eksternal yang digerakkan oleh gerbang. CL meliputi kapasitansi jalur interkoneksi, bonding pad, jalur konduktor internal, pin IC, jalur konduktor eksternal serta termasuk kapasitansi masukan IC lain yang digerakkan oleh gerbang. Selain kapasitansi terdapat pula komponen pembebanan lain yaitu resistansi keluaran, namun disini dipilih CL karena hanya komponen kapasitansi yang mempengaruhi propagation delay rangkaian. Dilihat dari konfigurasi (2-37) gerbang perbedaan yang mendasar antara AOI HCMOS dan CMOS adalah terdapatnya konfigurasi pasangan dalam rangkaian HCMOS. Gerbang AOI CMOS memanfaatkan keuntungan dari konfigurasi pasangan ini yang dikenal dengan teknik driver kaskada. Dengan pengaturan nilai W dan L dari sistem yang tepat maka akan diperoleh peningkatan propagation delay yang lebih cepat dibanding sistem CMOS konvensional (Gambar 4). Gambar 4. Susunan nilai L/W AOI HCMOS Aturan perancangan gerbang mula-mula dilakukan dengan nilai k adalah 3 (tiga) (gerbang dasar dan 2 buah ), nilai optimum untuk α adalah 3 (tiga), sehingga untuk gerbang dasar, WU 1 = WP LU 1 = LP WD1 = W N (4-1) LD1 = L N untuk pertama WU 2 = WD 2 = 3W N LU 2 = LD 2 = L N WD 2 = 3WD1 = 3W N Gambar 3. Konfigurasi AOI HCMOS LD 2 = LD1 = LN untuk kedua, (4-2) SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 WU 3 = WD 3 = 9W N t PHL = t dir = LU 3 = LD 3 = L N Selanjutnya dapat dicari nilai W N, LN atau nilai W dan L untuk MOSFET tipe-n serta W P, LP atau nilai W dan L untuk MOSFET tipe-p pada gerbang dasar. Nilai W dan L ini dapat dicari apabila diketahui hubungan antara propagation delay sistem dengan driver kaskada atau propagation delay sistem tanpa driver kaskada. Hubungan ini ditunjukkan melalui rumusan, nαt apd t cas nα C G = = t dir t apd C L CG CL selanjutnya berdasar persamaan , 1/ n C α = L CG CL =αn CG (2-74) (4-4) mensubstitusi bentuk t cas nα = t dir α n t cas n = n −1 t dir α t dir = ini (4-5) α n−1t cas n dimana tcas adalah propagation delay dari sistem kaskada dan tdir adalah propagation delay gerbang dasar tanpa struktur kaskada. Parameter tdir dalam fungsi tcas, tcas adalah propagation delay yang diinginkan dari struktur kaskada ini. Selanjutnya setelah tdir atau propagation delay gerbang dasar tanpa struktur kaskada diketahui maka langkah selanjutnya mencari nilai K'N dan K'P atau parameter transkonduktansi MOSFET tipe-n dan tipe-p, t dir = t PLH + t PHL 1 CLVDD CLVDD = + 2 2 K ' P (VDD − VTP )2 K ' N (VDD − VTN ) 2 Untuk mendesain gerbang yang memiliki keluaran simetris harus dibuat nilai tPLH = tPHL sehingga, t PLH = t dir = α n−1t cas n = n = C LVDD K ' N (VDD − VTN ) 2 (4-9) dengan mengetahui nilai K'N dan K'P selanjutnya nilai parameter W dan L dapat dicari dengan menggunakan persamaan, LD 3 = LD1 = L N dengan α n−1t cas (4-3) WD 3 = 9WD1 = 9W N selanjutnya diperoleh, A2-128 C LVDD K ' P (VDD − VTP ) 2 (4-8) K 'N = W 1 µ e C ox N 2 LN untuk K'P parameter µe (mobilitas elektron) digantikan dengan µh (mobilitas hole). Berikut adalah parameter proses dan konstanta yang dipergunakan dalam perhitungan, 2 Cox = 28.8 fF/µm CL = 50 pF VTP = -1 V α=3 (2-79) 2 2 µe = 1350 cm /V.s µh = 480 cm /V.s VTN = 1 V n=3 VDD = 5 V Khusus PMOS : Keqp = 0.375 CJSW = 0.135 fF/µm 2 AD = 16.2 µm CGDO = 0.43 fF/µm 2 CJ = 0.5 fF/µm PD = 11.4 µm Khusus NMOS : Keqn = 0.611 CJSW = 0.8 fF/µm 2 AD = 6.14 µm CGDO = 0.43 fF/µm 2 PD = 9 µm CJ = 0.3 fF/µm 3.3. Disain Nilai W Dan L Transistor - Analisis Propagation Delay Proses disain dimulai dengan menentukan (4-6) parameter yang nilai propagation delay sebagai dirancang. Nilai propagation delay yang dirancang adalah 8 ns untuk nilai CL sebesar 50 pF. Gerbang akan dirancang dengan nilai(4-7) tPLH dan tPHL yang sama agar memiliki keluaran yang simetris. Untuk niali tPLH, α n−1t cas n K 'P = = C LVDD K ' P (VDD − VTP ) 2 nC LVDD α t cas (VDD − VTP n −1 (4-10) ) 2 dan untuk tPHL, α n−1t cas n K 'N = = C LVDD K ' N (VDD − VTN nC LVDD α t cas (VDD − VTN n −1 ) 2 ) 2 (4-9) (4-11) Dengan mensubstitusikan nilai tcas = 8 ns, α = 3, n = 3, CL = 50 pF, VDD = 5 V, VTN = 1 V VTP = -1 V, maka diperoleh nilai K'P dan K'N sebagai berikut, K 'P = 3.50.10 −12.5 = 0.65 mA V 2 33−1.8.10 −9 (5 − 1) 2 SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 K 'N = A2-129 3.50.10 −12.5 = 0.65 mA V 2 3−1 −9 2 3 .8.10 (5 − 1) 2 sehingga diperoleh hasil K'P = K'N = 0.65 mA/V . Setelah nilai K'P dan K'N diketahui maka praktis nilai W dan L transistor pada gerbang dasar akan segera diketahui. Untuk K'N menggunakan persamaan; W 1 µ e C ox N 2 LN WN 2 K ' N = LN µ e Cox K 'N = (2-26) (4-12) dengan mensubstitusi nilai K'N = 0.65 mA/V , µe = 2 2 1350 cm /V.s dan Cox = 28.8 fF/µm , maka diperoleh rasio W dan L untuk MOSFET tipe-n, 2 WN 2K'N 2.0,65.10−3 1 = = = 0.334≈ −4 −15 2 LN µeCox 1350.10 .28,8.10 µ 3 Untuk MOSFET tipe-p maka parameter µe pada harus diganti dengan parameter µh , W 1 µ h Cox P 2 LP WP 2 K ' P = LP µ h Cox K 'P = (2-26) (4-13) dengan mensubstitusi nilai K'N = 0.65 mA/V , µh = 2 2 480 cm /V.s dan Cox = 28.8 fF/µm , maka diperoleh rasio W dan L untuk MOSFET tipe-p, 2 WP 2K'P 2.0,65.10−3 = = = 0.944 ≈ 1 LP µ h Cox 480.10−4.28,8.10−15 µ 2 Microwind menggunakan 0.12 µm CMOS process (λ = 0.06 µm), sehingga untuk nilai W dan L transistor NMOS (MODN) didefinisikan pada nomor ganjil; M1 W N = 0.12 µm LN = 0.36 µm M3 W N = 0.12 µm LN = 0.36 µm s/d M23 W N = 0.12 µm LN = 0.36 µm Sedangkan W dan L transistor PMOS (MODP) didefiniskan pada nomor genap; M2 W P = 0.36 µm LP = 0.36 µm M4 W P = 0.36 µm LP = 0.36 µm s/d M24 W P = 0.36 µm LP = 0.36 µm Kaskade pertama M25 W P = 0.36 µm LP = 0.36 µm M26 W N = 0.36 µm LN = 0.36 µm Sedangkan kaskade ke dua; M27 W P = 1.08 µm LP = 0.36 µm M28 W N = 1.08 µm LN = 0.36 µm Gambar 4 menunjukkan rangkaian transistor lengkap dengan nilai W dan L pada masing-masing transistor beserta node persambungan yang digunakan dalam simulasi SPICE. Gambar 4. Gerbang AOI HCMOS Dengan Nilai W Dan L Transistor 4. HASIL PENELITIAN Simulator rangkaian menggunakan komputer, dalam hal ini digunakan program komputer SPICE; merupakan mekanisme penting dalam analisis dan perancangan rangkaian AOI HCMOS. MOSFET dideskripsikan pada SPICE dengan menggunakan dua pernyataan; satu pernyataan mendeskripsikan sifat alamiah FET serta hubungannya terhadap letaknya pada rangkaian, dan pernyataan lain menentukan nilai parameterparameter FET. 4.1. Parameter Model dalam Simulator SPICE SPICE menyediakan tiga model komponen MOSFET yang berbeda dalam formulasi karakteristik i-v. Variabel LEVEL menentukan model yang akan digunakan untuk merepresentasikan MOSFET secara khusus. Model LEVEL=1 merupakan model paling sederhana yang akan ditinjau dalam proses perancangan ini. Ketepatan simulasi menggunakan LEVEL=1 mencukupi untuk sebagian besar desain dan analisis rangkaian digital AOI HCMOS. 4.2. Proses Simulasi Hasil analisis dan perhitungan matematis perlu disimulasikan untuk mengetahui kebenaran perancangan yang telah dilakukan. Simulasi dilakukan untuk mengetahui VTC, rise time, dan fall time, serta propagation delay. Nilai–nilai yang didapatkan dari tampilan grafik simulasi kemudian akan dibandingkan dengan karakteristik dari CMOS, kemudian dari keduanya akan dapat diketahui teknologi mana yang lebih baik dalam perancangan chips berdasarkan pada kondisi–kondisi ideal. 4.3. Simulasi VTC Untuk mengetahui kebenaran hasil perancangan perlu diketahui terlebih dulu bagaimana tampilan grafik VTC (Voltage Transfer Characteristic) SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 pada hasil simulasi seperti dalam Gambar 13 . Dari tampilan grafik VTC dapat diketahui nilai VOH , VIL, VOL , VIH, dan untuk kemudian dibandingkan kondisi yang lebih baik antara AOI HCMOS dan CMOS. Kondisi ideal untuk tampilan VTC adalah nilai VOH yang semakin mendekati nilai tegangan masukan dan nilai VOL yang mendekati nilai tegangan ground (0V), serta selisih antara nilai VIL dan VIH yang semakin kecil. Pada simulasi VTC, rangkaian diberi masukan DC dengan tegangan catu sebesar 5V. Pada simulasi ini, rangkaian diuji tanpa dan dengan menggunakan beban (CL) Dengan listing program yang benar, dapat menampilan grafik VTC yang benar sehingga aspek–aspek mempengaruhi kondisi ideal AOI HCMOS dapat terpenuhi. Hasil simulasi VTC ditunjukkan dalam Gambar 5. A2-130 5.0V 2.5V 0V V(3) 5.0V 2.5V SEL>> 0V 0s 0.2us 0.4us 0.6us 0.8us 1.0us 1.2us V(16) Time Gambar 6. Hasil simulasi unit step 4.5. Data Simulasi Dari simulasi yang dilakukan, memberikan gambaran tentang kondisi dari rangkaian AOI HCMOS yang telah dirancang dan tercatat nilai–nilai nominal yang akan dipakai sebagai dasar perbandingan serta kesimpulan tentang kondisi rangkaian yang telah dirancang. 4.6. Penggambaran Layout dengan Program Microwind Proses terakhir yang dilakukan adalah melakukan penggambaran layout rangkaian dengan menggunakan program Microwind. Penggambaran dilakukan dengan menggunakan default process Microwind (0.12 µm CMOS Process) dengan λ = 0.12 µm 2 = 0.06µm . Layout akan digambarkan dalam bentuk gerbang AOI tunggal dan empat gerbang dengan pad dalam satu IC. Gerbang AOI tunggal digambar dengan skala 1 : 0.6µm (1 grid senilai dengan 0.6 µm), sedangkan empat gerbang dengan pad digambar dengan skala 1 : 3µm (1 grid senilai dengan 3 µm). Gambar 5. Simulasi VTC 4.4. Simulasi Unit Step Proses simulasi selanjutnya adalah simulasi Unit Step yaitu rangkaian diberi masukan satu gelombang (step) sinyal pulsa. Pada sinyal keluaran akan diamati nilai rise time (tr), fall time (tf), propagation delay (tPLH dan tPHL) untuk kemudian diambil perbandingan antara AOI HCMOS dan CMOS. Tegangan catu dan beban kapasitif (CL) sebesar 50pF. Pada simulasi unit step seperti ditunjukkan dalam Gambar 10, kondisi ideal untuk output sinyal pulsa adalah propagation delay (tPHL dan tPLH) yang lebih cepat dan VOL (steady state) yang mendekati tegangan ground (0V), serta VOH (steady state) yang mendekati tegangan catu (VDD). Deskripsi simulasi unit step sebagai berikut; Gambar 7. Layout AOI HCMOS SEMINAR NASIONAL ELECTRICAL, INFORMATICS, AND IT’S EDUCATIONS 2009 5. KESIMPULAN DAN SARAN 5.1 Kesimpulan Berdasar pada hasil perancangan dan pengujian terhadap rangkaian gerbang AOI HCMOS yang dirancang, diperoleh kesimpulan sebagai berikut, 1. Gerbang AOI HCMOS hasil disain menghasilkan nilai propagation delay 8.1 ns untuk nilai CL 50 pF. 2. Disipasi daya dinamik rangkaian adalah 1.25 mW untuk frekuensi kerja 1 MHz. 3. Noise margin rangkaian adalah 2,2 V 4. Rangkaian menempati layout dengan luasan 105 µm x 14 µm. 5. Rangkaian menempati layout dengan luasan 110 µm x 120 µm beserta pad. 5.2 Saran 1. Nilai W dan L transistor yang dikemukakan dalam penelitian ini akan menghasilkan gerbang AOI HCMOS dengan propagation delay sekitar 3 ns untuk nilai VDD 5 V dan CL 50 pF, bila nilai VDD dan CL berbeda dengan yang ditetapkan maka hasil propagation delay juga akan berbeda. Untuk menghasilkan nilai yang sama maka harus dilakukan disain ulang nilai W dan L transistor. 2. Hasil dari penelitian ini dapat digunakan sebagai salah satu bahan referensi bagi perancangan fungsi logika yang lebih kompleks misalnya flipflop dan counter menggunakan teknologi high speed CMOS (HCMOS). A2-131 DAFTAR PUSTAKA Darmawansyah, Agung. 2000. Jurnal Ilmu-Ilmu Teknik: Analisis dan Perancangan Integrated Circuit (IC) NAND Berteknologi HCMOS (High Speed Complementary Metal Oxide Silicon). Malang: FT. UNIBRAW Faulkenberry L. M., 1982, An Introduction to Operational Amplifiers with Linier IC Applications, John Wiley & Sons Inc., N.Y. Geiger R. L., Allen P. E., Noel R. S., 1990, VLSI Design Techniques for Analog and Digital Circuits, McGraw-Hill, Inc., N.Y. Gregorian R., Temes G. C., 1986, Analog MOS Integrated Circuits for Signal Processing, John Willey and Sons, Inc., New York. Hodges D. A. and Jackson H. G., 1987, Analysis and Design of Digital Intregrated Circuits, Depart. of Electrical Engineering and Computer Sciences, University of California, Berkeley. Karki J., 1999, Effect of Parasitic Capacitance in Op Amp Circuits, Texas Instruments, Inc., DallasTexas. Loveday G., 1986, Essential Electronics an A to Z Guide, Pitman Publishing Company, New Jersey. Mancini R., 1999, Feedback Amplifier Analysis Tools, Texas Instruments, Inc., Dallas-Texas. Rashid, Muh. 2004. Introduction to PSPice Using rd OrCAD for Circuits and Electronics, 3 edition. London: Prentice Hall.