TEKNIK DIGITAL-DIDIK BARU.indd

advertisement

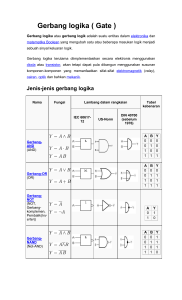

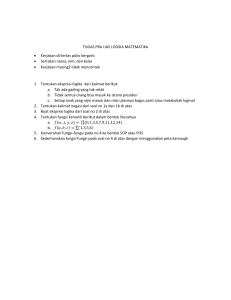

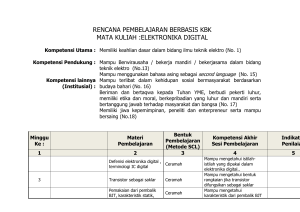

SISTEM DIGITAL; Analisis, Desain dan Implementasi, oleh Eko Didik Widianto Hak Cipta © 2014 pada penulis GRAHA ILMU Ruko Jambusari 7A Yogyakarta 55283 Telp: 0274-889398; Fax: 0274-889057; E-mail: [email protected] Hak Cipta dilindungi undang-undang. Dilarang memperbanyak atau memindahkan sebagian atau seluruh isi buku ini dalam bentuk apa pun, secara elektronis maupun mekanis, termasuk memfotokopi, merekam, atau dengan teknik perekaman lainnya, tanpa izin tertulis dari penerbit. ISBN: Cetakan ke I, tahun 2014 — Untuk de Erni, Azizah, Azzam dan Atikah K ATA P E N G A N TA R Buku ini membahas dasar-dasar sistem digital mulai dari konsep, analisis, perancangan, implementasi dan evaluasi rangkaian logika. Konsep dan analisis rangkaian logika meliputi gerbang logika, ekspresi dan persamaan logika, aljabar Boolean, representasi bilangan digital dan operasi aritmetika. Perancangan (sintesis) ditujukan untuk menghasilkan rangkaian logika yang optimal (seringkali minimal) dengan menyederhanakan persamaan logika menggunakan aljabar Boolean, peta Karnaugh dan metode tabular Quine-McKluskey. Perancangan dilakukan untuk menghasilkan rangkaian kombinasional dan/atau sekuensial. Perancangan rangkaian sekuensial sinkron dilakukan menggunakan model Moore dan Mealy. Teknologi implementasi diarahkan menggunakan chip standar TTL (Transistor-transistor logic) keluarga 7400. Evaluasi rangkaian dilakukan untuk menverifikasi desain rangkaian melalui pengujian atau simulasi menggunakan program bantu komputer. standar kompetensi yang diharapkan Secara khusus, sasaran buku Sistem Digital: Analisis, Desain dan Implementasi ini adalah mahasiswa di program studi/jurusan Sistem Komputer yang sedang mengambil mata kuliah Sistem Digital. Buku ini juga dapat digunakan sebagai buku ajar mata kuliah sistem/teknik/elektronika digital di program studi/jurusan lain seperti Teknik Elektro, Teknik Informatika dan Ilmu Komputer. Buku ini disusun secara runut mulai dari konsep, perancangan, implementasi dan evaluasi suatu rangkaian digital sehingga diharapkan mampu memberikan pemahaman yang komprehensif kepada mahasiswa. Setelah mempelajarinya, mahasiswa diharapkan mampu memahami tentang konsep dasar sistem digital dan menganalisis kebutuhan sistem tersebut dengan tepat. Dengan pemahaman konsep tersebut, mahasiswa akan mampu merancang, mengimplementasikan menggunakan teknologi TTL, mengevaluasi dan mengkomunikasikan solusi desain sistem digital tersebut dengan jelas, runut dan tepat baik tertulis maupun lisan. sistematika penulisan Buku ini terbagi atas 5 bagian dan 12 bab sebagai berikut: 1. Bagian Sistem Digital Bagian ini terdiri atas 2 bab yang membahas tentang sistem digital secara umum dan konsep rangkaian logika. Bab 1 berisi penjabaran sistem digital secara umum, yaitu meliputi sistem analog dan representasi kontinyu, sistem digital dan representasi diskrit, konversi analog ke digital, perangkat digital dan pengantar teknologi rangkaian terintegrasi dan metodologi pengembangan sistem digital. Bab 2 berisi konsep dasar rangkaian logika secara mendalam, yaitu meliputi representasi biner dan saklar sebagai elemen biner, variabel dan fungsi logika, ekspresi dan persamaan logika, tabel kebenaran, gerbang logika dasar dan simbolnya (AND, OR, NOT, NAND dan NOR), rangkaian logika, analisis rangkaian dan diagram pewaktuan sebagai perangkat analisis/evaluasi rangkaian. 2. Bagian Rangkaian Logika Minimal Bagian ini terdiri atas 3 bab dan membahas tentang aljabar Boolean, sintesis rangkaian logika, peta Karnaugh, rangkaian multikeluaran, metode Quine-McKluskey dan program sintesis. Bab 3 berisi proses perancangan (sintesis) rangkaian logika minimal dengan menggunakan aljabar Boolean, yaitu meliputi aljabar Boolean (aksioma, teorema, dan hukum), diagram Venn, penyederhanaan persamaan secara aljabar, sintesis ekspresi logika dari tabel kebenaran, minterm, persamaan SOP (Sum-of-Product) dan notasi kanoniknya, Maxterm, persamaan POS (Product-of-Sum) dan notasi kanoniknya, konversi SOP ke POS dan sebaliknya, rangkaian dua level AND-OR dan OR-AND serta rangkaian dua level NAND-NAND dan NOR-NOR. Bab 4 berisi proses sintesis rangkaian logika minimal menggunakan peta Karnaugh untuk menyederhanakan persamaan fungsi logika, yaitu meliputi peta Karnaugh sampai 6-variabel, strategi minimisasi rangkaian SOP (pengelompokan minterm), kondisi don’t care dan rangkaian dengan spesifikasi tidak lengkap, minimisasi POS (pengelompokan viii Maxterm), istilah dalam fungsi logika (literal, implicant, cover, cost dan prime implicant), implementasi rangkaian logika SOP dengan AND-OR atau NAND-NAND, implementasi rangkaian logika POS dengan OR-AND atau NOR-NOR dan rangkaian multi-keluaran. Bab 5 berisi teknik penyederhanaan fungsi logika untuk memperoleh rangkaian minimal menggunakan metode tabular Quine-McCluskey, yaitu meliputi proses penyederhanaan fungsi secara tabular, penggunaan program bantu sintesis Bmin (Boolean minimizer) dan program bantu simulasi Qucs. 3. Bagian Teknologi Implementasi Bagian ini terdiri atas 2 bab dan membahas tentang rangkaian logika CMOS dan rangkaian terintegrasi standar TTL. Bab 6 berisi penjabaran prinsip kerja transistor CMOS untuk melakukan fungsi-fungsi logika dasar, yaitu meliputi transistor NMOS, PMOS dan CMOS, gerbang logika CMOS: NOT, NAND, NOR, AND, OR, buffer, buffer tiga keadaan dan gerbang transmisi (TG, Transmission Gate) serta XOR dan XNOR. Bab 7 berisi implementasi IC TTL standar seri 7400 untuk rangkaian logika minimum, yaitu meliputi fungsi logika dasar di IC TTL standar seri 7400, metodologi desain rangkaian digital menggunakan IC TTL standar dan tinjauan praktikal dalam implementasi rangkaian IC TTL untuk menjamin kehandalan sinyal digital. 4. Bagian Sistem Bilangan Digital Bagian ini terdiri atas 2 bab dan membahas tentang representasi data digital, operasi bilangan biner dan rangkaian aritmetika biner. Bab 8 berisi representasi data digital (bilangan, angka, karakter), yaitu meliputi representasi posisional: bilangan tak bertanda (unsigned), desimal, biner, oktal dan heksadesimal, konversi bilangan, bilangan bertanda (signed): sign-magnitude, 1’s complement dan 2’s complement, bilangan pecahan fixed-point (titik tetap) dan floating-point (titik mengambang/tidak tetap), bilangan BCD (binary-coded decimal) untuk kode angka desimal dan kode ASCII untuk karakter ix Bab 9 membahas operasi bilangan biner berupa penjumlahan dan pengurangan untuk bilangan bulat dan pecahan fixed-point, yaitu meliputi unit penjumlah 1 bit, operasi penjumlahan dan pengurangan bilangan biner, kondisi overflow dalam operasi aritmetika, unit penjumlah/pengurang n bit, rangkaian penjumlah/pengurang dengan deteksi overflow, desain penjumlah cepat n bit serta desain dan simulasi penjumlah cepat 32 bit.s 5. Bagian Rangkaian Digital Bagian ini terdiri atas 3 bab dan membahas rangkaian kombinasional, elemen rangkaian sekuensial dan rangkaian sekuensial sinkron. Bab 10 membahas rangkaian kombinasional dan blok komponen penyusunnya, yaitu meliputi blok rangkaian kombinasional berupa multiplekser, enkoder, konverter kode, dekoder, demultiplekser, teorema ekspansi Shannon dan desain rangkaian digital menggunakan multiplekser serta rangkaian tampilan 7-segmen. Bab 11 membahas elemen rangkaian sekuensial berupa latch dan flip-flop serta tipe dan karakteristiknya masing-masing. Pokok bahasan di bab ini meliputi prinsip rangkaian sekuensial, elemen penyimpan 1 bit latch, yaitu set-reset latch (latch SR), latch SR tergerbang dan data latch (latch D) serta rangkaian logikanya, elemen penyimpan 1 bit flip-flop berupa data flip-flop (DFF), toggle flip-flop (TFF) dan JK flip-flop (JKFF), register data n bit dan register geser (shift register), pencacah naik-turun serta pencacah sinkron dan asinkron. Bab 12 membahas tentang perancangan rangkaian sekuensial sinkron, yaitu meliputi meliputi mesin keadaan terbatas (FSM, finite state machine), diagram keadaan (state diagram) dan tabel keadaan (state table), desain FSM menggunakan model Moore, implementasi FSM menggunakan DFF, TFF dan JKFF, penyederhanaan rangkaian FSM dengan pemberian nilai keadaan dan desain FSM menggunakan model Mealy serta evaluasi rangkaian sekuensial sinkron. x