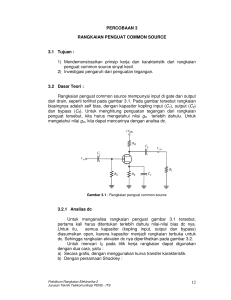

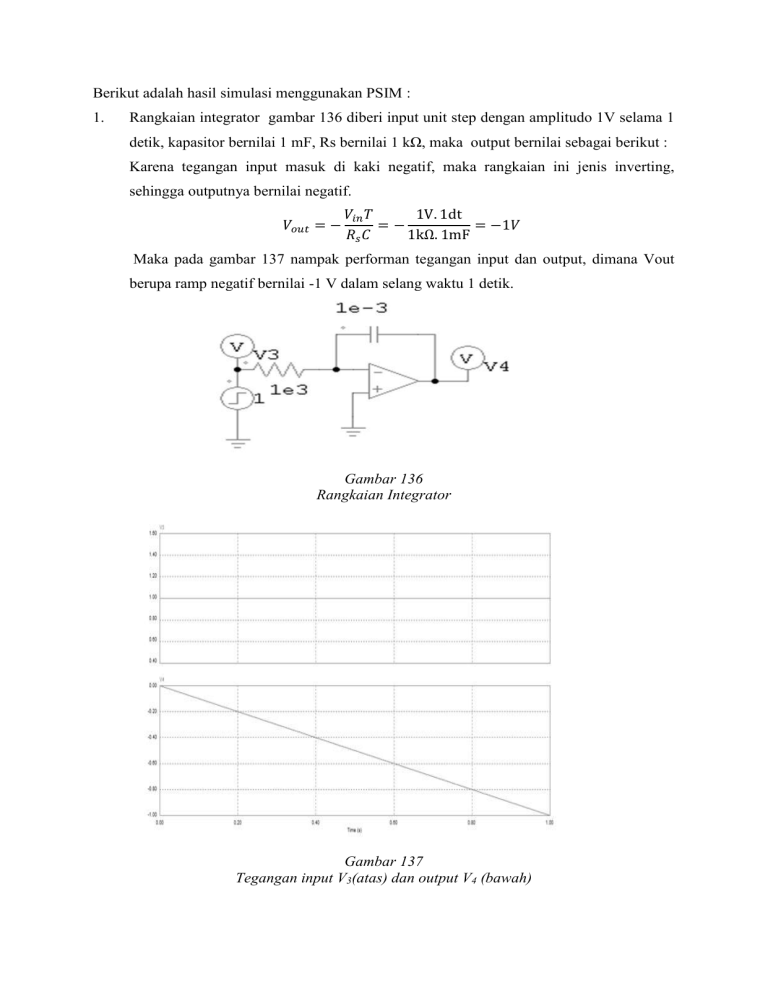

Berikut adalah hasil simulasi menggunakan PSIM : 1. Rangkaian integrator gambar 136 diberi input unit step dengan amplitudo 1V selama 1 detik, kapasitor bernilai 1 mF, Rs bernilai 1 kΩ, maka output bernilai sebagai berikut : Karena tegangan input masuk di kaki negatif, maka rangkaian ini jenis inverting, sehingga outputnya bernilai negatif. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝑇 1V. 1dt =− = −1𝑉 𝑅𝑠 𝐶 1kΩ. 1mF Maka pada gambar 137 nampak performan tegangan input dan output, dimana Vout berupa ramp negatif bernilai -1 V dalam selang waktu 1 detik. Gambar 136 Rangkaian Integrator Gambar 137 Tegangan input V3(atas) dan output V4 (bawah) 2. Rangkaian integrator pada gambar 138 diberi input unit step dengan amplitudo -1 V selama 1 detik, kapasitor bernilai 1 mF, Rs bernilai 1 kΩ, maka output bernilai sebagai berikut : Karena tegangan input masuk di kaki negatif, maka rangkaian ini jenis inverting, sehingga outputnya bernilai negatif. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝑇 −1V. 1dt =− = 1𝑉 𝑅𝑠 𝐶 1kΩ. 1mF Maka pada gambar 139 nampak performance tegangan input dan output, dimana Vout berupa ramp positif bernilai +1V dalam selang waktu 1 detik. Gambar 138 Rangkaian Integrator Gambar 139 Tegangan input V19 (atas) dan output V20 (bawah) 1. Rangkaian integrator pada gambar 140 diberi input sinyal kotak dengan amplitudo 1 Vp-p dan frekuensi 2 Hz, serta duty cycle 50%. Kapasitor bernilai 1 mF, Rs bernilai 1 kΩ, maka output bernilai sebagai berikut : Frekuensi = 2Hz, maka T = 1/F = 0,5 detik. Dan karena tegangan input masuk di kaki negatif, maka rangkaian ini jenis inverting, sehingga outputnya bernilai negatif. Duty cycle 50%, artinya time high = 0,25 detik dan time low juga 0,25 detik. Untuk pulsa periode I, Vin = 1 V, T = 0,25 detik. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝑇 1V. 0,25dt =− = −0,25𝑉 𝑅𝑠 𝐶 1kΩ. 1mF Untuk pulsa periode II, Vin = 0 V, T = 0,25 detik. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝑇 0V. 0,25dt =− = 0𝑉 𝑅𝑠 𝐶 1kΩ. 1mF Untuk pulsa periode III, Vin = 1 V, T = 0,25 detik. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝑇 𝑅𝑠 𝐶 1V.0,25dt = − 1kΩ.1mF = −0,25𝑉 Gambar 140 Rangkaian Integrator Gambar 141 Tegangan input Vin (atas) dan output Vout (bawah) Maka pada gambar 141 nampak performance tegangan input dan output, dimana : Vout periode I : berupa ramp negatif bernilai -0,25 V dalam selang waktu 0,25 detik. Vout periode II : berupa garis lurus atau tidak ada ramp karena Vout nol, tapi garis ini ditarik langsung dari kondisi titik akhir dari Vout I dalam selang waktu 0,25 detik. Vout periode III : berupa ramp negatif bernilai -0,25 V dalam selang waktu 0,25 detik. Tapi garis ditarik dari kondisi titik akhir dari Vout II dalam selang waktu 0,25 detik. Dan seterusnya.... 6.1.6 Soal : 1. Dari rangkaian integrator gambar 142 di bawah, sinyal input kotak 100mVp-p, frekuensi 2 Hz dan duty cycle 35%. Rs = 1 kΩ, C = 1 mF. Buktikan bahwa tegangan output seperti pada kurva pada gambar 143b. Gambar 142 Rangkaian Integrator Gambar 143 Gambar input (a) dan output (b) Dari rangkaian pada gambar 144, dengan data seperti pada gambar, Hitung tegangan 2. output. Gambar 144 Rangkaian Integrator 6.2 Differensiator Differensiator adalah rangkaian yang melakukan operasi diffrensiasi secara matematik. Rangkaian ini menghasilkan tagangan output yang sebanding dengan kemiringan tegangan input. Pemakaian yang umum adalah untuk mendekteksi tepi leading dan tepi lagging dari sebuah pulsa persegi atau untuk menghasilkan output persegi dari input lereng. 6.2.1 Differensiator RC Gambar 145 berikut adalah differensiator RC, dapat digunakan untuk mendifferensialkan sinyal masuk. Masukan yang lazim bukan sinyal sinusoidal, melainkan pulsa persegi seperti nampak pada gambar berikut. Keluaran rangkaian ini berbentuk loncatan positif dan negatif. Gambar 145 Differensiator RC Loncatan positif terjadi pada saat yang sama dengan tepi leading dari masukan. Loncatan negatif terjadi pada saat yang sama dengan tepi leading dari masukan. Perhatikan gambar 146 berikut. Bila tegangan masuk berubah dari 0 ke V, kapasitor mulai diisi secara eksponensial. Setelah lima kali tetapan waktu, tegangan kapasitor berada dalam 1% dari tegangan akhir V. Untuk memenuhi hukum tegangan Kirchhoff, tegangan melintas tahanan adalah : vR = vin –vC Artinya tegangan keluar tiba-tiba melompat dari 0 ke V, lalu menurun secara eksponensial. Pada tepi lagging dari pulsa, tegangan masuk melompat ke arah negatif, dengan uraian yang sama diperoleh loncatan negatif. Bila differensiator RC harus menghasilkan loncatan yang sempit, tetapan waktunya paling tidak harus 10 kali lebih kecil dari lebat pulsa T. Misal, bila lebar pulsa 1ms, maka tetapan waktu (RC) harus lebih kecil atau sama dengan 0,1 ms. Makin kecil tetapan waktunya makin tajam loncatannya . Differensiator Op Amp gambar 146 berikut adalah differensiator op amp, mirip dengan integrator op amp. Perbedaanya terletak pada tahanan dan kapasitor yang saling berpindah tempat. Bila tegangan masuk berubah, kapasitor diisi atau dikosongkan. Karena adanya virtual ground, arus kapasitor mengalir melalui tahanan umpan balik dan menghasilkan tegangan. Tegangan ini setara dengan kemiringan tegangan masuk. Gambar 146 Differensiator Op Amp Masukan yang sering digunakan pada differensiator op amp adalah bentuk lereng. Sehingga diperoleh keluaran berbentuk pulsa membalik. Cara menurunkan arus: pada akhir lereng, tegangan kapasitor adalah V = Q/C. Dengan membagi kedua ruasnya dengan waktu lereng diperoleh : V Q /T T C atau V/T = I/C Maka diperoleh persamaan arus sebagai berikut : I = CV/T Dimana I = arus kapasitor C= kapasitansi V= tegangan pada akhir lereng T= Waktu antara saat awal dan saat akhir lereng. Vout = - Iin.R = CV.R/T (6.2) Jika input berbentuk persegi maka output berbentuk impulse. Seperti gambar 146 di bawah ini. Gambar 150 Gambar 147 Input dan Output Diferensiator 6.2.2 Contoh Soal 1. Gambar 148 berikut memperlihatkan sebuah rangkaian diferensiator dengan masukan lereng 3 V. Gambar 148 Rangkaian Diferensiator Arus kapasitornya adalah : I (0,01F )(3V ) 30 A 1ms Tegangan keluarnya adalah : Vout = (-30uA)(2kΩ) = -60 mV. Sehingga gelombang keluarnya adalah pulsa negatif dengan puncak -60 mV. Berikut adalah hasil simulasi menggunakan PSIM : 1. Rangkaian diferensiator gambar 149 diberi input sinyal segitiga dengan amplitudo 2Vpp frekuensi 2,5 Hz, duty cycle 50%. Kapasitor bernilai 1 mF, Rs bernilai 1 kΩ, maka output bernilai sebagai berikut : F = 2,5 Hz; DC 50%, T = 50% . 1/(2,5) = 0,2 detik. Karena tegangan input masuk di kaki negatif, maka rangkaian ini jenis inverting, sehingga outputnya bernilai negatif. Untuk ramp periode I (naik), Vin = 2 Vp-p, T = 0,2 detik. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝐶𝑅𝑠 2V. 1mF. 1kΩ =− = −10𝑉 𝑇 0,2dt. Untuk ramp periode II (turun), Vin = -2 V (nilai turun sebesar 2 V dari 2V ke nol), T = 0,2 detik. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝐶𝑅𝑠 −2V. 1mF. 1kΩ =− = +10𝑉 𝑇 0,2dt. Untuk ramp periode III (naik), Vin = 2 Vp-p, T = 0,2 detik. 𝑉𝑜𝑢𝑡 = − 𝑉𝑖𝑛 𝐶𝑅𝑠 2V. 1mF. 1kΩ =− = −10𝑉 𝑇 0,2dt. Maka pada gambar 150 nampak performance tegangan input dan output, dimana : Vout periode I : berupa kotak negatif bernilai -10 V dalam selang waktu 0,2 detik. Vout periode II : berupa kotak positif +10 V dalam selang waktu 0,2 detik. Vout periode III : berupa kotak negatif bernilai -10 V dalam selang waktu 0,2 detik. Dan seterusnya.... Gambar 149 Rangkaian Diferensiator Gambar 150 Gambar input (a) dan output (b) 6.2.3 Soal 1. Dari rangkaian pada gambar 151, dengan data sebagai berikut : Tegangan input berupa sinyal segitiga dengan amplitudo 2 Vp-p; 2,5 Hz ; Duty cycle 50 %. RF = 1 kΩ, C = 1mF. Buktikan bahwa sistem ini akan menghasilkan tegangan output seperti gambar 152b. +15 -15 0,01 -60 1 3 0 ms V VV F 2 kmV ICR Gambar 151 Rangkaian Differensiator Gambar 152 Gambar Input dan Output dari Rangkaian Differensiator