Sinyal Logik level dan Famili logik, perubah level

advertisement

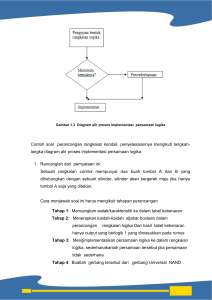

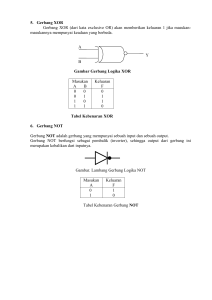

4 Tujuan Sinyal Logik level dan Famili logik, perubah level : Setelah mempelajari Sinyal Logik ini diharapkan 1. Memahami batasan tegangan yang diberlakukan pada logik 1 2. Memahami batasan tegangan yang diberlakukan pada logik 0 3. Mampu menjelaskan prinsip kerja gerbang NOT, pada kejadian sinyal L pada input 4. Mampu menjelaskan prinsip kerja gerbang NOT, pada kejadian sinyal H pada input 5. Mampu menjelaskan prinsip kerja gerbang NOT, pada kejadian sinyal L pada Output 6. Mampu menjelaskan prinsip kerja gerbang NOT, pada kejadian sinyal H pada Output 7. Mampu menghitung kemampuan pembebanan pada rangkaian TTL 8. Memahami perbedaan antara Famili Bipolar dan Famili MOS 9. Mampu mengantisipasi perubahan level pada rangkaian gabungan NMOS dan TTL Prasyarat : Untuk mempelajari Pembelajaran 4 diperlukan kegiatan dan kemampuan seperti di bawah ini , 1. Telah mengerjakan latihan-latihan pada Pembelajaran 3. 2. Semua latihan pada Pembelajaran 3 dijawab dengan Benar. 4.1. Level dan Famili Logik 4.1.1. Level Logik Dalam logik biner kedua keadaan sinyal " 0 " dan " 1 " dibentuk melalui level tegangan yang berbeda. Hal ini dapat di realisasikan juga melalui gambaran ada arus dan tidak ada arus. Menurut Positip Logik sinyal 0 dinyatakan dalam daerah Tegangan Low, sedangkan sinyal 1 dinyatakan dalam daerah Tegangan High. Dalam rangkaian yang terintegrasi ( IC ) harga outputnya hampir tidak mungkin berharga 0 V, hal ini dikarenakan tegangan saturasi dari beberapa transistor yang dibangun di dalamnya antara 0,4 hingga 0,8 Volt. Dari kenyataan di atas maka harga level logik bukan Teknik Mikroprosessor 52 Sinyal Logik merupakan harga kongkrit yang tanpa toleransi, tetapi berupa harga dari daerah tegangan, sehingga level logik dinyatakan dengan L ( Low ) dan H ( High ) dan bukan berupa besaran tegangan yang absolut. Agar lebih jelas dalam pemahaman level logik ada baiknya diperhatikan gambar di bawah ini. OUTPUT Q INPUT I U QH / IH max 5,0 4,5 4,0 H - Level H - Level 3,5 3,0 2,5 U IQ min U IH min 2,0 0,4V 1,5 1,0 0,8 0,5 L - Level U IL max U QL max 0,4V L - Level 0,0 Standard TTL Level Logik Dari gambar di atas dapat dimengerti bahwa level input yang diberi index I mempunyai UIL dan UIH , sedangkan level output yang diberi index Q mempunyai UQL dan UQH. Tegangan input low level ( UIL ) mempunyai harga maksimum 0,8 V sedangkan tegangan input high level ( UIH ) mempunyai harga minimum 2,0 V. Tegangan output low level ( UQL ) mempunyai harga maksimum 0,4 V sedangkan tegangan output high level ( UQH ) mempunyai harga minimum 2,4 V. Dengan dasar di atas didapatkan daerah tegangan Output dan Input Output Q UQmin 0V + 2,4 V Teknik Mikroprosessor Input I UQmax UImin + 0,4 V L 0V +5V H +2V 53 UImax + 0,8 V +5V Sinyal Logik Keterangan : UQLmin : Tegangan Output Minimum pada Low-Level UQLmax : Tegangan Output Maksimum pada Low-Level UQHmin : Tegangan Input Minimum pada High-Level UQHmax : Tegangan Input Maksimum pada High-Level Sebagai acuan dalam menganalisa level logik kali ini diambil IC standard yaitu standard inverter 7404 +5 V 4k 1,6k 125 +5 V 14 13 12 11 1 10 9 1 T3 8 1 D1 I 1 1 1 2 3 T1 1 4 5 6 T2 Q 7 T4 D1 1k Kaki Inverter 7404 Rangkaian Sebuah Inverter 7404 Sinyal L pada Input : 0 V ≤ UIL ≤ + 0,8 V - IIL ≤ 1,6 mA Transistor T1 mendapatkan arus melalui +5V tahanan UIL 1 pada UIH= + 0,4 V 4k yang membuat lintasan Emitor - Kolektor mempunyai tahanan UQH yang rendah. Tegangan pada kolektor T1 I IL hanya sedikit lebih besar dibandingkan tegangan emitornya, yang berarti bahwa sebagai tegangan input, tegangan kolektor T1 ini tidak cukup untuk membuat T2 = ON (menghantar). Akibat T2 = OFF, transistor T3 memperoleh arus basis yg. cukup dan menghantar dengan sempurna. Transistor T4 mempunyai keadaan yang sebaliknya dengan transistor T3 sehingga T4 dalam keadaan tidak menghantar ( T4 = OFF ), karena pada tahanan 1 k tidak ada arus yang mengalir ( tidak ada tegangan ). Dalam keadaan T3 = ON dan T4 = OFF Teknik Mikroprosessor 54 Sinyal Logik pada output Q terdapat tegangan yang cukup sebagai H Level. Jika beban maksimum yang diijinkan tidak terlampaui, maka tegangan outputnya akan berada pada batas level + 2,4 V ≤ UQH ≤ + 5 V . Sinyal H pada Input : + 2 V ≤ UIH ≤ + 5 V IIH ≤ 0,04 mA pada UIH= +2,4 V Transistor T1 sekarang bekerja terbalik +5V oleh karena itu arus akan mengalir UIH 1 melalui " Kolektor - Basis Dioda " T1 UQL menuju ke basis T2 dan akan membuat IIH T2 = ON. Dengan kejadian ini maka T3 = OFF dan T4 = ON sehingga tegangan outputnya akan berada pada batas level 0 V ≤ UQL ≤ + 0,4 V dan mengalir arus IIH masuk menuju input inverter. Sinyal L pada Output : 0 V ≤ UQL ≤ +0,4 V IQL ≤ 16 mA pada UQL= +0,4 V L sinyal pada output, arus maksimum +5V yang diperbolehkan mengalir masuk menuju output adalah IQLmax = 16 mA UIH 1 I QL UQL Sinyal H pada Output : +2,4 V ≤ UQH ≤ +5 V - IQH ≤ 0,4 mA pada UQL= +2,4 V Pernyataan - IQH berarti bahwa arus dari +5V output mengalir keluar ( berlawanan dengan arah arus pada gambar ). H UIL 1 I QH sinyal pada output, arus maksimum yang UQHL diperbolehkan mengalir keluar dari output adalah IQHmax = 0,4 mA. Teknik Mikroprosessor 55 Sinyal Logik 4.1.2. Kemampuan Pembebanan Rangkaian TTL Sinyal output dari sebuah pengirim yang berupa tegangan disambungkan dengan satu atau beberapa input dari penerima. Setiap penerima merupakan beban bagi pengirimyang akan mempengaruhi tegangan keluarannya. Semakin banyak rangkaian penerima yang disambungkan pada output dari pengirim semakin besar pengaruhnya terhadap tegangan outputnya. PENERIMA I1 1 Q1 1 Q2 1 Q3 1 Q4 1 QN I2 PENGIRIM I3 1 7400 I4 IN Kejadian 1 : L sinyal pada output pengirim = L sinyal pada semua Input penerima Dalam kejadian ini berlaku batasan, IQL ≤ 16 mA dan - IIL ≤ 1,6 mA Dari setiap input penerima mengalir arus IIL ≤ 1,6 mA keluar menuju output pengirim. Arus yang diperbolehkan mengalir menuju output pengirim sebesar IQL ≤ 16 mA. Dari dua pernyataan ini dapat dimengerti bahwa sampai 10 buah penerima dapat dilayani dengan sebuah pengirim ( 16 mA : 1,6 mA = 10 ). Kejadian 2 : H sinyal pada output pengirim = H sinyal pada semua Input penerima Dalam kejadian ini berlaku batasan, - IQH ≤ 0,4 mA Teknik Mikroprosessor dan 56 IIH ≤ 0,04 mA Sinyal Logik Arus sebesar IIH ≤ 0,04 mA masuk menuju masing-masing penerima, sedangkan pada saat yang sama berlaku batasan bahwa arus yang diperbolehkan mengalir keluar dari pengirim IQH ≤ 0,4 mA. Dengan cara yang sama didapatkan juga 10 penerima dapat dilayani oleh satu pengirim. Faktor atau angka 10 ini berlaku untuk seluruh gerbang ( IC ) TTL seri 74xx dengan output standard dan dinyatakan sebagai Faktor Pembebanan Output FQ = 10 ( FQ = FAN-OUT ). Selain Fan-Out terdapat juga Faktor Pembebanan Input FI =1 ( FI = FAN-IN ). Dari seluruh penjelasan di atas, dengan mudah dan tanpa perhitungan yang rumit dapat dihindari pembebanan suatu output pengirim yang berlebihan agar diperoleh Level Logik yang diinginkan. 4.1.3. Famili Logik Ada dua dasar teknologi pembuatan IC digital yaitu Bipolar dan MOS (Metal Oxid Semiconductor) teknik. Famili logik adalah sekelompok komponen yang kompatibel secara level dan tegangan sumber. Kompatibel berarti bahwa kita dapat menghubungkan output dari salah satu komponen ke input komponen yang lain atau sebaliknya. Bipolar teknologi mempunyai kecepatan yang lebih karena terdiri dari SSI (Smal Scale Integration, < dari 12 Gerbang dalam chip yang sama) dan MSI (Medium Scale Integration, 12-100 Gerbang dalam chip yang sama) sedangkan MOS teknologi terdiri dari LSI (Last Scale Integration > dari 100 Gerbang dlm. chip yang sama) tetapi untuk ukuran chip yang sama dapat dibangun lebih banyak gerbang di dalamnya. 4.1.3.1. Famili Bipolar Yang termasuk dalam katagori famili bipolar adalah RTL ( Resistor Transistor Logik ), DTL ( Dioda Transistor Logik ), TTL ( Transistor Transistor Logik ) dan ECL ( Emitter Coupled Logik ). Jika level H ada pada U1 atau U2 maka 3,6 V transistor 1,5 k menghantar yang bersangkutan akan dan pada output akan berlogika L. Output akan berlogika H 3,6 k 3,6 k T1 U1 UQ T2 U2 hanya jika kedua inputnya berlogika L, dan fungsi yang demikian adalah fungsi NOR. Rangkai RTL ini untuk masa RTL Gerbang NOR Typ MC 717 Teknik Mikroprosessor sekarang sudah tidak disukai lagi 57 Sinyal Logik 5V Arus basis pada 5V T1 melalu tahanan R2 akan timbul jika D1 5k 2k dan D2 tidak menghantar atau semua inputnya pada kondisi H. D1 D3 Dalam 5k ini T1 menghantar ( T1 = ON ) dan U1 U2 keadaan UQ T1 R2 tegangan outputnya berlogika L. D2 Jika salah satu input dari D1 atau D2 berlogika L maka T2 = OFF dan tegangan outputnya DTL Gerbang NAND Typ MC 849 berlogika H. Jika semua input +5 V 4k R1 1,6k 130 mengalir arus dari R1 melalui dioda pelalu " Basis - Kolektor T4 Dioda " T1, menuju basis T2 dan D T2 T1 mempunyai level sinyal H, maka UQ membuat T2 = ON yg. diikuti juga oleh T3 = ON. Keadaan ini U1 T3 U2 menyebabkan 1k sinyal output berlogika L . Salah satu dari input T1 berlogika L sinyal output akan berlogika H. T2 dan T3 TTL Gerbang NAND Typ 7400 membentuk penguat deferensial. R2 220 220 Pada basis T3 melalui pembagi tegangan membentuk Vref. Jika T4 T5 semua input berlogika L, T1 dan T1 UQ1 T2 T3 Vref melalui T3 dan pd. R2 timbul U1 UQ2 U2 780 510 T2 = OFF. Arus emitor mengalir 510 tegangan mengakibatkan UQ1 berlogika L dan UQ2 berlogika H. Jika salah satu input berlogika H - 5,2 V keadaan output akan berbalik. ECL Gerbang NOR-OR Typ MC 10102 4.1.3.2. Famili MOS Teknik Mikroprosessor 58 Sinyal Logik Yang termasuk dalam katagori famili MOS adalah PMOS ( p-Chanel MOSFETs ) , NMOS ( n-Chanel MOSFETs ) dan CMOS ( Complementary MOSFETs ). Sinyal L pada U1 VDD T1p U1 • T1p menghantar ( T1p = ON ) • T1n tidak menghantar ( T1n = OFF ) Sinyal H pada U1 T2p U2 • T1p tidak menghantar ( T1p = OFF ) • T1n menghantar ( T1n = ON ) Keadaan di atas berlaku juga untuk U2. T1n T2n UQ Jika kedua input berlogika L, maka T1p dan T2p = ON, sedangkan T1n dan T2p = OFF sehingga tegangan output UQ sama CMOS Gerbang NOR VGG = 12 V dengan VDD atau berlogika H VDD = 5 V Gerbang NMOS - NOR disamping hampir T3 mirip dengan rangkaian RTL di atas Jika Salah satu input berlogika H , maka tegangan outputnya akan berlogika L. T1 U1 Sedangkan T2 UQ berlogika Tegangan H apabila output semua akan inputny berlogika L U2 -5V NMOS Gerbang NOR Teknik Mikroprosessor 59 Sinyal Logik 4.2. Perubah Level dan Sakelar Pada sebuah sistem yang dibangun dari gabungan rangkaian antara NMOS (komponen-komponen mikrokomputer ) dengan hardware lain dari komponen TTL akan timbul permasalahan, karena NMOS yang mempunyai tahanan output besar hanya dapat mengendalikan sebuah input TTL. Dari permasalahan ini diharapkan ada driver yang dapat membantu keperluan di atas. Driver atau inverter NMOS yang dimaksud adalah gerbang 4050 dan 4041. Dengan driver ini dapat mengendalikan sampai 2 input TTL yang jika disambung secara langsung tidak mungkin. UB I1 1 Q1 I2 1 Q2 I3 1 Q3 I4 1 Q4 I5 1 Q5 I6 1 Q6 UB Q1 Q6 I1 Q2 I2 I6 6x DRIVER Q5 Q3 I5 I3 Q4 I4 GERBANG C-MOS 4050 Komponen 4050 mempunyai 6 driver bukan inverter, sedangkan komponen 4041 mempunyai 4 kelompok driver yang masing-msaing mempuyai sebuah output inverter dan sebuah output bukan inverter. UB I1 I2 I3 I4 1 1 1 1 1 1 1 1 Q1 Q1 UB Q1 Q1 I4 Q2 I1 Q4 4x BUFFER Q2 Q2 Q3 Q2 I3 Q3 I2 Q3 Q4 Q4 Q3 Q4 GERBANG C-MOS 4041 Teknik Mikroprosessor 60 Sinyal Logik Dalam hal-hal tertentu diperlukan juga suatu komponen yang tidak hanya dapat bekerja dengan sinyal digital tetapi dibutuhkan juga komponen yang dapat bekerja dengan sinyal analog. Prinsip ini dapat dibayangkan seperti halnya pada sebuah sakelar yang bekerja berdasarkan fungsi ON-OFF, salah satu komponen yang dimaksud adalah komponen C-MOS 4066. UB E1 Y1 Z1 E2 Y2 Z1 E1 Y2 Z3 E4 Y4 UB Z2 Z2 E3 Y3 Y1 E4 SAKELAR ANALOG Y4 E2 Z4 E3 Z3 Y3 Z4 GERBANG C-MOS 4066 Lintasan Y - Z adalah lintasan sinyal analog dan juga sinyal digital, sedangkan input E adalah pengatur lintasan agar lintasan Y - Z dapat menghantar ( ON ) atau tidak menghantar ( OFF ). Sinyal pengatur pada input E adalah sinyal digital yaitu "1" artinya ON sedangkan "0" artinya OFF. Seperti halnya sakelar biasa, lintasan Y - Z adalah lintasan dua arah sehingga baik Y atau Z dapat difungsikan sebagai input atau output ( bisa lintasan Y - Z atau lintasan Z - Y ). Dalam keadaan menghantar lintasan Y - Z mempunyai tahanan antara 30 - 100 Ω sedangkan dalam keadaan tidak mengantar mempunyai tahanan kira-kira 10 MΩ. Teknik Mikroprosessor 61 Sinyal Logik LATIHAN 1 Perhatikan gambar di bawah ini +5 V 4k 1,6k 125 +5V T3 D1 I T2 T1 UIL 1 Q UQH I IL T4 D1 1k Jelaskan keadaan T1, T2, T3 dan T4 pada saat sinyal L pada INPUT Lihat Halaman 54 2 +5 V 4k 1,6k 125 +5V T3 D1 I T2 T1 UIH 1 Q UQL IIH T4 D1 1k Jelaskan keadaan T1, T2, T3 dan T4 pada saat sinyal H pada INPUT Lihat Halaman 55 3 Hitunglah Faktor Pembebanan ( FAN-OUT ) untuk gerbang standard TTL 10 Teknik Mikroprosessor 62 Sinyal Logik