abstrak - Universitas Hasanuddin

advertisement

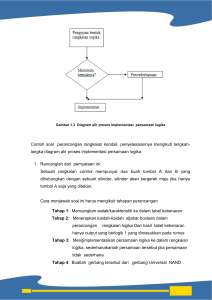

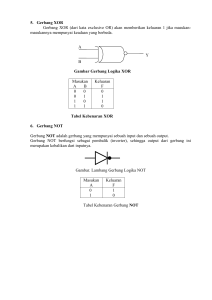

MAKALAH PERANCANGAN SISTEM DIGITAL DOSEN : IR. H. TAHIR ALI TAMPILAN HURUF “ d I G I t a L” PADA SEVENT SEGMNET DENGAN KONFIGURASI GERBANG LOGIKA OLEH NAMA STB. :DIDMAN : D41104730 - 1 R. JURUSAN TEKNIK ELEKTRO TELEKOMUNIKASI FAKULTAS TEKNIK PROGRAM NON REGULAR UNIVERSITAS HASANUDDIN I. ABSTRAK Tampilan huruf “ d I G I t a L “ pada sevent segment adalah suatu contoh perancangan sistem digital dengan menggunakan Electronics Workbench (EWB) sebagai edia simulasi rangkaian. Rancangan ini merupakan aplikasi dari Gerbang Logika yang dikonfigurasi sedemikian rupa dari suatu output yang diinginkan untuk menampilkan karakter huruf “ d I G I t a L “ pada sevent segment secara bergantian. Dari hasil perancangan ini digunakan sebuah IC Counter yaitu Decade Counter yang dipicu oleh Clock yang dibangkitkan oleh Generator Clock. Output counter akan terhubung dengan konfigurasi Gerbang Logika yang telah disesuaikan dengan output yang diinginkan pada sevent segment, sehingga akan menampilkan karakter huruf “ d I G I t a L “. II. PERANCANGAN RANGKAIAN Untuk menghasilkan output tampilan huruf “ d I G I t a L “ pada sevent segment, maka sebelum merancang rangkain perlu dibuat blok diagram yang menggambarkan secara keseluruhan rangkaian yang akan dibuat. INPUTCLOCK CLOCK INPUT DECADE DECADE COUNTER COUNTER RANGKAIAN RANGKAIAN GERBANG GERBANG LOGIKA LOGIKA Gambar II.1. Blok Diagram Rangkaian SEVENT SEVENT SEGMENT SEGMENT II.1. INPUT CLOCK Input clock dalam rangkaian ini berfungsi untuk memberikan/mensuplay Clock yang akan memicu IC Counter untuk dapat berfungsi dengan baik. Input clock dapat bersumber dari Generator Clock atau Function Generator. Dalam perancangan ini digunakan Generator Clock dengan output 1 Hz, tetapi dapat pula diatur sesuai dengan keinginan kita. Besarnya Frekuensi Generator Clock menentukan delay time untuk perubahan satu kode desimal. T 1 1 , f 1Hz , T 1Sc f 1Hz Jadi setiap satu detik, huruf pada sevent segment akan berubah. Untuk membuat waktu tunda lama, maka digunakan frekuensi clock yang lebih kecil. II.2. DECADE COUNTER Counter merupakan rangkaian pencacah yang menanggapi setiap perubahan clock atau suatu rangkaian logika kombinasional yang mampu mengubah bilangan biner (BCD) ke dalam bentuk decimal. Dalam perancangan ini digunakan counter jenis Decade Counter atau BCD Counter Tipe 7490 dimana output 4 biner dengan jumlah desimal 9 atau sampai clock 10 sehingga biasa disebut Counter Modulus – 10. Gambar II.2. IC Decade Counter 7490 II.3. GERBANG LOGIKA Konfigurasi Gerbang Logika untuk membuat tampilan huruf “ d I G I t a L “ pada sevent segment dihasilkan dari beberapa tahap perancangan. II.3.1. Membuat Tabel Kebenaran Tabel kebenaran yang dimaksud adalah output yang diinginkan untuk setiap huruf yang akan ditampilkan pada sevent segment dengan merepresentasikan sebagai kode biner “1” dan “0”, dimana “1” apabila segment menyala dan “0” apabila tidak menyala. Hal ini dapat dilihat pada table berikut ini. DECI TAMPILAN C B A a b c d e f g 0 D 0 0 0 0 1 1 1 1 0 1 1 I 0 0 1 0 1 1 0 0 0 0 2 G 0 1 0 1 0 1 1 1 1 1 3 I 0 1 1 0 1 1 0 0 0 0 4 T 1 0 0 0 0 0 1 1 1 1 5 A 1 0 1 1 1 1 1 1 0 1 6 L 1 1 0 0 0 0 1 1 1 0 1 1 1 0 0 0 0 0 0 0 MAL 7 Tabel 1. Tabel Kebenaran/ output Sevent Segment Karena IC counter 7490 merupakan counter Mod – 9 yang memiliki Output Binary sampai clock yang ke-9 jadi memungkinkan untuk menampilkan sampai 9 huruf secara bergantian, tetapi yang digunakan dalam perancangan ini hanya 6 huruf dan 1 untuk waktu tunda, selebihnya diabaikan artinya output QD diabaikan, tetapi ini berakibat pada clock ke-8 dan ke-9 akan berulang sama pada clock 0 dan 1, artinya dua huruf pertama akan berulang dua kali. Hal ini bisa diatasi dengan melakukan reset setelah clock ke 7 sehingga secara otomatis akan kembali ke clock awal. II.3.2. Penyederhanaan dengan K-Map Untuk menghindari penggunaan terlalu banyak konfigurasi gerbang logika, maka perlu dilakukan penyederhanaan untuk setiap output segment dari a sampai f dengan metode K-Map. Untk segment a ABC + ABC 1 1 Untuk segment b B C 1 1 1 + 1 Untuk Segment c 1 1 1 1 C + ABC 1 Untuk segment d = e 1 1 1 1 1 A + BC A C + A B C Untuk segment f 1 1 1 AB + AC 1 AC + BC Untuk segment g 1 1 1 Tabel 2. Tabel Penyederhanaan K-Map II.3.3. Membuat Rangkaian gerbang Logika Dari hasil penyederhanaan diatas, menggunakan gerbang logika seperti berikut : diimplementasikan dengan Gambar II.2. Gambar Konfigurasi Gerbang Logika II.4. SEVENT SEGMENT 7 Segment Led adalah display yang terbentuk dari 7 kelompok segment led yang diatur sedemikian rupa sehingga bisa membentuk angka-angka dan beberapa karakter. Sevent segment merupakan konfigurasi 7-segment yang terbuat dari bahan yang mengeluarkan cahaya ketika dilewati oleh arus listrik Gambar II.2. Sevent Segment Sevent segment terdiri dari 2 macam yaitu Common Anoda dan Common Catoda. Dalam perancangan ini digunakan sevent segment common catoda dimana setiap segment akan menyala apabila input anoda diberi arus listrik yang lebih besar dari tegangan dalam dioda yaitu 0,2 volt. III. SIMULASI Untuk keperluan simulasi digunakan Electronics Workbench (EWB) Versi 5.12 dengan rangkain lengkap sebagai berikut : Gambar III.1. Gambar Rangkaian dengan Konfigurasi Gerbang Logika Untuk simulasi bisa hanya digunakan gerbang logika tetapi dalam Aplikasi untuk perancangan Hardware, maka gerbang-gerbang logika tersebut harus digantikan dengan IC (Integrated Circuit) yang merepresentasikan masing- masing gerbang logika yang digunakan. Gambar III.2. Gambar Rangkaian dengan Representasi IC Dalam perancangan ini digunakan 7 Buah IC yaitu AND gate 2 input (7408) 2 buah, OR gate 2 Input (7432) 2 buah, AND gate 3 input (7411) 1 buah, OR gate 3 input (4075) 1 buah dan 1 buah IC inverter (7404). IV. KESIMPILAN DAN SARAN KESIMPULAN Kita dapat merancang sebuah rangkaian menggunakan gerbang logika dengan mengacu kepada output yang diinginkan Rangkaian dengan disimulasikan pada menggunakan gerbang logika bisa langsung Electronics Workbench (EWB) tetapi untuk implementasi pada perancangan Hardware harus digantikan dengan representasi Integrated Circuit (IC) untuk masing-masing gerbang. SARAN Apabila menggunakan counter yang output Clocknya melebihi output tampilan pada sevent segment, maka disarankan untuk melakukan reset pada clock terakhir untuk output yang diinginkan sehingga secara otomatis akan kemabli ke clock awal sehingga tidak terjadi pengulangan karakter tampilan. Untuk menampilkan lebih dari 9 karakter bisa menggunakan counter Modulus 13 atau yang lebih besar lagi, atau membuat rangkaian IC 7490 secara kaskade.