limits vol 5 no2 sept 2009

advertisement

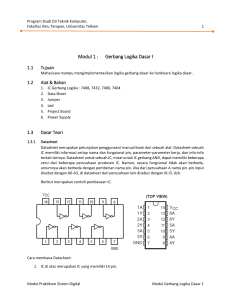

Volume 5 No.2September 2009 Jurnal Ilmiah Fakultas Teknik LIMIT’S Menentukan Jaringan Terpendek Menggunakan Algorithma Prim RiamaSibarani Pengolahan Air LimbahRumahTanggaDenganMetodeSaringanCepat NunungNurhayatidanEndangSupriadi AnalisisKebutuhan (User Requirement Analysis)SistemInformasiPenjualanPadaMalika YS-Net Berbasis Web HernalomSitorusdan T. AdiKurniawan PembuatanTabelKebenaranGerbangLogikaDenganMenggunakan SistemKecerdasanBuatan PertumpunGurusinga PerancanganJaringan Wireless Local Area Network (WLAN) StudiKasusPada PT. MerpatiAlamSemesta (Maskargo) Kiki Kusumawatidan Rudi Anton Volume 5 No.2 Tahun 2009 ISSN 0216-1184 JURNAL ILMIAH FAKULTAS TEKNIK L I M I T’S SUSUNAN REDAKSI PimpinanUmum/PenanggungJawab: Berlin Sitorus, S.Kom.,M.Kom (DekanFakultasTeknik) Staff Ahli: Dr. Ir. Jupiter Sitorus, M.Eng. Dr. YusrianiSaptaDewi, MSi. Dr. IrTambakManurung, MS. Drs. S.H. Hutapea, M.Kom Drs. Edison Sihombing, M.Si PimpinanRedaksi: Dra.PertumpunGurusinga, M.MSi. SekretarisRedaksi: Kiki Kusumawati, ST, MMSi. AnggotaDewanRedaksi: Drs. Charles Situmorang, M.Si. Sukarno BahatNauliSitorus, S.Kom.,M.Kom. Ir. NunungNurhayati, M.Si AgungPriambodo, S.Kom.,M.Kom. HernalomSitorus, ST.,M.Kom. BosarPanjaitan, SSi.,M.Kom. RiamaSibarani, SSi.M.MSi Sekretariat : LinaMursadi, SE AlamatRedaksiPublikasiIlmiah: FakultasTeknik – UniversitasSatya Negara Indonesia Jl. ArteriPondok Indah No. 11 Jakarta Selatan 12240 Indonesia Telp. (021) 7398393, Fax: (021) 7200352 http://www.usni.ac.id DAFTAR ISI MenentukanJaringanTerpendekMenggunakanAlgorithma Prim 1 - 12 RiamaSibarani Pengolahan Air LimbahRumahTanggaDenganMetodeSaringanCepat 13 – 19 NunungNurhayatidanEndangSupriadi AnalisisKebutuhan (User Requirement Analysis) SistemInformasiPenjualan PadaMalika YS-Net Berbasis Web 20- 35 Hernalom S. dan T. AdiKurniawan PembuatanTabelKebenaranGerbangLogikaDenganMenggunakan SistemKecerdasanBuatan 36 – 42 PertumpunGurusinga PerancanganJaringan Wireless Local Area Network (WLAN) StudiKasus PadaPT.MerpatiAlamSemesta (Maskargo) Kiki Kusumawatidan Rudi Anton 43 – 54 PEMBUATAN TABEL KEBENARAN GERBANG LOGIKA DENGAN MENGGUNAKAN SISTEM KECERDASAN BUATAN Pertumpun Gurusinga Program Studi Sistem Informasi, Fakultas Teknik Universitas Satya Negara Indonesia e-mail [email protected] Abstrak Gerbang Logika adalah suatu metode penyederhanaan suatu rangkaian logika(digital) dengan menggunakan tabel kebenaran dari input menjadi output. Penyederhanaan tersebut lebih dulu dilakukan dengan membuat rangkaian ekivalen, sehingga rangkaian yang rumit besar dapat diatasi dengan rangkaian ekivalen tersebut. Tulisan ini membuat tabel kebenaran rangkaian logika AND, OR,NOT, NAND, NOR, EXOR DAN EXNOR dengan menggunakan system Pakar yaitu dengan diagram arus (flowchart) Abstract Spandrel Logic [is] a[n moderation method a[n network of logical to digital by using tables of the truth of from input become output. The simple in advance to conducted by making network of ekivalen, so that big complicated network can overcome with network of ekivalen. This article make the tables of the truth of logic network of AND, OR,NOT, NAND, NOR, EXOR AND of EXNOR by using Expert system that is with current diagram ( computer flowchart). Key word: Truth Table Pendahuluan Perkembangan ilmu yang mempelajari tentang teknik digital pada dewasa ini adalah sangat marak sekali. Hal ini bisa dilihat dari perkembangan dunia elektronika semakin hari semakin pesat. Sebagai contoh adalah perkembangan di dunia komputer yang hampir tidak pernah berhenti dapat dilihat pada mikroprosessor, 8080, 8086, Z60 sampai dengan Pentium II MMX. Teori teknik digital sangat berperan sekali dalam perkembangan ilmu elektronika tersebut, karena tanpa mengetahui teknik digital tidak akan mungkin dapat diciptakan berbagai jenis chip dengan fungsi beraneka ragam. Teori teknik digital dapat pula disebut akar dari ilmu eletronika hal ini disebabkan karena tidak ada satupun rangkaian elektronika yang tanpa menggunakan ilmu teknik digital. Dalam pembuatan suatu rangkaian elektronika atau pembuatan chip yang nantinya dapat berfungsi sebagaimana yang diharapkan oleh sang perancang, maka hal pertama yang harus dilakukan dalam ilmu rangkaian digital adalah membuat suatu tabel kebenaran atau tabel logika dengan input dan output sesuai dengan yang diharapkan, Semakin komplek permasalahan yang harus dipecahkan dalam suatu Sebagaimana te!ah diuraikan pada pembahasan di atas bahwa pembuatan tabel kebenaran adalah hal sangat yang berperan dalam pembuatan rangkaian elektronika. Semakin komplek permasalahan yang harus dipecahkan dalam suatu rangkaian maka akan semakin komplek dan rumit dalam pembuatan tabel kebenarannya. Metode Penulisan Metode penulisan yang penulis gunakan adalah metode penulisan Deskriptif, di mana penulisan dimungkinkan untuk menggambarkan situasi yang terjadi melalui dokumen yang tertulis dari kepustakaan, seperti buku, artikel, jurnal (e-journal), majalah situs internet, dan sebagainya LANDASAN TEORI 1. Pengertian Artifical Intelegence Artifical lntelegence atau kecerdasan buatan dapat didefinisikan sebagai cabang sains komputer yang mempelajari otomatisasi tingkah laku cerdas (inte!igence). Karena itu kecerdasan buatan harus didasarkan pada prinsip-prinsip teorikal dan terapan yang menyangkut struktur data digunakan dalan reprensentasi pengetahuan (knowledge representaion), algoritma yang diperlukan dalam penerapan pengetahuan itu, serta teknik-teknik bahasa dan program yang dipakai dalam implementasinya. Beberapa persoalan yang dipecahkan oleh kecerdasan buatan adalah pembuktian suatu teorema dan permainan (game), pemecahan problema umum persepsi (vison dan percakapan), pemahaman bahasa alamiah, pemecahan problema pakar (expert) dan lain sebagainya. Teknik yang digunakan dalam kecerdasaan buatan memungkinkan dibuatnya sebuah program yang setiap bagiannya mengandung langkahlangkah independent dan dapat didefinisikan dengan baik untuk dapat memecahkan sebuah atau sejumlah persoalan. Setiap potong bagian program adalah seperti sepotong informasi dalam pikiran manusia. Jika informasi tadi diabaikan, pikiran secara otomatis dapat mengatur cara kerjanya untuk menyesuaikaan diri dengan fakta atau informasi yang baru itu. Kita tidak perlu selalu mengingat setiap potong informasi yang telah kita pelajari. Hanya yang relevan dengan persoalan yang kita hadapilah yang kita gunakan. Demikian pula pada kecerdasan buatan, setiap potong bagian program kecerdasan buatan dapat dimodifikasi tanpa mempengaruhi struktur seluruh programnya. Gerbang Logika Gerbang logika sering disebut sebagai rangkaian pintu (gate circuits) yang di dalamnya terdapat berbagai blok pintu logika dan dapat membentuk suatu rangkaian logika dengan hasil atau keluaran sesuai yang kita harapkan. Blok-blok pintu logika tersebut antara lain: gerbang AND, NOT, OR, NAND, NOR yang akan diuraikan pada pembahasan berikut ini. Nilai kebenaran dari suatu gerbang biasanya disimbolkan dengan istilah On dan Off, pada penulisan makalah ini On disimbolkan dengan angka 1 (satu) sedangkan Off disimbolkan dengan angka 0 (nol ). GerbangAND Gerbang AND disebut juga sebagai pintu DAN. Gambar dari gerbang AND adalah sebagai berikut: P Q F Gambar 1 Gerbang AND Rumus F = P * Q P dan Q adalah masukan, sedangkan F adalah keluaran, F akan bernilai 1 (satu) jika dan hanya jika nilai P dan Q adalah 1 (satu). Tabel kebenaran dari gerbang AND adalah sebagai berikut: Tabel 1 Tabel kebenaran gerbang AND Gerbang OR Gerbang OR disebut juga sebagai pintu ATAU. Gambar gerbang OR adalah sebagai berikut: Gambar 2 Gerbang OR P dan Q adalah masukan, sedangkan F adalah keluaran, F akan bernilai 1 (satu) jika nilai P dan Q adalah 1 (satu) atau ke dua masukan adalah 1 (satu). Tabel 2 Tabel Kebenaran gerbang OR Gerbang NOT Gerbang NOT disebut juga sebagai pintu TlDAK. Gambar dari gerbang NOT adalah seperti gambar 3 berikut: Gambar 3 Gerbang Not(Inverter) P adalah masukan, sedangkan Q adalah keluaran, Q akan bernilai 1 (satu) jika salah satu nilai P dalah 0 (noI) atau sebaliknya P bernilai 1 (satu) maka Q bernilai 0 (nol). Tabe! kebenaran dari gerbang OR adalah seperti tabel 3 berikut: Tabel 3 Tabel Kebenaran Gerbang NOT Gerbang NAND Gerbang NAND adalah merupakan gabungan dari dua buah gerbang logika yaitu NOT dan AND sehingga gerbang NAND disebut juga sebagai pintu TIDAK DAN. Gambar dari gerbang NAND adalah sebagai seperti gambar 4 berikut: P Q F Gambar 4a Gerbang NAND dengan Not Gambar di atas dapat disederhanakan menjadi sebagai berikut: P Q F Gambar 4 a dan 4b Gerbang NAND yang lain P dan Q adalah masukan, sedangkan F adalah keluaran, F akan bernilai o(nol) jika dan hanya jika nilai P dan Q adalah I (satu). Rumusnya F = P*Q Tabel kebenaran dari gerbang NAND adalah seperti tabel 4 berikut: GerbangNOR Gerbang NOR adalah merupkan gabungan dari dua buah gerbang logika yaitu NOT dan OR sehingga gerbang NOR disebut juga sebagai pintu TIDAK ATAU. Gambar dari gerbang NOR adalah seperti pada gambar 5 berikut: Gambar 5 Gerbang NOR P dan Q adalah masukan, sedangkan F adalah keluaran, F akan bernilai satu jika kedua inputnya adalah 1 (satu) jika dan hanya jika nilai P dan Q adalah 0 (nol). Tabel kebenaran dari gerbang NOR adalah seperti tabel 5 Tabel 5 Tabel kebenaran NOR P 1 1 0 0 Q 1 0 1 0 F 0 0 0 1 PEMBACAAN FUNGSI LOGIKA DENGAN AUTOMATA HINGGA DETERMINISTIK Fungsi logika adalah termasuk suatu besaran kualitatif karena hanya memunyai nilai benar dan salah atau lebih sering dikenal dengan On dan Off serta 0 dan 1. Oleh karena itu pada tulisan ini pembacaan operasi logika dalam suatu fungsi dilaukan dengan cara scanning karakter per karakter dengan menggunakan teknik automata hingga deterministik. Adapun simbolsimbol operasi gerbang lgika telah dituliskan pada uraian di atas, yaitu AND, OR, NOT, NAND, NOR. Perlu diingat operasi ini tidak baku. Sebuah automata hingga deterministik (AHD) terdiri dari 5 tupel yaitu (K, Vt, r, qo, Z) adalah: Himpunan hingga K berisi stata internal atau disingkat dengan Stata. Himpunan hingga Vt berisi simbol input. Sebuah fungsi f : K x Vt ------K merupakan fungsi next state atau fungsi stata berikutnya. Stata awal qo anggota K Himpunan Z subset dari K yang elemennya disebut stat akhir stata penerima. PEMBAHASAN Scanning Fungsi Logika Pada pembahasan di atas telah diuraikan bahwa fungsi logika adalah merupakan besaran kualitatif, karena pada dasarnya hasil dari operasi fungsi logika hanya mengeluarkan pernyataan benar, salah on, off -0 atau 1. Sehingga komputer tidak akan mengenali operasi yang akan dibuat. Oleh karena itu dengan ketetapan simbol operasi logika yang telah ditetapkan di atas maka pembacaan dari fungsi logika harus Proses pembacaan fungsi logika dari suatu input dapat digambarkan dengan suatu digraph seperti pada gambar 6 berikut: Gambar 6 Graph logika PSEUDOCODE Proses selanjutnya setelah flowchart dibuat adalah pembuatan program yang dimulai dengan pembuatan potongan-potongan program yang nantinya bila digabungkan akan menjadi suatu program yang utuh. Potongan-potongan program tersebut sering disebut dengan Pseudocode. Pseudocode dari flowchart tersebut di atas adalah sebagai berikut: Pseudocode program utama Awalx = 0; Awaly = 0; write('Masukkan fungsi logikanya: '); Readln(fungsinya); panjang=len(fungsi); Gotoxy(awalx,awaly); read(nilai awal); For 1=1 to panjang do Begin Read(operasi); if operasi='*' then AND if operasi='+' then OR if operasi='-' then NOT if operasi='#' then NAND If operasi = ‘$’ then NOR End; Endfor Pseudecode AND Begin if nilaiawal= 1 and nilaiakhir= 1 then hasil=1 if nilaiawal= 1 and nilaiakhir=O then hasil=O if nilaiawal=O and nilaiakhir=1 then hasil=O if nlaiawal = 0 and nilai akhir = 0 then hasil = 0 nilai awal = nilai akhir end Pseudecode OR Begin if nilai awal> 1 and nilaiakhir=1 then hasil=1 if nilaiawal= 1 and nilaiakhir=O then hasil=1 if nilaiawal=O and nilaiakhir=1 then hasil=1 if nilaiawal-O and nilaiakhir-O then hasil=O Nilaiawal=hasil; end Pseudecode NAND Begin if nilaiawal> 1 and nilaiakhir>1 then hasil-O if ni1aiawal~ 1 and nilaiakhir-O then hasil~1 if nilaiawal-O and nilaiakhir-1 then hasil> 1 if nilaiawal-O and nilaiakhir-O then hasil-1 Nilaiawalvha.sil; end; Pseudecode NOR Begin if nilaiawalv l and nilaiakhir-s l then hasil--O if nilaiawal> 1 and nilaiakhir-O then hasil> 1 if nilaiawal=O and nilaiakhir=1 then hasil=1 if nilaiawal=O and nilaiakhir=O then hasil=1 Nilaiawal=hasil; end; Pseudecode NOT Begin if nilaiawal>1 then hasil-O if nilaiawalvO then hasil>1 Nilaiawalvhasil; end KESIMPULAN Dengan adanya sistem komputerisasi yang berbasis berbasis artifical yang berguna untuk menentukan atau bahkan dapat membuat suatu suatu tabel kebenaran fungsi logika, maka bagi problema bagi para perancang rangkaian Elektronika dalam menentukan keluaran dari suatu gerbang logika dapat terpecahkan. Bahkan sekarang bukan menjadi suatu permasalahan yang rumit DAFTAR PUSTAKA Sandi Setiawan, artifical Intellegence, Andi Offset Yogyakarta, 1993. Wasito, S., B., Hernawan, B.Sc, Teknik Digital, cetakan ke-7, Karya Utama, 1989. Malvinos and Leach, Prinsip-prinsip dan Penerapan Digital, Terjemahan , Jakarta, 1985. Elaine Rich, Artificallntellegence, McGraw Hill Inc, New York, 1991. Goerge F. Luger, Artifical Itellegence and Design of Expert System, Jhon Wiley, 1988 Samuel C. Lee Rangkaian Digital Dan Rancangan Logika , Terjemahan Erlangga Jakarta 1991