Solusi Ujian Akhir Semester EL2005 Elektronika Senin, 12 Mei 2014

advertisement

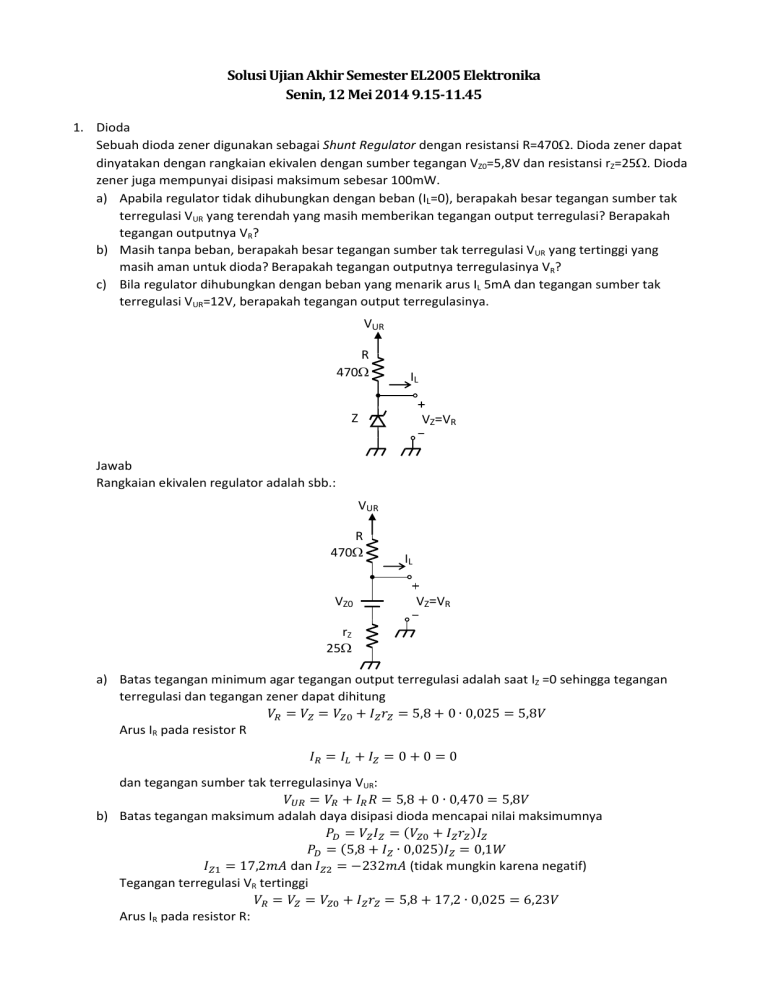

Solusi Ujian Akhir Semester EL2005 Elektronika Senin, 12 Mei 2014 9.15-11.45 1. Dioda Sebuah dioda zener digunakan sebagai Shunt Regulator dengan resistansi R=470. Dioda zener dapat dinyatakan dengan rangkaian ekivalen dengan sumber tegangan VZ0=5,8V dan resistansi rZ=25 Dioda zener juga mempunyai disipasi maksimum sebesar 100mW. a) Apabila regulator tidak dihubungkan dengan beban (IL=0), berapakah besar tegangan sumber tak terregulasi VUR yang terendah yang masih memberikan tegangan output terregulasi? Berapakah tegangan outputnya VR? b) Masih tanpa beban, berapakah besar tegangan sumber tak terregulasi VUR yang tertinggi yang masih aman untuk dioda? Berapakah tegangan outputnya terregulasinya VR? c) Bila regulator dihubungkan dengan beban yang menarik arus IL 5mA dan tegangan sumber tak terregulasi VUR=12V, berapakah tegangan output terregulasinya. VUR R 470 IL Z VZ=VR Jawab Rangkaian ekivalen regulator adalah sbb.: VUR R 470 VZ0 IL VZ=VR rZ 25 a) Batas tegangan minimum agar tegangan output terregulasi adalah saat IZ =0 sehingga tegangan terregulasi dan tegangan zener dapat dihitung Arus IR pada resistor R dan tegangan sumber tak terregulasinya VUR: b) Batas tegangan maksimum adalah daya disipasi dioda mencapai nilai maksimumnya dan Tegangan terregulasi VR tertinggi Arus IR pada resistor R: (tidak mungkin karena negatif) Tegangan sumber takterregulasi VUR: c) Arus IR pada resistor R: dan sehingga Tegangan pada zener atau tegangan output terregulasi VR: 2. MOSFET Semua transistor pada gambar di bawah ini mempunyai |Vt| = 1 V, λ = 0, γ = 0, µnCox = 50 µA/V2, L = 1µm, W = 10µm. Carilah V2 dan I2. Bagaimana perubahan harga-harga ini jika Q3 dan Q4 mempunyai W = 100 µm? +5V +5V Q4 Q2 I2 V2 Q3 Q1 Jawab Q1 dalam keadaan saturasi karena Asumsikan Q2 dalam keadaan saturasi, , maka Karena Q3 dan Q4 mempunyai arus drain yang sama, maka dan Q4 dalam keadaan jenuh. Tegangan maka diperoleh Jika Q3 dan Q4 mempunyai W = 100, , dengan asumsi Q3 atau 3. BJT BJT beroperasi pada IC = 1 mA. Tentukan dan jika = 2 pF dan = 10 pada 50 Mhz. Petunjuk : Jawab Transkonduktansi transistor Penguatan arus dari petunjuk sehingga frekuensi transisi Dari frekuensi transisi diperoleh dapat diperoleh 4. Penguat Daya +VCC iBN iN VBB/2 vI VBB/2 vO iP iL RL iBP -VCC Diketahui rangkaian penguat daya kelas AB seperti pada gambar, dengan nilai arus tanpa sinyal (queiscent current) IQ, tegangan bias total , dengan hubungan: , dan , dan , di mana = 10-13A. Transistor mempunyai penguatan arus =50. Resistansi beban =100. Jika (dan ) berbentuk fungsi sinus, selama setengan siklus positif berlaku hubungan arus . Pada kondisi ini, a) Dalam keadaan tidak ada sinyal, jika = 2 mA, hitung nilai yang dibutuhkan. b) Jika (dan ) berbentuk fungsi sinus, selama setengan siklus positif berlaku hubungan arus . Turunkan hubungan antara , , dan . c) Pada kondisi (b) Buktikan hubungan / persamaan kuadrat: d) Pada kondisi (b), jika nilai maksimum = 12 V, hitung nilai arus beban . e) Hitung harga arus pada keadaan (d) menggunakan hubungan (c). f) Dari hasil (e): Hitung nilai serta arus basis pada kondisi (d) tersebut Jawab a) Dalam keadaan tidak ada sinyal, jika = 2 mA, maka yang dibutuhkan. b) Hubungan antara , c) Dari , dan selama setengan siklus positif: , dapat diturunkan Dari . Substitusi ke persamaan sebelumnya memberikan d) Saat nilai maksimum e) Arus beban f) = 12 V, nilai arus beban . dapat diperoleh dari sehingga diperoleh =-0,32mA (tidak mungkin karena negatif) dan Dari hubungan arus tegangan transistor NPN Diketahui juga =12,32mA. sehingga Arus basis transistor NPN: 5. Rangkaian Logika CMOS Susunlah rangkaian untuk gerbang logika CMOS dengan fungsi . Teknologi yang digunakan menggunakan ukuran geometri minimum 0,25m dengan perbandingan mobilitas elektron n dan holenya p adalah 2:1. Perbandingan ukuran transistor NMOS dan PMOS dipilih untuk memberikan fungsi karakteristik transfer yang simetris dengan panjang kanal minimum. Tentukan dimensi untuk semua transistor yang digunakan. Jawab Fungsi gerbang logika sudah membentuk aoutput active-low untuk rangkaian Pull Down sehingga rangkaian pulldown diperoleh: M3 C M4 D A M1 B M2 Rangkaian Pull-Up diperoleh dengan merangkai rangkaian komplemendari rangkaian Pull-Down sbb.: A M1p C B M3p M2p M4p D Rangkaian lengkap A M1p C B M3p M2p M4p D M3n C M4n D A M1n B M2n Mobilitas elektronn 2 kali lipat mobilitas holep sehingga untuk prototip inverter lebar transistor PMOS Wp dua kali lebar transistor NMOS Wn. Ukuran geometri transistor NMOS sbb.: Untuk transistor M1n hanya ada satu transistor terhubung ke output, maka M1n L=0,25m dan W=0,25m Untuk transistor M2n, M3n, M4n ada 2 NMOS seri, maka M2n L=0,25m dan W=0,25x2=0,50m M3n L=0,25m dan W=0,25x2=0,50m M4n L=0,25m dan W=0,25x2=0,50m Ukuran geometri transistor PMOS sbb.: Untuk transistor M1p, M3p, M4p ada 3 PMOS seri, maka M1p L=0,25m dan W=0,25x2x3=1,50 m M3p L=0,25m dan W=0,25x2x3=1,50 m M4p L=0,25m dan W=0,25x2x3=1,50 m Untuk transistor M2p setara dengan seri M3p dan M4p, maka M2p L=0,25m dan W=1,50/2=0,75m