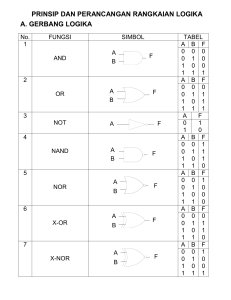

GERBANG-GERBANG DASAR LOGIKA

advertisement