Pekerjaan_Rumah_#06

advertisement

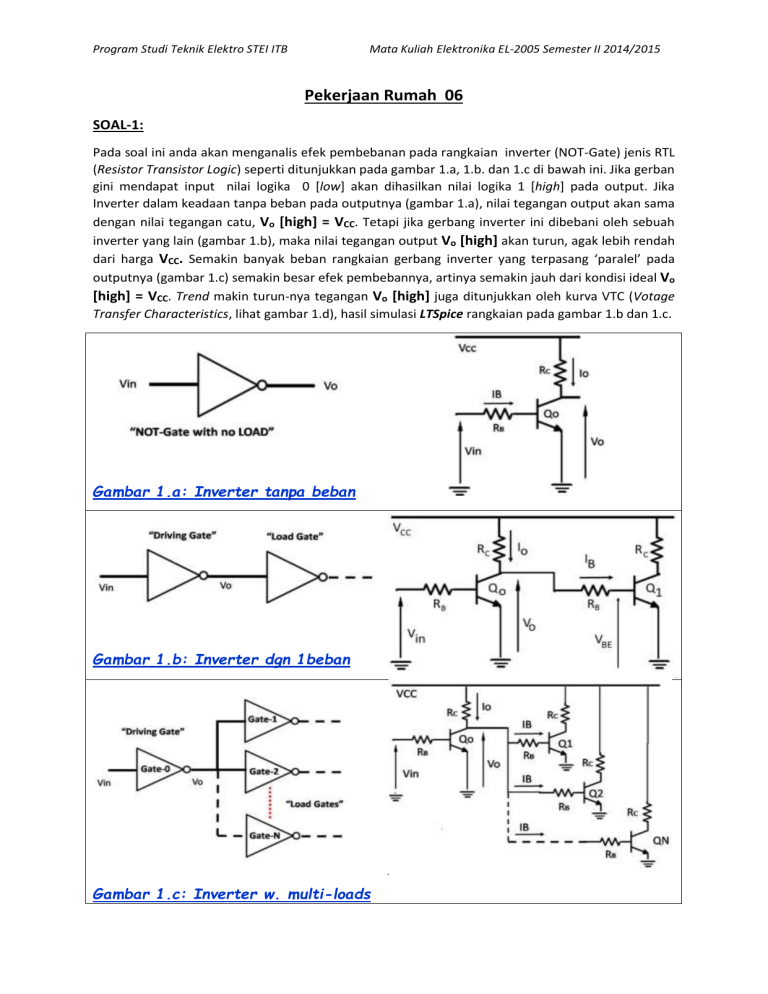

Program Studi Teknik Elektro STEI ITB Mata Kuliah Elektronika EL-2005 Semester II 2014/2015 Pekerjaan Rumah 06 SOAL-1: Pada soal ini anda akan menganalis efek pembebanan pada rangkaian inverter (NOT-Gate) jenis RTL (Resistor Transistor Logic) seperti ditunjukkan pada gambar 1.a, 1.b. dan 1.c di bawah ini. Jika gerban gini mendapat input nilai logika 0 [low] akan dihasilkan nilai logika 1 [high] pada output. Jika Inverter dalam keadaan tanpa beban pada outputnya (gambar 1.a), nilai tegangan output akan sama dengan nilai tegangan catu, Vo [high] = VCC. Tetapi jika gerbang inverter ini dibebani oleh sebuah inverter yang lain (gambar 1.b), maka nilai tegangan output Vo [high] akan turun, agak lebih rendah dari harga VCC. Semakin banyak beban rangkaian gerbang inverter yang terpasang ‘paralel’ pada outputnya (gambar 1.c) semakin besar efek pembebannya, artinya semakin jauh dari kondisi ideal Vo [high] = VCC. Trend makin turun-nya tegangan Vo [high] juga ditunjukkan oleh kurva VTC (Votage Transfer Characteristics, lihat gambar 1.d), hasil simulasi LTSpice rangkaian pada gambar 1.b dan 1.c. Gambar 1.a: Inverter tanpa beban Gambar 1.b: Inverter dgn 1beban Gambar 1.c: Inverter w. multi-loads Program Studi Teknik Elektro STEI ITB Mata Kuliah Elektronika EL-2005 Semester II 2014/2015 Gambar 1.d Efek pembebanan pada Kurva VTC (Voltage Transfer Characteristics) Inverter (a) Perhatikan gambar 1.b di mana nilai VCC = 5V, RC = 1 kΩ, nilai RB = 10 kΩ. Jika output gerbang inverter yang pertama (‘Driving Gate’) dalam keadaan high (logika 1), maka transistor Qo dalam keadaan OFF (open circuit). Arus Io mengalir dari VCC melalui RC transistor Qo, lalu menjadi arus basis transistor Q1: IB , sedemikian rupa, sehingga Q1 berada dalam keadaan jenuh. Jika dalam keadaan saturasi Q1 ini, VBE1 sat = 0.8 V, hitunglah besar arus Io = IB ini, lalu hitung tegangan output gerbang inverter yang pertama, Vo [high]. (b) Ulangi soal (a) dengan nilai VCC, serta RC dan RB yang sama Jika sekarang pada terminal output gerbang inverter terpasang 2 buah gerbang inverter lain yang sama (lihat rangkaian pada gambar 1.c sebagai acuan, tetapi hanya menggunakan dua buah “load-gates”: rangkaian inverter Q1 dan Q2). Ulangi perhitungan Vo [high] dari ‘the driving inverter’ Qo jika sekarang nilai RB dari Q1 dan Q2 diperbesar menjadi RB = 20 kΩ (anggap Q1 dan Q2 tetap dapat mencapai keadaan saturasi). Bandingkan dengan hasil sebelumnya ( jika RB = 10 kΩ ), berikan penjelasan anda. (c) Tinjau gambar 1.c: Berapa jumlah maksimum gerbang inverter beban (load-gates) yang dapat dipasang secara paralel pada output inverter Qo (the ‘Driving Gate’), agar pada kondisi output high (nilai logika 1), degradasi / penurunan tegangan ouput-nya tidak lebih dari 50%, artinya agar Vo [high] ≥ 2.5 V. Untuk ini, lakukan hal berikut: - Kembangkan cara perhitungan anda pada soal 1.b untuk kasus jumlah beban yang lebih umum, misalnya N buah inverter beban (load-gates). Turunkan sebuah rumus umum yang menghubungkan nilai Vo [high] dengan nilai parameter N ini, serta nilai parameter rangkaian lainnya: VCC, RB, RC, dan VBE sat. Dengan menggunakan rumus ini, cobalah secaa bertahap menaikkan harga N, dari N = 1, N = 2, dst hingga dicapai suatu harga kritis Vo [high] = 2.5V atau sedikit lebih tinggi, di mana jika nilai N di naik-kan satu, nilai Vo [high] menjadi lebih rendah dari 2.5V. - Lakukan simulasi menggunakan LTSpice/Winspice untuk mendapatkan dua buah kurva VTC (Voltage Transfer Characteristics) serupa dengan gambar 1.d untuk kasus N = 0 (tanpa beban) dan N = ...? (sesuai Jawaban anda pada soal 1.b). Untuk simulasi SPICE ini, gunakan Program Studi Teknik Elektro STEI ITB Mata Kuliah Elektronika EL-2005 Semester II 2014/2015 parameter BJT: IS = 0.1 pA dan BF = 100. Lakukan pengubahan (sweep) tegangan input inverter (‘driving gate’) dari Vin = 0 V hingga Vin = 5 V. Gunakan Excel atau program lain untuk menggambar kuva VTC hasil simulasi LTSpice/Winspice di atas. SOAL-2: Gambar 2 Diagram rangkaian penguat dan kurva IC vs VCE transistor yang digunakan (a) Anda diminta merancang sebuah rangkaian penguat transistor bipolar dengan kurva karakteristik IC vs VCE transistor seperti pada gambar. Pertama, tentukan titik operasi (DC) transistor. Tulis persamaan garis beban dari penguat ini. Gunakan nilai VCC = 15V. Pilihlah nilai DC VCE = ½ VCC. Di inginkan agar garis beban memotong sumbu IC pada niai IC = 50 mA. Hitunglah nilai RC dan gambarlah garis beban ini pada grafik IC vs VCE di atas (super-imposed) (b) Dari persamaan garis beban dan nilai RC di atas, hitung nilai IC. Tunjukkan letak titik operasi (VCE, IC) pada garis beban yang anda gambar di atas. Berdasarkan posisi nilai IC ini dan kurva karakteristik di atas, tentukan ( atau “perkirakan”) nilai IB serta angka penguatan arud transistor, β. Jika diketahui nilai VBB = 5 V, hitung nilai RB. (c) Gambarlah model AC / sinyal-kecil dari rangkaian penguat di atas. Hitunglah nilai parameterparameter rangkaian, kemudian hitungah penguatan tegangana Av = vo / vi. (d) Dengan nilai VBB tetap sama seperti di atas, ubahlah nilai RB agar diperoleh nila IB yang baru = 2x lipat nilai IB sebelumnya, tunjukkan (+/-) letak titik operasi yang baru (VCE, IC) pada grafik. Apa peningkatan kinerja rangkaian penguat yang (mungkin) dapat diperoleh? Sebutkan pula kerugian yang (mungkin) timbul pada kinerja rangkaian! Gunakan gambar kurva IC vs VCE serta garis beban, dan titik operasi yang telah anda gambar sebelumnya (pada soal a dan b) sebagai acuan dalam menjawab. CATATAN: Pada saat menjawab bantuan gambar/grafik, jadi diperoleh suatu harga yang dimungkinkan. Untuk menjawab 2.b di atas, jika perlu dapat soal 2.b dan 2.d, anda menggunakan untuk kedua sub-soal ini tidak harus “eksak”. Variasi harga yang “wajar soal 2.a anda perlu meng-copy gambar diperbesar.