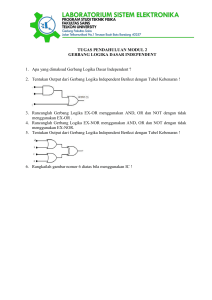

LAPORAN PRAKTIKUM SISTEM DIGITAL MODUL 01 DASAR-DASAR LOGIKA & RANGKAIAN KOMBINASIONAL Asisten Praktikum: Raden Muhammad Faisal Abdul Aziz (15/384857/TK/43519) Praktikan: Davidika Argo Selo Buwono (17/413545/TK/45985) Tanggal Praktikum: Jumat, 29 Maret 2019 LABORATORIUM SENSOR DAN SISTEM TELEKONTROL DEPARTEMEN TEKNIK NUKLIR DAN TEKNIK FISIKA FAKULTAS TEKNIK UNIVERSITAS GADJAH MADA YOGYAKARTA 2019 I. Tujuan 1. 2. 3. 4. 5. Mahasiswa mengenal dasar-dasar logika, operasi-operasi yang berlaku dan teknik matematis yang digunakan untuk menyelesaiakn persoalan-persoalan logika. Mahasiswa mengenal implementasi gerbang-gerbang ke dalam bentuk hardware (IC/ Integrated Circuits). Mahasiswa dapat menjelaskan rangkaian logika secara aljabar dengan menggunakan ekspresi boolean. Mahasiswa dapat mengevaluasi output dari suatu rangkaian logika. Mahasiswa dapat mengimplementasikan rangkaian dari ekspresi boolean. II. Alat dan Bahan 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. Modul Praktikum Project Board IC AND 74xx08 IC OR 74xx32 IC NOT 74xx04 IC NAND 74xx00 IC NOR 74xx02 IC XOR 74xx86 Lampu LED Resistor 330 Ω III. Langkah Kerja Praktikum 1. Menyiapkan project board. 2. Memasang IC yang akan diamati ke project board, diperbolehkan memasang beberapa IC sekaligus. Kemudian, hubungkan kaki Vcc IC ke sumber tegangan +5 Vdc dengan menggunakan kabel/jumper, demikian juga kaki GND dihubungkan ke ground. 3. Menghubungkan input A dan B atau salah satunya (khusus gerbang NOT) ke saklar. 4. Menghubungkan output gerbang ke resistor 330 Ω yang salah satu kakinya telah dihubungkan dengan lampu LED, kaki LED yang lain dihubungkan dengan ground. 5. Membuat rangkaian gerbang logika seperti gambar berikut. Gambar 1. Rangkaian Gerbang Logika. 6. Membuat rangkaian kombinasional yang mengacu pada kedua gambar berikut. Gambar 2. Rangkaian kombinasional 2 input Gambar 3. Rangkaian kombinasional 3 input Gambar 4. Rangkaian kombinasional 3 input oleh asisten praktikum 7. Menyalakan sumber tegangan. Isi tabel dengan angka 1 jika LED menyala dan angka 0 untuk sebaliknya. IV. Hasil Praktikum 1. Rangkaian Gerbang Logika INPUT B A OUTPUT AND 7408 OR 7432 NOT 7404 B 0 0 1 0 0 0 1 1 0 1 0 1 0 1 0 1 1 0 1 1 2. Rangkaian Kombinasional 2 Input INPUT B A 0 0 0 1 1 0 1 1 OUTPUT Y1 Y2 0 1 1 0 1 0 1 1 A NAND 7400 NOR 7402 EX-OR 7486 1 1 1 0 1 0 0 0 0 1 1 0 1 0 1 0 NOTASI 𝑌1 = ((𝐴′ 𝐵). (𝐴𝐵′ )) + (𝐴 + 𝐵) = (𝐴 + 𝐵) 𝑌2 = ((𝐴 + 𝐵′). (𝐴′ + 𝐵)) 3. Rangkaian Kombinasional 3 Input INPUT OUTPUT C B A Y3 Y4 Y5 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 0 0 0 𝑌3 = (((𝐴. 𝐵) + 0 1 1 1 0 1 (𝐴. 𝐶 ′ )). (𝐴 + 𝐶 ′)) = 1 0 0 0 0 1 𝐴. (𝐵 + 𝐶 ′ ) 1 0 1 0 0 1 1 1 0 0 0 1 1 1 1 1 0 1 NOTASI 𝑌4 = (((𝐴. 𝐵). (𝐴′ + 𝐵′ )). (𝐵 + 𝐶 )) =0 𝑌5 = (𝐴. 𝐵. (𝐴′ + 𝐶) + 𝐶 = (𝐴. 𝐵) + 𝐶 V. Pembahasan Praktikum Gambar 5. Gerbang Logika Dasar Pada praktikum ini, gerbang-gerbang logika yang digunakan dikemas dalam suatu IC (integrated circuits). Jenis IC yang digunakan adalah jenis TTL, yaitu IC yang membutuhkan catu tegangan sebesar +5 Vdc ± 10%. Keluarga IC TTL ditandai dengan awalan angka 74 atau 54. Label xx menunjukkan class and price. Seperti pada gambar 5: IC 74xx08 digunakan untuk gerbang AND IC 74xx32 digunakan untuk gerbang OR IC 74xx04 digunakan untuk gerbang NOT IC 74xx00 digunakan untuk gerbang NAND IC 74xx02 digunakan untuk gerbang NOR IC 74xx86 digunakan untuk gerbang EX-OR Pada semua jenis IC TTL inputan VDC dan GND ada pada kaki 14 dan 7. Kemudian, terdapat perbedaan pada nomor-nomor kaki inputan dan outputan sinyal logika IC gerbang NOT dan gerbang NOR. Sedangkan untuk IC yang lalin memiliki penomoran kaki yang sama. Pada percobaan pertama praktikum ini, yaitu menguji nilai input dan output masing-masing gerbang logika. Pengujian dilakukan dengan menyusun rangkaian seperti pada Gambar 1. Didapati hasil yang sesuai dengan teori. Pada gerbang logika AND, output bernilai satu saat kedua input bernilai satu. Pada gerbang logika OR, output bernilai satu saat salah satu input atau keduanya bernilai satu. Pada gerbang logika NOT, maka akan dihasilkan output yang merupakan invers dari inputnya sendiri. Untuk gerbang logika NAND, output bernilai nol ketika kedua inputnya bernilai satu. Pada gerbang logika NOR, output bernilai jika kedua input bernilai nol. Dan pada gerbang logika EX-OR, output bernilai satu ketika salah satu input bernilai satu. Pada percobaan kedua pada praktikum ini, rangkaian yang digunakan sesuai pada Gambar 2. Output yang dihasilkan antara teori dengan hasil praktikum adalah sama untuk semua input. Pada Y1: Y1 = (A’B)(AB’) + A + B Dengan Hukum Komplemen. Y1 = 0 + A + B 𝑌1 = (𝐴+𝐵) Gambar 6. Rangkaian Y1 paling sederhana. Output rangkaian Y1 akan bernilai satu apabila salah satu atau kedua input bernilai satu. Pada Y2: 𝑌2 = (A+B’)(A’+B) Rangkaian sudah paling sederhana. Gambar 7. Rangkaian Y2 paling sederhana. Pada Y2, output akan bernilai nol apabila salah satu input bernilai satu, dan akan bernilai satu ketika kedua output bernilai nol atau bernilai satu. Pada percobaan ketiga dengan tiga input, dibuat tiga rangkaian seperti pada Gambar 3 dan Gambar 4. Untuk Y3: Y3 = ((AB)+(AC’))(A+C’) Dengan Hukum Distributif. Y3 = (B+C’)A(A+C’) Dengan Hukum Penyerapan. Y3 = A(B+C’) Gambar 8. Rangkaian Y3 paling sederhana. Antara output berdasarkan teori dan hasil praktikum dimana menunjukkan output yang bernilai satu saat input bernilai satu pada kabel A saja, A dan B saja, maupun semua ketiganya A , B, dan C. Untuk Y4: Y4 = (AB(A’+B’))(B+C) Dengan Hukum De Morgan. Y4 = (AB)(AB)’(B+C) Dengan Hukum Komplemen. Y4 = 0.0.(B+C) Dengan Hukum Dominasi. Y4 = 0 Gambar 9. Rangkaian Y4 paling sederhana Pada Y4, menurut hasil teori, output bernilai nol untuk semua nilai input dan hal ini sesuai dengan hasil praktikum. Untuk Y5: Y5 = AB(A’+C’) + C Dengan Hukum Distributif. Y5 = ABA’ + ABC’ + C Dengan Hukum Komplemen. Y5 = 0 + ABC’ + C Dengan Hukum Reduksi. Y5 = AB+C Gambar 10. Rangkaian Y5 paling sederhana. Pada rangkaian ini, nilai output nol didapatkan saat ketiga kabel bernilai nol, maupun antara A dan B salah satu bernilai nol dan kabel C pasti bernilai nol. VI. Kesimpulan Dari praktikum ini, didapatkan kesimpulan sebagai berikut. 1. Operasi-operasi dasar logika adalah operasi INVERS, AND, dan OR. 2. Terdapat beberapa gerbang logika dasar berdasarkan seri dari ICnya, antara lain gerbang logika NOT, AND, OR, NOR, NAND, EX-OR dimana gerbang logika tersebut memiliki ekspresi Boolean sendiri-sendiri. 3. Gerbang-gerbang logika dapat dikombinasikan untuk membuat suatu rangkaian. Kemudian dengan menggunakan aljabar Boolean, rangkaian dapat disederhanakan dengan hukum-hukum Aljabar Boolean. VII. Daftar Pustaka Sunarno. 2018. Modul 1 praktikum sistem digital. Yogyakarta: Lab SSTK DTNTF FTUGM. LAMPIRAN