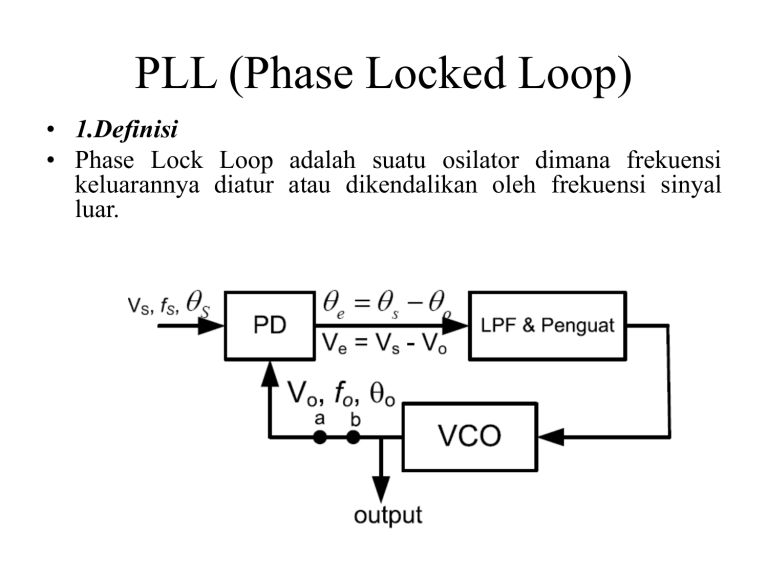

VCO

advertisement

PLL (Phase Locked Loop) • 1.Definisi • Phase Lock Loop adalah suatu osilator dimana frekuensi keluarannya diatur atau dikendalikan oleh frekuensi sinyal luar. 2.Prinsip kerja • Loop dalam keadaan “terkunci“ jika frekuensi sinyal terkunci masukan (referensi) dan frekuensi VCO identik (fS = fO); • Serta beda fasa relatif θe = θs – θo, ditentukan oleh karakteristik detektor fasa dan oleh penyimpangan fS dari frekuensi free running ff (yang didefenisikan dengan tegangan kendali Vd = 0) dari VCO. • Kalau sinyal masuk mempunyai fS = ff , tegangan kendali ke VCO akan tetap sama dengan nol. Fasa θo dari VCO akan mengatur sendiri untuk menghasilkan beda fasa θe = θs – θo, yang akan menghasilkan keluaran nol pada detektor fasa (θe = 0, θs = θo). Sudut θe mungkin 90° atau 180°, tergantung pada jenis rangkaian detektor fasa. • Jika frekuensi masuk berubah sehingga fs ≠ ff, beda fasa θe harus cukup berubah untuk menghasilkan kendali Vd tegangan yang akan menggeser frekuensi VCO ke fo=fs. Daerah frekuensi yang dimungkinkan oleh pengendalian tersebut merupakan fungsi dari komponen–komponen loop. • Suatu pembagi frekuensi yang dapat dipilih dapat disisipkan ke dalam loop antara titik a dan b. Kalau perbandingan pembagi sama dengan n, frekuensi VCO fo - n.fs tetapi tegangan/fasa yang diumpanbalikkan ke detektor fasa mempunyai fasa = θo. Dengan ini berarti VCO dapat membangkitkan kelipatan frekuensi masuk dengan hubungan fasa yang teliti antara dua tegangan. 3.Jenis Detektor Phasa: Sinusoidal Detektor Phasa: Ve = kd sin θe, dimana θe = θs – θo jika : θe <<Ve, Ve = kd.θe, kd = Ve/ θe dimana Kd = konstanta detektor fasa (Volt / rad) jika fasa masukan dan fasa keluaran berubah terhadap waktu dan frekuensi, maka: dalam domain s (=j2πf) Ve(s) = kd.θe(s) Detektor Phasa Segitiga: Ve = 2A / π .θe Kd = Ve / θe = 2A / π jika fasa masukan dan fasa keluaran berubah terhadap waktu dan frekuensi, maka: dalam domain s (=j2πf) Ve(s) = kd.θe(s) Detektor Phasa Gigi gergaji: Ve A kd . e Ve e A volt rad jika fasa masukan dan fasa keluaran berubah terhadap waktu dan frekuensi, maka: (dalam domain s =j2πf) Ve(s) = kd.θe(s) 4.Filter LPF tanpa penguatan (pasif): 5. Filter Lead-Lag: 6. Filter dengan penguat: 7. VCO (Voltage Controled Oscillator): Phasa keluaran VCO: Fasa keluaran VCO, kita lihat sistem PLL: Fungsi Transfer (fasa) Lingkar Terbuka PLL: Asumsi menggunakan Filter tipe nomor 2: Sehingga: Respon alami sistem orde 2: Keterangan gambar: Daerah kuncian/ tracking: Daerah dimana frekuensi free running masih mampu mengejar perubahan frekuensi luar. 8.9. Kegunaan PLL: 8.9.1 Frequency Syntesizer: 8.9.2 Modulator dan Demodulator: 8.9.2.1 PLL sebagai Modulator FM: Langkah-langkah Perancangan PLL (dengan filter lead-lag): Contoh perancangan PLL: Rancanglah PLL jika diinginkan: Overshot 20%, pada settling time: 1ms dengan kriteria 5% dari soal diatas, overshot< 20 % , nilai < 5% dicapai pada saat: asumsi bahwa dihitung pada saat n =25 fo =2,5 MHz, sehingga: kv = 0,5.10.107 / 25 = 0,2.107 Latihan Soal