Kelompok 7 Danu Setiawan 1017041023 Juli Adi Prastyo

advertisement

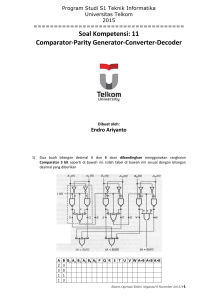

Kelompok 7 Danu Setiawan 1017041023 Juli Adi Prastyo 1017041031 Comparator Rangkaian Comparator adalah satu jenis penerapan rangkaian kombinasional yang mempunyai fungsi utama membandingkan dua data digital. Hasil pembandingan itu adalah, sama, lebih kecil, atau lebih besar. Dari dua data digital yang hanya terdiri dari 1 bit yang dibandingkan, kemudian dapat diperluas menjadi dua data digital yang terdiri dari lebih dari 1 bit seperti dua bit, tiga bit, dst. Komparator banyak digunakan misalnya pada mesin penyeleksi surat, baik ukuran dimensinya, berat surat, kode area (berdasarkan bar-code), dsb. Berikut contoh Gambaran rangkaian komparator 1-bit A>B Comparator 1 bit A= B A<B A B (a) L A E B G (b) Gambar 1. Rangkaian Komparator 1-bit. (a) Rangkaian Jadi, dan (b) Rangkaian dari Gerbang Logika Data angka umumnya paling sedikit terdiri dari dua bit. Namun di dalam bilangan desimal, angka yang terbesar yang dapat diwakili oleh dua bit ini ialah angka 3 (‘11’ dalam sistem biner). Apabila kita ingin membandingkan angka-angka yang lebih besar tentunya sistem pembanding itu tidak dapat digunakan lagi sehingga kita perlu rnerancang sistem yang baru yang sesuai dengan kebutuhan. Jadi setiap ada perubahan untuk membandingkan angka yang lebih besar yang diluar kemampuan sistem pembanding tersebut, kita harus merancangnya lagi. Hal sepertinya tidaklah menguntungkan. Oleh karena itulah kita harus rancang suatu sistem pembanding sedemikian rupa sehingga setiap sistem ini dapat saling dihubungkan satu sama lain untuk membentuk sistem pembanding yang lebih besar. Dengan kata lain, untuk kepentingan pembandingan yang dapat mengakomodasi semua bilangan, maka harus dirancang satu sistem praktis untuk itu. A. Komparator untuk Dua bit data Misalkan kita ingin merancang suatu alat pembanding (comparator) yang akan membandingkan dua angka dan memberkan hasilnya, yaitu angka yang satu lebih kecil, lebih besar, atau sama dengan angka yang satunya. Sistem pembanding ini digambarkan secara garis besar sebagai sebuah kotak hitam yang hanya diketahui fungsinya saja. Kotak hitam dari sistem ini dapat dilihat pada Gambar 2. Sistem pembanding ini mempunyai 2 Input A dan B yang masing-masing terdiri dan 2 bit dan 3 output yang masing-masing terdiri dari 1 bit untuk menunjukkan hasil perbandingan tersebut yaitu, A>B, A<B, dan A=B. Cara kerja sistem ini sangatlah sederhana. Setiap waktu hanya ada satu output yang bernilai BENAR. Output A>B akan bernilai ‘1’ apabila nilai A lebih besar dari B. Demikian juga halnya dengan output A<B dan A=B yang bernilai ‘1’ apabila nilai A lebih kecil dari B dan apabila nilai A sama dengan B. Gambar 3 menggambarkan tabel kebenaran dari sistem ini. Gambar. 2 Diagram blok Comparator Gambar. 3 Tabel kebenaran sistem Komparator Sistem ini akan mempunyai 3 persamaan logika karena adanya 3 output. Oleh karena itu kita akan sederhanakan dan peroleh persamaan logikanya satu persatu. Gambar 4, 5, dan 6 menunjukkan penyederhanaan dan persamaan logika yang di peroleh untuk output-output A > B, A < B, dan A = B. Gambar 4. Persamaan logika untuk A > B Gambar 5. Persamaan logika untuk A < B Gambar 6. Persamaan logika untuk A = B Jika diperhatikan, persamaan logika dari ketiga output tersebut dinyatakan dalam 4 variabel inputnya yaitu A1, A0, B1, dan B0. Hal ini menunjukkan bahwa setiap outputnya tergantung pada input-inputnya. Di dalam mendesain sistem pembanding yang sebenarnya dengan menggunakan komponen-komponen digital, kita ingin berusaha untuk mengurangi jumlah ICs/komponen yang digunakan. Suatu penghematan yang jelas dan mudah di peroleh dengan mengamati persamaan-persamaan logika yang di peroleh adalah dengan adanya kanonical term yang sama di antara persamaan-persamaan logika tersebut. Sebagai contohnya dalam desain sistem pembanding ini ialah kanonikal term A0.A1.B0 yang terdapat pada persamaan logika untuk output A > B dan A < B. Hal ini berarti bahwa hanya satu rangkaian yang perlu dibangun untuk kanonikal term ini sehingga output A > B dan A < B akan menggunakannya bersama. Perlu diingat juga bahwa pada sistem ini hanya akan ada satu output yang akan bernilai BENAR=1 untuk setiap kombinasi inputnya; sebagai contohnya untuk input 01 (A1 & A0) dan 11 (B1 & B0) hanya output A < B yang akan bernilai BENAR=1. Dengan menyadari hal semacam ini, maka akan menolong kita untuk mengetahui apabila sistem tersebut tidak bekerja dengan semestinya misalnya jika output A < B dan A = B memberikan nilai BENAR untuk contoh input di atas tadi. B. Komparator untuk lebih dari Dua bit data Satu sistem pembanding sederhana (hanya 2 bit) telah dibahas pada Bagian A di atas. Tetapi untuk keperluan pembandingan yang lebih dari 2 bit, karena memang kenyataan angka desimal terbesar yang dinyatakan dalam biner adalah angka 3 (‘11’), maka harus dirancang satu komparator lain untuk fungsi pembandingan tersebut. Komparator tersebut mempunyai kotak hitam berbeda dengan Gambar 1, yaitu mempunyai tiga input tambahan, IA<B, IA>B, dan IA=B seperti yang ditunjukkan pada Gambar 7. Ketiga input tambahan ini dimaksudkan untuk dihubungkan ke output dari sistem komparator yang lainnya apabila sebuah sistem pembanding lebih besar ingin dibentuk. Oleh karena itulah, ketiga input tambahan itu disebut sebagai cascading input. Gambar 7. Kotak hitam Komparato yang disempurnakan. Komparator yang ditunjukkan pada Gambar 6 itu adalah untuk membandingkan angka-angka yang besarnya 2 bit saja. Tetapi komparator ini dapat digabungkan untuk membentuk alat pembanding gang lebih besar yang tentunya berukuran kelipatan dari 2. Sebagai contoh, sistem pembanding untuk 6 bit dapat dibentuk dengan menggunakan 3 buah komparator tersebut seperti yang ditunjukkan pada Gambar 8. Sistem pembanding yang paling kanan disebut sebagai LSW (Least Significant Word) dan sistem pembanding yang paling kiri disebut MSW (Most Significant Word). Gambar 8. Komparator 6 bit Perhatikan bahwa ketiga cascading input dari LSW-nya harus diberikan nilai konstan seperti anda dapat lihat pada Gambar 8, yaitu IA>B = 0, IA=B = 1, dan IA<B = 0. Tujuannya ialah untuk menetralkan komparator tersebut sehingga nilai perbandingan pada LSW itu hanya bergantung pada inputnya (A1, A0, B1, dan B0) saja. Sebagai contoh, output A>B dari LSW itu akan bernilai ‘1’ apabila A lebih besar dari B, output A<B = 1, apabila A lebih kecil dari B, dan A=B = 1 apabila A sama dengan B. Tetapi apa yang terjadi kalau cascading input ini tidak diberikan nilai konstan seperti itu. Misalnya apabila nilai konstan dari cascading inputnya adalah IA>B = 1, IA<B = 0, dan IA=B = 0, maka LSW ini akan mengeluarkan output A>B = 1 apabila A sama dengan B. Hal ini karena LSW itu menganggap bahwa nilai dari A yang sebelumnya adalah lebih besar dari B. C. Merancang Komparator dengan komponen baku Marilah kita desain komparator ini yang tentunya kita tahu bahva tabel kebenarannya harus diperoleh terlebih dahulu. Tabel kebenaran untuk komparator ini yang ditunjukkan pada Gambar 8 adalah agak berbeda dengan tabel kebenaran yang sebelumnya, karena tabel ini tidak menggunakan nilai-nilai biner untuk input-input A dan B-nya. Hal ini dimaksudkan untuk mempermudah penganaliaaan operasi dari komparator tersebut sama seperti penggunaan angka desimal dalam teknik Quine-McClusky. Baiklah, sekarang kita bahas bagaimana tabel kebenaran itu diperoleh. Baris pertamanya diperoleh dengan mengingat bahwa apabila A1>B1 maka tidak perduli apa saja nilai dari input-input lainnya; output A>B akan bernilai ‘1’ karena Al dan B1 merupakan MSBnya. Baris-baris yang lainnya dapat mudah dimengerti dengan mengingat apabila dituliskan A1>B1 berarti A1 = 1 dan B1 = 0, A1=B1 berarti A1 sama dengan B1, dan apabila A1<B1 berarti A1 = 0 dan B1 = 1. Perhatikan bahwa tiga baris terakhirnya mempunyai kondisi yang sama, yaitu, A1=B1 dan A0=B0, sehingga outputnya akan tergantung pada nilai dari cascading inputnya. Gambar 9. Tabel kebenaran satu Komparator dengan cascading input. Tanpa perlu menyederhanakannya juga kita peroleh persamaan-persamaan logika untuk semua outputnya sebagai berikut: 1. [A>B] = [A1>B1] + [(A1=B1)•(A0>B0)] + [(A1 =B1)•(A0=B0)•(IA>B)•(IA<B)’•(IA=B)’] 2. [A<B] = [A1<B1] + [(A1=B1)•(A0<B0)] + [(A1=B1)•(A0=B0) )•(IA>B)’•(IA<B)•(IA=B)’] 3. [A=B] = [(A1=B1)•(A0=B0)•(IA>B)’•(IA<B)’•(IA=B)] Seperti kita lihat persamaan-persamaan tersebut di atas masih menggunakan kondisi-kondisi seperti A1>B1 dan lain-lainnya yang harus diimplementasikan dengan menggunakan operator-operator baku atau dasar. Implementasi semua kondisi itu ditunjukkan pada Gambar 9. Dengan mensubstitusikan kondisi-kondisi yang diperoleh pada Gambar 10tersebut, maka persamaan-persamaan itu dapat dituliskan lagi sebagai berikut: (1). [A>B] = [A1.B1’] + [(A1ΘB1)•(A0)•(B0’)] + [(A1ΘB1)•(A0ΘB0)• (IA>B)•(IA<B)’•(IA=B)’] (2). [A<B] = [A1’.B1] + [(A1ΘB1)•(A0’)•(B0)] + [(A1ΘB1)•(A0ΘB0)• (IA>B)’•(IA<B)•(IA=B)’] (3). [A=B] = [(A1ΘB1)•(A0ΘB0)• (IA>B)’•(IA<B)’•(IA=B)] (a) (b) (c) A B A>B 0 0 0 0 1 0 1 0 1 1 1 0 A B A<B 0 0 0 0 1 1 1 0 0 1 1 0 A B A=B 0 0 1 0 1 0 1 0 0 1 1 1 (A>B) = A•B’ (A<B) = A’•B (A=B) = A•B + A’•B’ = AΘB Gambar 10. Implementasi kondisi matematik pada rangkaian komparator. Terlihat pada Gambar 10 (c) tanda Θ yang digunakan. Tanda tersebut adalah untuk fungsi Gerbang EXOR dengan tabel kebenaran disampingnya. IC gerbang EXOR sendiri telah ada tetapi jarang. Hanya satu vendor yang membuat gerbang EXOR, yaitu National Semiconductor dengan tipe DM74S135 dari tipe TTL yang dapat juga berfungsi sebagai gerbang EXNOR. Komparator yang sama tetapi dengan 4 bit dapat diperoleh dengan ICs seri 7485 yang biasa disebut 4-bit Magnitude Comparator. Komparator yang terakhir ini juga dapat dihubungkan satu sama lain sama seperti Komparator 2 bit yang ditunjukkan pada Gambar 8 untuk membentuk komparator yang lebih besar. Skematik dan rangkaian digital serta tabel operasinya dapat dilihat dalam TTL Data Book. Soal Latihan 1. Gambarkan rangkaian diskrit dari gerbang XOR 2. Gambarkan dan buktikan dengan aljabar bole rangkaian komparator 1bit dan 2 bit. 3. Jelaskan prinsip pembanding untuk 2 bit Refrensi Pangariwibowo, Kariyanto. (Tidak ada Tahun). Perancanaan Sistem Digital. Pusat Pengembangan Bahan Ajar, Universitas Mercu Buana. (Modul Online)