judul skripsi

advertisement

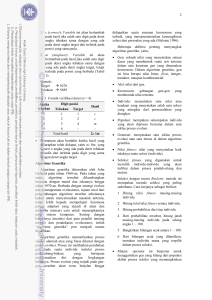

BAB I PENDAHULUAN 1.1. Latar Belakang Perkembangan teknologi informasi yang sangat pesat di era digital saat ini mempengaruhi kebutuhan pokok manusia akan informasi. Informasi yang bisa didapatkan secara cepat, tepat, dan akurat mempengaruhi segala aspek kehidupan manusia seperti sistem pengambilan keputusan yang lebih cepat, penyebaran tren, maupun perubahan gaya hidup (Broto, 2013). Namun kemudahan ini ternyata mengundang tindakan kejahatan di dunia maya seperti tindakan mencuri informasiinformasi rahasia ataupun memanipulasi informasi sehingga menimbulkan kerugian pihak tertentu. Salah satu cara terbaik untuk mengendalikan ancaman keamanan informasi adalah dengan kriptografi (Stallings, 2014). Kriptografi merupakan ilmu tentang penulisan rahasia dengan tujuan menyembunyikan arti dari pesan sebenarnya (Paar, 2010). Menurut Sari (2015) kriptografi adalah penerapan dan studi terhadap teknikteknik untuk keamanan komunikasi dari pihak ketiga. Kriptografi diperlukan ketika berkomunikasi dengan medium yang tidak aman. Ilmu kriptografi telah ada sejak tahun sebelum masehi, dibuktikan dengan adanya non-standard hieroglyps yang dipahat di monumen pada masa Old Kingdom of Egypt sekitar 1900 SM, juga ditemukannya semacam tablet clay dari Mesopotamia tertanggal 1500 SM yang berisi resep pemahat untuk pembuatan tembikar. 1 Ilmu kriptografi terus berkembang. Salah satu yang terkenal adalah mesin rotor elektromekanikal bernama enigma yang dipakai Jerman untuk mengenkripsi pesan tentara Jerman dalam perang melawan sekutu. Setelah itu terjadi peralihan dari ilmu kriptografi klasik berkembang menjadi ilmu kriptografi modern. Kriptografi modern sendiri dimulai dari publikasi Claude Elwood Shannon yang berjudul A Mathematical Theory of Cryptography pada tahun 1945. Setelah itu mulailah berkembang berbagai jenis algoritme kriptografi modern seperti algoritme DiffieHellman, algoritme RSA, algoritme Elgamal, algoritme DES (Data Encryption Standard) yang sempat menjadi standar enkripsi dari tahun 1975. Namun DES yang mempunyai panjang kunci 56-bit dinilai masih lemah dan mudah diretas, walaupun telah ditingkatkan keamanannya menjadi 3DES (Trang dan Loi, 2012). NIST (National Institute of Standards and Technology) pada tahun 2001 mengumumkan standar enkripsi baru bernama AES (Advanced Encryption Standard). Algoritme ini diambil dari pemenang sayembara penentuan standar enkripsi baru yang diadakan oleh NIST. Proposal yang ditetapkan sebagai pemenang adalah proposal yang diajukan oleh Joan Daemen dan Vincent Rijmen bernama Rijndael Cipher. Rijndael terbukti menunjukkan unjuk kerja yang sangat baik di perangkat keras maupun perangkat lunak. Rijndael juga membutuhkan memori yang sangat sedikit sehingga sangat baik digunakan pada lingkungan komputasi terbatas tanpa mempengaruhi unjuk kerjanya. Operasi Rijndael paling bisa menahan serangan daya dan pewaktuan. Bahkan Rijndael dapat menahan serangan tanpa mempengaruhi unjuk kerja secara signifikan (Daemen dan Rijmen, 2001). Hingga saat ini pun AES masih menjadi algoritme enkripsi simetris yang paling banyak digunakan. 2 Pengimplementasian AES tidak mengalami kendala apabila dieksekusi di komputer. Namun apabila dieksekusi di embedded system yang mempunyai clock rendah, maka masalah lama waktu eksekusi menjadi penting, apalagi jika data yang dienkripsi cukup besar. Maka diperlukan suatu engine AES yang diimplementasikan di level perangkat keras untuk mempercepat waktu eksekusi. Penelitian mengenai implementasi AES pada prosesor ARM telah dilakukan oleh Babu et al. (2011). Patil et al. (2013) juga telah berhasil mengimplementasikan AES di prosesor ARM untuk aplikasi jaringan sensor nirkabel. AES juga telah diimplementasi sebagai engine yang mendukung enkripsi dan dekripsi menggunakan FPGA Virtex XCV600 BG 560-6 dengan jumlah sumber daya yang digunakan sebesar 1853 slices dan lewatan sebesar 352 Mb/s (Ghewari et al., 2010). Trang dan Loi (2012) juga melakukan hal serupa menggunakan FPGA Altera APEX 20KC dengan jumlah memori sebesar 40960 bit (enkripsi) dan 42368 bit (dekripsi), latensi sepanjang 13 siklus clock (enkripsi) dan 25 siklus clock (dekripsi), lewatan sebesar 1184 Mb/s (enkripsi) dan 442 Mb/s (dekripsi), area sebesar 895 logic element (enkripsi) dan 1098 logic element (dekripsi). Paul et al. (2012) juga telah mengimplementasikan engine AES di RTOS (Real Time Operating System) FPGA Xilinx Spartan-3E (XC3S500E-FG320). Penelitian ini berfokus pada implementasi algoritme AES 128-bit di FPGA dan membandingkan kecepatan eksekusinya dengan embedded system yang dalam hal ini digunakan prosesor Nios II dari Altera. 3 1.2. Rumusan Masalah Berdasarkan latar belakang yang telah dipaparkan, diperlukan peningkatan kecepatan komputasi enkripsi AES di embedded system. Salah satu solusinya adalah dengan merancang suatu engine AES di level perangkat keras, dalam hal ini digunakan FPGA sebagai sarana implementasi. Kemudian perlu dilakukan pengujian engine yang telah dibuat serta membandingkan besar latensi, jumlah memori dan logic element yang digunakan dengan prosesor Nios II sebagai embedded system. 1.3. Batasan Masalah Penelitian ini berfokus pada hal-hal berikut: a. Desain yang dibuat adalah engine AES. Sedangkan desain prosesor Nios II sudah dalam bentuk Intelectual Property (IP) yang siap digunakan dan diprogram. Sehingga detail dari prosesor Nios II sendiri tidak dibahas. b. Desain engine AES yang dibuat hanya mendukung proses enkripsi dengan panjang kunci 128-bit. Desain ini tidak mendukung proses dekripsi. c. Engine AES yang dibuat hanya mendukung mode enkripsi Electronic Code Book (ECB). d. Implementasi modul AES menggunakan bahasa Verilog HDL. 1.4. Tujuan Penelitian Tujuan yang ingin dicapai pada penelitian ini adalah sebagai berikut: a. Mengimplementasikan engine AES di FPGA. b. Membandingkan panjang waktu eksekusi dan jumlah sumber daya yang digunakan pada implementasi AES menggunakan prosesor Nios II dan menggunakan prosesor Nios II + engine AES. 4 1.5. Manfaat Penelitian Manfaat penelitan yang diharapkan adalah sebagai berikut: a. Mendapatkan desain perangkat keras dengan kemampuan mengeksekusi algoritme AES. b. Mempunyai potensi untuk dijadikan properti intelektual di FPGA. c. Mengetahui besar peningkatan kecepatan eksekusi dan penambahan sumber daya pada penggunaan prosesor Nios II + engine AES dibandingkan hanya menggunakan prosesor Nios II. 1.6. Metode Penelitian Metode penelitian yang digunakan adalah sebagai berikut: a. Studi literatur Sebelum perancangan, dilakukan pengumpulan informasi serta studi mengenai topik-topik terkait desain FPGA dan algoritme AES dari jurnal, buku, ataupun karya ilmiah yang pernah dipublikasikan. Referensi-referensi ini digunakan untuk proses desain serta analisis terhadap pembuatan engine AES. b. Perancangan sistem Sistem yang dirancang adalah engine AES di level perangkat keras, yaitu menggunakan chip Altera Cyclone IV EP4CE22F17C6N. Perancangan sistem dilakukan dengan membagi sistem menjadi beberapa modul agar proses pengembangan menjadi lebih mudah. Implementasi engine AES dilakukan menggunakan bahasa Verilog HDL dan diagram skematik, sedangkan implementasi program Nios menggunakan bahasa pemograman C. 5 Setelah sistem berhasil diimplementasikan per modul, maka selanjutnya dilakukan pengintegrasian modul-modul AES menjadi satu kesatuan, termasuk mengimplementasikan prosesor Nios II bersama dengan engine AES dalam satu chip FPGA. c. Pengujian dan analisis hasil pengujian Pengujian dilakukan dalam tiga tahap yaitu sebagai berikut: - Simulasi fungsional modul-modul AES. Parameter yang diukur adalah kesesuaian masukan dan luaran modul serta latensi. - Simulasi fungsional engine AES yang telah terintegrasi. Parameter yang diukur adalah kesesuaian masukan dan luaran, frekuensi maksimum, latensi, pewaktuan, dan lewatan. - Pengujian secara fungsional menggunakan SoPC hasil integrasi dari prosesor Nios II dan engine AES. Parameter yang diukur adalah latensi, waktu eksekusi, dan total logic element yang digunakan. 1.7. Sistematika Penulisan BAB I PENDAHULUAN Bab ini berisi latar belakang, rumusan masalah, batasan masalah, tujuan penelitian, manfaat penelitian, metode penelitian, dan sistematika penulisan. Latar belakang memuat pula tinjauan terhadap penelitian-penelitian sebelumnya yang telah dipublikasi mengenai implementasi algoritme enkripsi AES di FPGA. 6 BAB II LANDASAN TEORI Bab ini berisi teori-teori yang berkaitan dengan penelitian yang dilakukan, meliputi teori-teori tentang desain FPGA, prosesor Nios II, dan algoritme AES. Teori-teori ini akan menunjang proses implementasi yang dilakukan. BAB III PERANCANGAN Bab ini menjelaskan mengenai perancangan sistem yang terdiri atas perancangan modul-modul AES, arsitektur AES yang digunakan secara keseluruhan, proses integrasi engine AES dengan prosesor Nios II, dan perancangan program yang berjalan di prosesor Nios II. BAB IV HASIL DAN PEMBAHASAN Bab ini membahas mengenai hasil pengujian sistem secara fungsional. Pengujian yang dimaksud meliputi simulasi fungsional modul-modul AES, simulasi fungsional engine AES secara keseluruhan, serta pengujian menggunakan prosesor Nios II sebagai sumber masukan data dan pembacaan data. BAB V KESIMPULAN DAN SARAN Bab ini berisi kesimpulan dari hasil penelitian yang telah dilakukan serta saran-saran untuk penelitian selanjutnya. 7