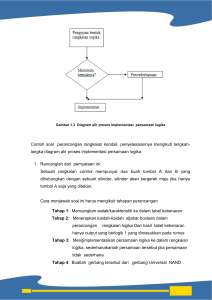

Pemrograman Devais FPGA (Field Programmable

advertisement

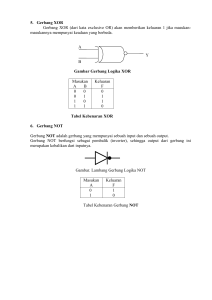

Pemrograman Devais FPGA (Field Programmable Gate Array) AQWAMROSADI K. Apa itu FPGA? • FPGA adalah suatu IC program logic dengan arsitektur seperti susunan matrik sel-sel logika yang dibuat saling berhubungan satu sama lain. • Memiliki jalur – jalur I/O FPGA yang memadai. • Mempunyai banyak gate: 5000 s/d juta-an gate • Kecepatan ~100 MHz • Memiliki sifat Programmable tapi, bersifat Volatile. • Programmable – User dapat memakai IC digital secara berulangulang untuk menyesuaikan program yang akan didownload ke dalam FPGA. • Volatile – Jika listrik mati maka secara otomatis fungsi FPGA akan hilang, artinya data yang telah diproses dan didownload akan hilang semuanya. Mengapa menggunakan FPGA? • Memiliki kemampuan untuk menangani beban komputasi yang begitu berat. • Menghilangkan tugas-tugas intensif dari Digital Signal Processing. • Kustomisasi arsitektur agar sesuai dengan algoritma ideal. • Mengurangi biaya sistem. • Efisiensi biaya. Teknologi FPGA berawal dari? • PROM (Programmable Read Only Memory) • EPROM (Erasable Programmable Read Only Memory) • EEPROM (Electrically Erasable Programmable Read Only Memory) • FLASH • SRAM (Static Random Access Memory) Teknologi yang berhubungan dengan FPGA • • • • • • • Transistor, IC (Integrated Circuit), SRAM (Static Random Access Memory), DRAM (Dynamic Random Access Memory), SPLD (Simple Programmable Logic Devices), CPLD (Complex Programmable logic Devices), ASIC Programmable Logic Device (PLD) • PLD adalah chip general-purpose yang digunakan untuk mengimplementasikan rangkaian logika (kombinasional). • PLD merupakan komponen elektronik yang dapat digunakan untuk membangun rangkaian digital sesuai dengan keinginan perancang. PLD menghubungkan beberapa gerbang logika yang diatur oleh perancang hardware. Programmable Logic Device (PLD) • Berdasarkan jumlah gerbang logika yang dimiliki, PLD dapat dibagi atas tiga tipe, PLD SPLD PLA CPLD PAL FPGA Simple Programmable Logic Devices (SPLD) • SPLD merupakan alat dengan gerbang AND yang dihubungkan dengan gerbang OR atau gerbang lain yang sejenis. • Gerbang-gerbang ini dapat diatur sedemikian rupa oleh pemakai. • SPLD dapat diprogram dengan fusible link, antifuse, EPROM, EEPROM, atau flash. PLA (Programmable Logic Array) • Merupakan pengembangan pertama dari PLD. • Struktur PLA: Skematik PLA Programmable Array Logic (PAL) • Di PLA, plane AND dan OR keduanya programmable. • Programmable Array Logic (PAL), lebih sederhana: – Plane OR tetap. – PAL lebih mudah untuk dimanufaktur dan dapat beroperasi lebih cepat daripada PLA. – Struktur ini paling banyak digunakan di aplikasi yang menggunakan programmable device sederhana. Skematik PAL Programmable Array Logic (PAL) • Device PAL mempunyai rangkaian tambahan di keluaran tiap gerbang OR untuk menyediakan fungsional tambahan: – Macrocell: gerbang OR dikombinasikan dengan rangkaian tambahan. – PAL = plane AND + macrocell Complex Programmable Logic Device (CPLD) • CPLD adalah gabungan dari beberapa SPLD yang dihubungkan oleh Programmable Switching Matrix. • Jadi, CPLD merupakan sebuah programmable logic device dengan kompleksitas antara Programmable Array Logic (PAL) dan FPGA. Karakteristik CPLD • CPLD memiliki sifat non-volatile yang diadopsi dari PAL. • Memiliki banyak gerbang yang diadopsi dari FPGA, meskipun gerbang PAL tidak sebanyak FPGA. • Jumlah gerbang yang terdapat pada IC CPLD berkisar antara ribuan sampai ratusan ribu gerbang logika. Arsitektur CPLD Logic Block memiliki macrocell yang terdiri dari sebuah SPLD dan sebuah flip-flop. I/O Block merupakan bagian pada CPLD yang digunakan sebagai interface data yang akan masuk dan keluar pada CPLD. Programmable Interconnect digunakan sebagai penghubung antar macrocell atau antara macrocell dengan I/O Block. Application-Specific Integrated Circuit (ASIC) • ASIC adalah IC yang hanya digunakan pada keperluan tertentu , kompleksitas IC ini cukup tinggi jadi tidak muat pada CPLD . Field Programmable Gate Array (FPGA) • Untuk mengimplementasikan rangkaian yang lebih besar lagi, digunakan tipe IC yang dapat mempunyai kapasitas logika yang lebih besar: – Field Programmable Gate Array (FPGA) • Tidak berisi blok AND dan OR. – Tapi, berisi array blok logika dan jalur interkoneksi antar blok. – Jalur interkoneksi disusun sebagai kanal routing secara horisontal dan vertikal yang berisi programmable switch. • Dapat mengimplementasikan fungsi logika dengan jumlah gerbang ekivalen jutaan. Field Programmable Gate Array (FPGA) Terdiri dari: • Configurable Logic Blocks (CLB). • Input/Output Blocks (IOB). • Programmable Switch Matrix (PSM) Configurable Logic Blocks (CLB) • CLB merupakan blok untuk membangun komponen-komponen combinational/sequential. • Untuk dapat membentuk CLB dibutuhkan truth table dalam membangun jalur logika. Input/Output Blocks (IOB) • IOB merupakan blok yang digunakan untuk mengirimkan sinyal keluar dari chip dan sekaligus membaca sinyal yang masuk ke dalam chip. Programmable Switch Matrix (PSM) • PSM merupakan penghubung yang bisa diatur sedemikian rupa untuk menghubungkan antar CLB dan CLB dengan IOB secara horizontal maupun secara vertikal. • Dapat mengeluarkan fan out (kemampuan untuk mengirimkan data ke banyak sumber untuk dijadikan input sekaligus) untuk multiple output. • Jadi, output dari CLB yang satu dapat dihubungkan ke input CLB yang lain melalui multiple PSM. Proses Pemrograman pada FPGA Design Entry Text Entry menggunakan VHDL (Verylog Hardware Definition Language) Schematic Entry Functional Simulation • Tujuan: memastikan rancangan rangkaian logika bekerja sesuai keinginan dengan input waveforms yang digunakan. Synthesis • Optimasi rangkaian logika dalam penggunaan gerbang. • Menghasilkan netlist yang merupakan daftar connection yang mendeskripsikan komponen dan keterhubungan komponen tersebut. Implementation • Meliputi: mapping, placing, and routing rancangan sehingga dapat diimplementasikan ke IC FPGA sesuai arsitektur dan konfigurasi pin IC FPGA tersebut. Timing Simulation • Verifikasi rangkaian apakah sudah bekerja pada frekuensi yang diinginkan dan tidak ada propagation delay. Device Programming • Membuat bitstream yang merepresentasikan rancangan akhir dan akan dikirim ke target device.