24 BAB III PERANCANGAN DAN IMPLEMENTASI C

advertisement

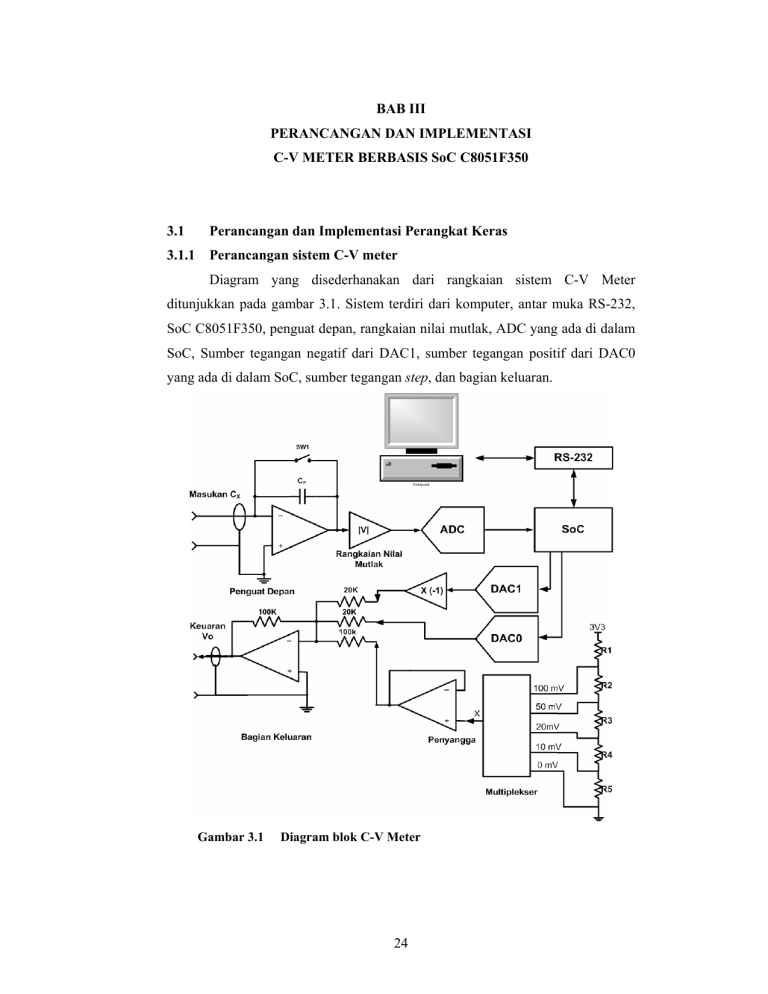

BAB III PERANCANGAN DAN IMPLEMENTASI C-V METER BERBASIS SoC C8051F350 3.1 Perancangan dan Implementasi Perangkat Keras 3.1.1 Perancangan sistem C-V meter Diagram yang disederhanakan dari rangkaian sistem C-V Meter ditunjukkan pada gambar 3.1. Sistem terdiri dari komputer, antar muka RS-232, SoC C8051F350, penguat depan, rangkaian nilai mutlak, ADC yang ada di dalam SoC, Sumber tegangan negatif dari DAC1, sumber tegangan positif dari DAC0 yang ada di dalam SoC, sumber tegangan step, dan bagian keluaran. Gambar 3.1 Diagram blok C-V Meter 24 Komputer berfungsi sebagai kontrol utama yang mengendalikan sistem C-V Meter secara keseluruhan sekaligus sebagai pengolah dan penyimpan data hasil pengukuran. Komunikasi antara komputer dengan SoC C8051F350 menggunakan sistem antar muka serial, sehingga untuk menyesuaikan level tegangan antara komputer dengan SoC C8051F350 dibutuhkan antar muka RS232. Sebagai kontrol sekunder, SoC C8051F350 berfungsi mengendalikan sistem pengukuran sesuai dengan perintah kontrol utama (komputer) mengatur saklar pada penguat depan, mengatur kerja DAC, memilih tegangan step, mengolah data hasil konversi ADC dan mengirimkan data hasil pengukuran ke komputer. SoC yang digunakan pada sistem C-V Meter yang dirancang menggunakan SoC C8051F350 dari Silicon Laboratories 15). Bagian Penguat depan berfungsi untuk menampung seluruh muatan yang masuk dan mengubahnya menjadi tegangan yang sebanding dengan CF. Tegangan keluaran dari penguuat depan kemudian masuk ke rangkaian nilai mutlak sehingga ADC selalu membaca tegangan positif. Tegangan DC untuk tegangan bias negatif dihasilkan oleh DAC1 dengan penguat membalik (inverting) dan DAC0 menghasilkan tegangan positif. Sumber tegangan step diberikan oleh multiplekser dan penyangga. Bagian keluaran berfungsi untuk menjumlahkan dan menguatkan tegangan bias dengan tegangan dari sumber step. Devais yang akan diukur dihubungkan seri dengan sumber tegangan dan masukan pada tahap penguat depan (rangkaian penguat balikan). Pembuatan PCB (Printed Circuit Board) rangkaian dibagi menjadi dua, yaitu: rangkaian pengendali tegangan, dan rangkaian kontrol seperti yang ditunjukkan pada gambar 3.2. PCB Pengendali tegangan terdiri atas sumber tegangan bias, sumber tegangan step dan bagian keluaran. PCB rangkaian kontrol terdiri dari SoC C8051F350, antar muka RS-232, penguat balikan muatan dan rangkaian nilai mutlak. Pemisahan PCB ini untuk menghindari gangguan dari sinyal tegangan tinggi terhadap SoC dan sistem penguat balikan muatan. 25 Gambar 3.2 Gambar PCB sistem C-V Meter 3.1.2 Pembangkit tegangan sumber bias Untuk mendapatkan kurva C-V devais yang akan diukur harus diberi tegangan bias dengan sapuan tegangan pada daerah yang diinginkan, biasanya dari tegangan negatif melewati tegangan nol hingga mencapai tegangan positif tertentu. Sumber tegangan bias pada sistem C-V Meter ini dirancang menggunakan dua buah DAC arus yaitu IDAC0 dan IDAC1 8 bit yang terdapat pada SoC C8051F350. Diagram blok IDAC pada SoC C8051F350 ditunjukkan oleh gambar 3.3. 26 Diagram blok IDAC 8 bit dalam SoC C8051F350 Gambar 3.3 15) Rangkaian penghasil tegangan bias ditunjukkan oleh gambar 3.4. Arus dari IDAC0 diubah menjadi tegangan dengan bantuan op-amp U1 sehingga menghasilkan tegangan negatif yang nilainya ditunjukkan oleh persamaan 3.1. Nilai tegangan negatif ini akan dibalikkan menjadi tegangan positif yang diperkuat pada bagian keluaran dari sistem C-V Meter. VDAC + = −( IDAC 0 × R1) (a) Gambar 3.4 (3.1) (b) Rangkaian sumber tegangan bias (a) sumber tegangan bias positif (b) sumber tegangan bias negatif 27 Untuk mendapatkan tegangan negatif digunakan IDAC1 yang diubah menjadi tegangan oleh U2A dan kemudian dibalikkan oleh U2B menjadi sebuah tegangan positif yang sebanding dengan nilai IDAC1. Nilai tegangan positif ini akan diperkuat dan dibalikkan menjadi tegangan negatif pada bagian keluaran. Nilai keluaran tegangan rangkaian ini diberikan oleh persamaan 3.2. VADC − = IDAC1× R2 (3.2) DAC arus merupakan pengubah data digital menjadi arus yang sebanding dengan data digitalnya. Salah satu keunggulan penggunaan IDAC ini adalah karena pengubahan daerah keluarannya sangat mudah. IDAC yang ada pada SoC C8051F350 mempunyai 4 pilihan daerah keluaran yang diatur dengan cara mengubah nilai skala penuhnya. Nilai skala penuh IDAC pada SoC C8051F350 terdiri dari empat pilihan, yaitu: 0.25 mA, 0,5 mA, 1 mA, dan 2 mA. Dengan menggunakan resistor R1, R2 sama dengan 2K seperti pada gambar 3.2, maka akan diperoleh tegangan keluaran dengan empat pilihan keluaran skala penuh, yaitu: 0,5 V, 1,0 V, 2,0 V dan 4,0 V. Pemilihan nilai reistor R1 dan R2 untuk menjaga keluaran maksimum op-amp berada di bawah 4,2 V karena nilai tegangan ini merupakan batasan keluaran op-amp yang dicatu dengan tegangan ±5V. Tegangan keluaran akhir ditentukan oleh besarnya penguatan pada bagian keluaran dari sistem C-V Meter. 3.1.3 Sumber tegangan step Dalam pengukuran kapasitansi menggunakan metode balikan muatan, sistem akan memberikan tegangan step (∆V) pada DUT dan kemudian mengukur jumlah muatan yang masuk (∆Q) dan membagi dengan nilai step tegangan yang jatuh pada kapasitor yang sedang diukur. Rangkaian pembangkit sumber tegangan step ditunjukkan pada gambar 3.5. 28 Gambar 3.5 Rangkaian sumber tegangan step Rangkaian pada gambar 3.5 merupakan pembagi tegangan yang membagi suatu tegangan referensi yang konstan menggunakan LM3904. Keluaran pembagi tegangan dipilih menggunakan multiplekser 4051 sedemikian rupa sehingga hanya ada satu keluaran tegangan. Keluaran tegangan dari multiplekser kemudian diumpankan pada sebuah bufer U3A dan dibalikkan polaritasnya dengan op-amp U3B sehingga keluaran akhir rangkaian adalah tegangan negatif. Tegangan step dibuat negatif karena pada bagian keluaran sistem C-V Meter tegangan ini akan dibalik polaritasnya dengan penguatan 1x. Pembagi tegangan dibentuk oleh RS1, RS2, RS3, RS4, dan RS5 yang membagi tegangan referensi 3,3V menjadi 100 mV, 50 mV, 20 mV dan 10 mV. Tegangan step bernilai sangat kecil untuk mendapatkan pengukuran DUT yang membutuhkan waktu lama untuk mencapai kesetimbangan. 29 3.1.4 Tahap keluaran Keluaran dari sumber tegangan bias positif, bias negatif dan tegangan step digabungkan menggunakan rangkaian penguat penjumlah pada tahap keluaran dari sistem C-V Meter. Gambar 3.6 menunjukkan gambar rangkaian untuk tahap keluaran. Gambar 3.6 Rangkaian tahap keluaran sistem C-V Meter 30 Rangkaian pada tahap keluaran pada dasarnya terdiri dari sebuah sistem penguat op-amp membalik gabungan. Rangkaian op-amp gabungan dibentuk oleh U4, Q1, Q2 dan beberapa komponen lain pemberi bias untuk transistor. Komponen balikan dibentuk oleh RO3 dan CO1 yang menentukan penguatan dari rangkaian. Penguatan dari rangkaian pada gambar 3.6 diberikan oleh persamaan 3.3. RO1 RO3 ⎛ RO3 ⎞ VDAC − ⎟ VDAC + + VStep + Vo = − ⎜ RO0 RO 2 ⎝ RO1 ⎠ (3.3) Dengan demikian, penguatan untuk sistem dengan nilai seperti diatas menghasilkan penguatan -1x untuk tegangan sumber step, -5x untuk tegangan VDAC+ dan VDAC-. Transistor Q3 dan RO7 membatasi arus keluaran tegangan positif sistem dan transistor Q4 serta RO8 membatasi arus negatif keluaran sistem. Arus keluaran dari tegangan sumber dibatasi maksimum sampai 4 mA. Gambar 3.7 menunjukkan rangkaian tambahan dari tahap keluaran yang memberikan pembatasan arus. Pembatasan arus terjadi pada 3 mA ± 1 mA. Pada setengah positif dari tahap keluaran komplementer, Q7 aktif ketika batas arus positif terlampaui. Arus basis Q3 dihubungsingkatkan melalui DO3 untuk mencegah tahap keluaran naik terlalu tinggi. Untuk setengah negatif dari tahap komplementer ini, Q4, RO8 dan DO4 menunjukkan fungsi yang sama. 31 Gambar 3.7 3.1.5 Rangkaian pembatas arus pada tahap keluaran sistem C-V Meter Perancangan penguat depan Penguat depan merupakan rangkaian utama dari sistem C-V Meter dan dirancang menggunakan metode balikan muatan. Rangkaian dasar pengukurannya ditunjukkan pada gambar 3.8, salah satu terminal dari kapasitansi yang akan diukur (Cx) dihubungkan ke sumber tegangan dan ujung yang lain dihubungkan ke masukan dari penguat balikan muatan (integrator). Pada saat awal, kapasitor balikan (Cf) dari integrator dikosongkan dengan menutup saklar SW1 yang terhubung secara paralel dengan Cf. Pengukuran dilakukan ketika saklar SW1 dibuka. Setiap muatan yang terpindahkan ke dari integrator akan menyebabkan perubahan pada keluaran integrator seperti pada persamaan 3.4. 32 ΔVout = Gambar 3.8 −ΔQ Cf (3.4) Rangkaian penguat depan Op-amp yang digunakan pada rangkaian penguat depan ini adalah IC OP07 yang mempunyai tegangan offset rendah hingga 75 µV. Kapasitor Cf merupakan kapasitor umpan balik yang dirancang untuk dapat mengukur kapasitansi hingga 100 pF. Nilai kapasitansi CF harus sangat tepat diketahui dan sebaiknya diukur denga alat ukur yang sangat presisi, karena komponen inilah penentu ketelitian pengukuran. Saklar SW1 merupakan reed relay yang telah dilengkapi dengan magnetic shield untuk menghindari gangguan akibat pengaktifan saklar. Reed relay yang digunakan adalah tipe EDR201A500 yang merupakan relay SPST (Single Pole Single Through) dengan tegangan kontrol 5V. Relay ini memiliki nilai resistansi yang kecil pada saat terhubung hingga 150 mΩ. Gambar 3.9 Rangkaian penguat depan dengan pengubah daerah pengukuran 33 Sistem penguat depan dirancang untuk dapat melakukan pengukuran dengan dua daerah pengukuran yang berbeda. Rangkaian lengkap penguat depan ditunjukkan pada gambar 3.9. Rangkaian dilengkapi dengan tambahan SW2 dan CF1. Ketika saklar SW2 aktif maka nilai kapasitansi balikan akan menjadi persamaan 3.5. Nilai CF1 juga harus mempunyai kepresisian yang baik. CF Total = CF + CF 1 (3.5) Dalam proses pengukuran kapasitansi pada sistem C-V Meter yang dirancang dilakukan tiga kali pengukuran muatan di sekitar tegangan step. Dari ketiga pengukuran ini kapasitansi dan arus yang mengalir ke devais (pada akhir waktu tunda) dihitung. Gambar 3.10 menjelaskan bagaimana bentuk gelombang muatan diukur. Simbol Q1, Q2, dan Q3 mewakili tiga pengukuran yang dibuat pada waktu tertentu. Q1 adalah tegangan dasar sesaat sebelum devais diberi tegangan step. Q3 diukur setelah waktu tunda tertentu (delay) dan menandai berakhirnya transfer muatan melalui CX. Q2 diukur sebelum Q3 (diberi selang waktu t0 sebelum pengukuran Q3) dan digunakan untuk menentukan kemiringan dari bentuk gelombang muatan. Kemiringan ini menunjukkan jumlah arus (Q/t) yang mengalir pada CX selama waktu terakhir waktu delay t0. Q/t merepresentasikan kebocoran pada CX atau sistem dan nilainya dapat diperoleh dari persamaan. Dari pengukuran gelombang muatan, diperoleh kapasitansi CX seperti pada persamaan 3.7. Nilai CX yang lebih tepat dengan mendeteksi kebocoran pada rangkaian menggunakan Q/t maka diperoleh CX koreksi seperti pada persamaan 3.8. 34 Gambar 3.10 3.1.6 Bentuk Gelombang pengukuran muatan Keluaran tegangan dan Pemilihan dan implementasi SoC C8051F350 SoC berfungsi sebagai kontrol sekunder yang mengendalikan bagian-bagian penting dari sistem C-V meter. SoC yang digunakan adalah SoC C8051F350 dari Silicon Laboratories. SoC ini dipilih karena fasilitasnya lengkap, cepat, konsumsi daya rendah, kemasannya kecil dan ringkas serta harganya relatif murah. Arsitektur SoC C8051F350 seperti ditunjukkan Gambar 3.11 terdiri atas 15): 1. ADC (analog to digital converter) dengan spesifikasi: • resolusi 24 bit atau 16 bit • throughput dapat diatur sampai dengan 1 ksps (kilo sample per second) • dapat menangani sampai dengan 8 buah masukan eksternal • terdapat PGA (programmable gain amplifier) yang dapat diatur besarnya: 1x sampai 128x • terdapat sensor temperatur internal 2. dua buah IDAC (current digital to analog converter) 8 bit 35 3. dua buah komparator analog 4. tegangan referensi 2,45 V 5. RAM (random acces memory) 768 byte 6. flash ISP (in system programmable) 8 kilo byte dalam 512 sektor 7. inti (core) SoC C8051F350 8051 kecepatan tinggi dengan kelebihan: • tujuh puluh persen instruksi dilakukan dalam 1 atau 2 sistem clock • kecepatan eksekusi program sampai dengan 50 MIPS (mega instruction per second) • sumber interupsi yang bisa diperluas 8. sumber clock • sumber oscillator internal 24.5 MHz dengan akurasi ± 2% dan mendukung operasi UART • sumber clock eksternal dapat berasal dari kristal, rangkaian RC atau osilator • terdapat pengali clock hingga mencapai 50 MHz internal • dapat berganti clock selama program berlangsung (on-the-fly) 9. tujuh belas port input/output toleran terhadap tegangan 5V dengan arus benaman (sink current) yang tinggi masing-masing hingga 100 mA 10. sistem antarmuka SMBus (kompatibel dengan I2C), SPI, dan UART 11. empat buah counter/timer untuk kegunaan umum yang dapat diatur dengan 3 modul capture/compare 12. WDT (watch-dog timer) 13. fasilitas JTAG dengan kemampuan: • sistem dapat dapat di-debug tanpa membutuhkan emulator • dilengkapi dengan kemampuan breakpoints, single stepping, watchpoints dan stack monitor • dapat memodifikasi isi memori dan register 14. catu daya 2,7 – 3,6 V dengan konsumsi arus 5,8 mA pada clock 25 MHz dan 11 μA pada clock 32 kHz 36 Gambar 3.11 Arsitektur SoC C8051F350 3.1.7 Implementasi 15) ADC (analog to digital converter) dan pengkondisi sinyal Diagram blok subsistem ADC dalam SoC C8051F350 ditunjukkan oleh Gambar 3.12. subsistem ini terdiri atas penyangga masukan (input buffer), tegangan referensi internal, kontrol kalibrasi, PGA (programmable gain amplifier), dan ADC 24 bit dengan throughput 1 ksps, fast filter dan SINC3 Filter. Analog multiplekser, PGA, ADC dan filter seluruhnya dapat dikonfigurasi dengan perangkat lunak melalui SFR (special function register) 15). 37 Gambar 3.12 Diagram blok ADC 24 bit dalam SoC C8051F350 15) Masukan ADC dipilih dengan menggunakan multiplekser analog 9 kanal yang masukannya bisa saling dipasangkan seperti ditunjukkan pada gambar 3.13. Masing-masing masukan dapat dipilih dengan referensi terhadap masukan yang lain. Sebagai contoh: masukan AIN0.0 dapat diukur terhadap beberapa pasangannya, yaitu terhadap: ground, AIN0.1-AIN0.7, atau terhadap sensor temperatur. 38 Gambar 3.13 Diagram blok multiplekser untuk memilih masukan ADC 24 bit dalam SoC C8051F350 15) 3.1.8 Sistem antarmuka Sistem antarmuka yang digunakan pada sistem C-V Meter ini adalah sistem antar muka serial melalui COM serial pada komputer yang berbentuk DB9. Sistem antarmuka ini dipilih dengan pertimbangan sudah lazim digunakan, relatif mudah dalam pengoperasian, dan relatif mudah dalam pembuatan protokolkomunikasi-nya. Hampir setiap komputer yang ada sekarang dilengkapi dengan antarmuka ini dan diperkirakan dalam beberapa waktu ke depan antarmuka ini masih digunakan dan terdapat pada komputer. Level tegangan antara COM serial komputer dengan SoC C8051F350 berbeda, oleh karena itu diperlukan divais yang dapat menjembatani kedua piranti tersebut, piranti yang dapat menyesuaikan kedua level tegangan tersebut harus memenuhi standar RS232. Untuk keperluan ini digunakan IC ST3222E dari ST Electronics. IC ini terdiri dari 2 buah pengubah level tegangan CMOS ke RS232 dan 2 buah pengubah level tegangan RS232 ke CMOS dengan kecepatan transfer 39 data sampai dengan 250 kbps dan memerlukan arus supply yang rendah sebesar 300 µA. Gambar rangkaian antar muka sistem C-V Meter dengan komputer ditunjukkan oleh gambar 3.14. Gambar 3.14 Rangkaian ST3222E Antar Muka RS-232 menggunakan 40 3.2 Perancangan dan Implementasi Perangkat Lunak 3.2.1 Perancangan dan Implementasi Perangkat Lunak pada SoC C8051F350 Perangkat lunak yang digunakan untuk program mikrokontroller adalah bahasa C yang dikompilasi ke dalam bahasa assembler MCS-51 16) untuk program komputer digunakan bahasa pemrograman Delphi 6.0 , sedangkan 17) . Diagram alir pemrograman untuk program SoC C8051F350 ditunjukkan oleh Gambar 3.15. Gambar 3.15 Diagram alir program pada SoC C8051F350 41 3.2.2 Perancangan dan Implementasi Perangkat Lunak pada Komputer Diagram alir pemrograman untuk program komputer ditunjukkan oleh Gambar 3.16. Gambar 3.16 Diagram alir program pada komputer Diagram alir pada gambar 3.16 memberikan gambaran tentang proses pengukuran C-V. Semua proses inisialisasi bisa dikendalikan oleh pengguna. Inisialisasi berguna untuk mendefinisikan besarnya tegangan Step, waktu tunda, 42 pendeklarasian nilai Cf, dan inisialisasi mikrokontroler lainnya. Program utama dimulai dengan mengosongkan muatan pada Cf dan kemudian pengukuran V1 yaitu Vout. Pemberian tegangan step, ΔV untuk waktu delay tertentu diberikan kemudian tegangan keluaran Vout diukur untuk mendapatkan V2. Dengan diperolehnya V2 maka Cx bisa diperoleh dengan menggunakan persamaan 6. Pengukuran ini dilakukan terus menerus untuk tegangan bias yang berbeda sehingga akan diperoleh kurva Cx terhadap V bias. Cx = − V2 − V1 Cf VStep (3.9) 43