- Repository UIN SUSKA

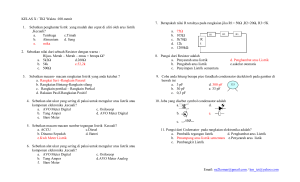

advertisement