bab III gerbang logika dan aljabar boole

advertisement

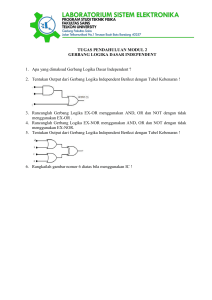

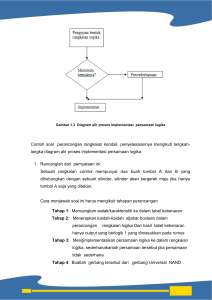

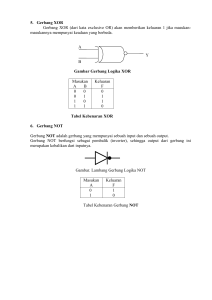

BAB III GERBANG LOGIKA DAN ALJABAR BOOLEAN 3.1 Pendahuluan Komputer, kalkulator, dan peralatan digital lainnya kadang-kadang dianggap oleh orang awam sebagai sesuatu yang ajaib. Sebenarnya peralatan elektronika digital sangat logis dalam operasinya. Bentuk dasar blok dari setiap rangkaian digital adalah suatu gerbang logika. Gerbang logika adalah rangkaian digital yang dapat dinyatakan dengan dua keadaan (tegangan/logika tinggi atau tegangan/logika rendah). Gerbang logika merupakan rangkaian dengan satu atau lebih sinyal masukan, tetapi hanya menghasilkan satu sinyal keluaran. Keluaran akan berlogika tinggi (1) atau berlogika rendah (0) tergantung pada sinyal masukan digital yang diberikan. Rangkaian digital di dalam computer digital dan system digital lainnya dirancang dengan menggunakan disiplin matematika, yaitu Aljabar Boole. Nama tersebut diambil dari nama penemunya yaitu George Boole. 3.2 Gerbang Logika Dasar Gerbang logika dasar ada tiga, yaitu : gerbang NOT (Inverter), gerbang AND, dan gerbang OR. 3.2.1 Gerbang NOT (Inverter) Gerbang NOT adalah gerbang logika dasar yang mempunyai satu sinyal masukan dan satu sinyal keluaran, dimana keluarannya selalu berlawanan dengan masukannya. Apabila sinyal masukan berlogika 1, maka keluarannya akan berlogika 0, begitu sebaliknya. Jadi, gerbang NOT berfungsi sebagai inverter (pembalik) inputnya. Simbol gerbang NOT diperlihatkan pada Gambar 3.1. Gambar 3.1. Simbol Inverter Untuk menggambarkan level output dari masing-masing kombinasi input dapat dibuat dengan menggunakan tabel kebenaran. Tabel 3.1 menunjukkan tabel kebenaran inverter. Tabel 3.1. Tabel Kebenaran Inverter A 0 1 Y 1 0 Persamaan logika atau fungsi aljabar boole untuk gerbang NOT adalah : Y =A Operasi Inverter secara simbolis direpresentasikan dengan menggunakan garis di atas. Timing Diagram acap kali dibutuhkan untuk memudahkan dalam menganalisa kinerja suatu system. Gambar 3.2 berikut menggambarkan timing digram gerbang NOT. Gambar 3.2. Timing Diagram Gerbang NOT Dalam prakteknya, gerbang NOT disediakan dalam bentuk IC digital, dan salah satu jenisnya adalah IC TTL (Transistor-transistor Logic). Seri IC TTL untuk gerbang OR 2 input adalah 7404. IC 7404 menyediakan 6 buah gerbang NOT. Gambar IC dan susunan pin IC 7404 ditunjukkan pada gambar berikut. (a) Gambar IC 7404 (b) Susunan Pin IC 7404 Gambar 3.3. Gambar IC dan Susunan Pin IC 7404 29 3.2.2 Gerbang AND Gerbang AND mempunyai dua atau lebih sinyal masukan tetapi hanya satu sinyal keluaran. Semua masukan harus dalam keadaan tinggi untuk mendapatkan keluaran yang tinggi. Gambar 3.3 memperlihatkan simbol gerbang AND 2 input. Gambar 3.4. Simbol Gerbang AND 2 input Tabel kebenaran gerbang AND untuk kombinasi 2 masukan A dan B diperlihatkan pada Tabel 3.2. Tabel 3.2. Tabel Kebenaran Gerbang AND 2 input A 0 0 B 0 1 1 1 0 1 Y 0 0 0 1 Persamaan logika atau fungsi aljabar untuk gerbang AND 2 input adalah : Y = A⋅ B Operasi AND secara simbolis direpresentasikan dengan menggunakan operator titik (dot), dan boleh juga disederhanakan tanpa menggunakan titik (dot). Gambar 3.5 berikut menggambarkan timing digram gerbang AND 2 input. Gambar 3.5. Timing Diagram Gerbang AND 2 input Dalam praktek, gerbang AND jenis TTL mempunyai nomor seri 7408. Gambar susunan pin IC 7408 seperti ditunjukkan pada gambar 3.6 berikut : 30 Gambar 3.6. Susunan Pin IC 7408 (AND 2 input) 3.2.3 Gerbang OR Gerbang OR mempunyai dua atau lebih sinyal masukan tetapi hanya satu sinyal keluaran. Jika salah satu atau semua sinyal masukannya tinggi, maka sinyal keluarannya akan menjadi tinggi. Simbol gerbang OR 2 input diperlihatkan pada Gambar 3.7. Gambar 3.7. Simbol Gerbang OR 2 input Tabel kebenaran gerbang OR untuk kombinasi 2 masukan A dan B diperlihatkan pada Tabel 3.3. Tabel 3.3. Tabel Kebenaran Gerbang OR 2 input A 0 0 1 1 B 0 1 0 1 Y 0 1 1 1 Persamaan logika atau fungsi aljabar untuk gerbang OR 2 input adalah : Y = A+ B Operasi OR secara simbolis direpresentasikan dengan menggunakan operator tambah (“+“). Gambar 3.8 berikut menggambarkan timing digram gerbang OR 2 input. 31 Gambar 3.8. Timing Diagram Gerbang OR 2 input Dalam praktek, IC TTL untuk gerbang OR 2 input adalah 7432. Gambar susunan pin IC 7432 ditunjukkan pada gambar 3.9 berikut : Gambar 3.9. Susunan Pin IC 7432 (OR 2 input) 3.3 Gerbang Logika Lain 3.3.1 Gerbang NAND Gerbang NAND mempunyai dua atau lebih sinyal masukan tetapi hanya satu sinyal keluaran. Struktur logika gerbang NAND yang terdiri dari sebuah gerbang AND dan sebuah inverter yang dirangkai secara seri. Gerbang NAND merupakan kebalikan dari gerbang AND, dimana keluarannya akan rendah apabila semua masukannya berlogika tinggi. Simbol gerbang NAND 2 input diperlihatkan pada Gambar 3.10. (a). Struktur Logika (b). Simbol Standar NAND 2 input Gambar 3.10. Simbol Gerbang NAND 2 input 32 Tabel kebenaran gerbang NAND untuk kombinasi 2 masukan A dan B diperlihatkan pada Tabel 3.4. Tabel 3.4. Tabel Kebenaran Gerbang NAND 2 input A 0 0 1 1 B 0 1 0 1 Y 1 1 1 0 Persamaan logika atau fungsi aljabar untuk gerbang NAND 2 input adalah : Y = A⋅ B Timing diagram gerbang NAND 2 input dapat dilihat pada Gambar 3.11 berikut : Gambar 3.11. Timing Diagram Gerbang NAND 2 input Dalam praktek, gerbang NAND disediakan dalam bentuk IC. Untuk jenis TTL, gerbang NAND serinya antara lain 7400 (NAND 2 input) dan 7410 (NAND 3 input). Berikut adalah susunan pin IC 7400. VCC 14 13 12 11 10 9 8 7400 1 2 3 4 5 6 7 GND Gambar 3.12. Susunan Pin IC 7400 (NAND 2 input) 33 3.3.2 Gerbang NOR Gerbang NOR mempunyai dua atau lebih sinyal masukan tetapi hanya satu sinyal keluaran. Struktur logika gerbang NAND yang terdiri dari sebuah gerbang OR dan sebuah inverter yang dirangkai secara seri. Gerbang NOR merupakan kebalikan dari gerbang OR. Untuk memperoleh keluaran yang tinggi dari gerbang NOR, semua masukan harus berada dalam keadaan rendah. Dengan kata lain, gerbang NOR hanya mengenal kata masukan yang semua bitnya sama dengan nol. Simbol gerbang NOR 2 input diperlihatkan pada Gambar 3.13. (a). Struktur Logika (b). Simbol Standar NOR 2 input Gambar 3.13. Simbol Gerbang NOR 2 input Tabel kebenaran gerbang NOR untuk kombinasi 2 masukan A dan B diperlihatkan pada Tabel 3.5. Tabel 3.5. Tabel Kebenaran Gerbang NOR 2 input A 0 0 1 1 B 0 1 0 1 Y 1 0 0 0 Persamaan logika atau fungsi aljabar untuk gerbang NOR 2 input adalah : Y = A+ B Timing diagram gerbang NOR 2 input dapat dilihat pada Gambar 3.14 berikut : Gambar 3.14. Timing Diagram Gerbang NOR 2 input 34 Dalam praktek, gerbang NOR disediakan dalam bentuk IC. IC TTL untuk gerbang NOR 2 input mempunyai nomor seri 7402. Gambar 3.15. Susunan Pin IC 7402 (NOR 2 input) 3.3.3 Gerbang EX-OR Gerbang EX-OR mempunyai dua atau lebih sinyal masukan tetapi hanya satu sinyal keluaran. Keluaran gerbang EX-OR akan menjadi tinggi bila salah satu masukannya berlogika tinggi (1). Dengan kata lain, keluaran 1 hanya terjadi bila masukannya berbeda. Hal ini dapat dilihat pada tabel 3.6 berikut : Tabel 3.6. Tabel Kebenaran Gerbang EX-OR 2 input A 0 0 1 1 B 0 1 0 1 Y 0 1 1 0 Berdasarkan tabel kebenaran di atas dapat dituliskan persamaan aljabarnya yaitu : Y = AB + A B atau : Y = A⊕ B Simbol logika untuk gerbang EX-OR 2 input adalah : Gambar 3.16. Simbol Gerbang EX-OR 2 input Timing diagram gerbang EX-OR 2 input dapat dilihat pada Gambar 3.17 berikut : 35 Gambar 3.17. Timing Diagram Gerbang EX-OR 2 input Dalam praktek, IC TTL untuk gerbang EX-OR mempunyai nomor seri 7486. Gambar berikut menggambarkan sususan pin IC 7486 : Gambar 3.18. Susunan Pin IC 7486 (EX-OR 2 input) 3.3.4 Gerbang EX-NOR Gerbang EX-NOR ekivalen dengan EX-OR yang diikuti oleh sebuah inverter, seperti yang ditunjukkan pada gambar berikut : A B Y Gambar 3.19. Simbol Gerbang EX-NOR 2 input Persamaan fungsi aljabarnya adalah : Y = A B + AB Keluaran gerbang EX-NOR akan tinggi bila semua masukannya sama, sehingga gerbang EX-NOR ini merupakan gerbang yang ideal untuk digunakan 36 sebagai pembanding bit atau kata, dimana masukan dikenali oleh gerbang bila kedua bit masukannya identik. Contoh rangkaian pembanding kata : Register A A3 Y3 A2 Register B A1 Y2 A0 Y1 B3 B2 B1 B0 Y0 EQUAL Gambar 3.20. Rangkaian Pembanding Kata Rangkaian di atas adalah rangkaian pembanding kata (word comparator), yang mengenali 2 kata identik. Gerbang EX-NOR yang paling kiri membandingkan A3 dan B3, jika keduanya sama maka Y3 = 1, begitu juga untuk ketiga gerbang lainnya. Bila kata A dan B identik, maka seluruh gerbang EXNOR mempunyai keluaran tinggi dan keluaran akhir dari gerbang AND berupa sinyal EQUAL akan berlogika tinggi. Bila kata A dan B berbeda, maka sinyal EQUAL berlogika rendah. Gambar 3.21 memperlihatkan timing diagram gerbang EX-NOR 2 input. Gambar 3.21. Timing Diagram Gerbang EX-NOR 2 input 3.4 Deskripsi Rangkaian Logika ke Persamaan Logika Rangkaian logika dapat dideskripsikan ke dalam bentuk persamaan logika atau ekspresi aljabar boole. Untuk memudahkan dalam mendeskripsikan atau 37 membuat persamaan logika, tulislah terlebih dahulu persamaan logika pada setiap output gerbang penyusun rangkaian tersebut. Selanjutnya, penulisan persamaan logika terhadap gerbang terakhir, akan menghasilkan persamaan logika dari rangkaian tersebut. Contoh 3.1 Buatlah persamaan logika untuk rangkaian logika berikut ini : Jawab : Jadi, persamaan logika dari rangkaian tersebut : Y = A+ B Contoh 3.2 Buatlah persamaan logika untuk rangkaian logika berikut ini : Jawab : A B C Y = A (B+C) B+C Sehingga : Y = A( B + C ) 3.5 Membuat Tabel Kebenaran Suatu Rangkaian Logika Untuk membuat tabel kebenaran dari suatu rangkaian logika dapat dilakukan dengan 2 cara, yaitu : 38 • Cara 1 : Menulis keluaran dari semua gerbang yang merupakan komponen penyusun rangkaian logika untuk seluruh kombinasi input • Cara 2 : Mengevaluasi keluaran dari persamaan logika Membuat tabel kebenaran dengan cara 2 relatif lebih mudah dan cepat dilakukan dibandingkan dengan cara 1. Contoh 3.3 dan 3.4 diselesaikan dengan menggunakan cara 1, sedangkan contoh 3.5 diselesaikan dengan menggunakan cara 2. Contoh 3.3 Buatlah tabel kebenaran untuk gambar rangkaian yang ada pada contoh 3.1 ! Jawab : Persamaan logika untuk gambar rangkaian pada contoh 3.1 : Y = A + B Tabel kebenaran untuk persamaan di atas : A B A Y = A+ B 0 0 1 1 0 1 1 1 1 0 0 0 1 1 0 1 Contoh 3.4 Buatlah tabel kebenaran untuk gambar rangkaian yang ada pada contoh 3.2 ! Jawab : Persamaan logika untuk gambar rangkaian pada contoh 3.2 : Y = A(B+C) Tabel kebenaran untuk persamaan di atas : A B C B+C Y = A(B+C) 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 39 0 1 1 1 0 1 0 0 0 0 1 0 1 1 1 1 1 0 1 1 1 1 1 1 1 Contoh 3.5 Buatlah tabel kebenaran untuk gambar rangkaian berikut : Jawab : Persamaan logika dari rangkaian tersebut : Y = AB + CD Arti persamaan di atas : Y akan berlogika 1, jika AB = 1 atau CD = 1 AB = 1, jika A = 1 dan B = 1 CD = 1, jika C = 1 dan D = 1 Maka Y = 1 jika : A = 1 dan B = 1 atau C = 1 dan D = 1 Selain itu Y = 0 Sehingga bisa dibuat tabel kebenaran sebagai berikut : A B C D Y 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 0 1 1 1 0 1 0 0 0 0 1 0 1 0 0 1 1 0 0 0 1 1 1 1 1 0 0 0 0 1 0 0 1 0 40 1 0 1 0 0 1 0 1 1 1 1 1 0 0 1 1 1 0 1 1 1 1 1 0 1 1 1 1 1 1 Dari contoh di atas, bisa dibayangkan repotnya jika kita membuat tabel kebenaran dengan cara mencari keluaran dari semua gerbang untuk seluruh kombinasi input. Jika input ada 3, maka kita akan mencari keluaran untuk 8 kombinasi input. Jika input ada 4, maka akan ada 16 kombinasi input. Jadi, untuk n input akan menghasilkan 2n kombinasi input. 3.6 Implementasi Rangkaian Logika Kemampuan mengimplementasikan rangkaian berdasarkan persamaan logika adalah sangat penting, karena setiap rancangan rangkaian logika akan menghasilkan persamaan logika, dan agar dapat dimanfaatkan dalam bentuk nyata maka persamaan tersebut perlu diimplementasikan atau direalisasikan. Contoh 3.6 Implementasikan persamaan logika Y = A BC + ABC + A B ke dalam bentuk rangkaian logika. Jawab : • Berdasarkan persamaan tersebut terlihat bahwa terdapat 3 suku persamaan yaitu A BC , ABC , dan A B . Ketiga suku tersebut dioperasikan dengan operator “tambah”, sehingga diperlukan gerbang 1 buah gerbang OR 3 input. • Selanjutnya, terlihat bahwa suku-suku persamaan merupakan operasi AND dari variable-variabel input, untuk suku-1 dan suku-2 memerlukan 2 buah gerbang AND 3 input, dan suku-3 memerlukan 1 buah gerbang AND 2 input. • Terdapat pula 4 buah operasi NOT, sehingga diperlukan 4 buah gerbang NOT. 41 • 3.7 Jadi rangkaian logikanya adalah : Hukum dan Aturan Aljabar Boole Berikut ini merupakan hukum-hukum Aljabar Boole : 1. Hukum Komutatif :A+B=B+A A.B=B.A 2. Hukum Asosiatif : A+(B+C) = (A+B)+C A(BC)=(AB)C 3. Hukum Distributif : A(B+C) = AB + AC A+(BC) = (A+B).(A+C) Di samping hukum dasar aljabar boole, juga terdapat aturan-aturan mengenai Aljabar Boole. Aturan-aturan aljabar boole terdiri dari satu variable sehingga bentuk rangkaian ekivalennya menjadi lebih sederhana. Berikut ini aturan-aturan pada aljabar boole : • Aturan 1 : Setiap bilangan yang dikalikan atau di-AND-kan dengan 0 akan menghasilkan keluaran 0. A⋅0 = 0 • Aturan 2 : Setiap bilangan yang dikalikan atau di-AND-kan dengan 1 akan menghasilkan bilangan itu sendiri. A ⋅1 = A • Aturan 3 : Perkalian dua buah bilangan maka hasilnya adalah bilangan itu sendiri. A⋅ A = A • Aturan 4 : Setiap bilangan yang dikalikan atau di-AND-kan dengan komplemennya akan menghasilkan 0. 42 A⋅ A = 0 • Aturan 5 : Setiap bilangan yang ditambahkan atau di-OR-kan dengan 0 akan menghasilkan bilangan itu sendiri. A+0 = A • Aturan 6 : Setiap bilangan yang ditambahkan atau di-OR-kan dengan 1 akan menghasilkan 1. A +1 = 1 • Aturan 7 : Penjumlahan dua buah bilangan akan menghasilkan bilangan itu sendiri. A+ A = A • Aturan 8 : Setiap bilangan yang dijumlahkan atau di-OR-kan dengan komplemennya akan menghasilkan 1. A+ A =1 • Aturan 9 : Suatu bilangan yang dikomplemenkan dua kali, maka akan dihasilkan bilangan itu sendiri. A= A • Aturan 10 : A + AB = A + B Penjabaran : A + AB = A(1 + B ) + AB = A + AB + AB = A + B ( A + A) , A+ A =1 , A+ A =1 A + AB = A + B • Aturan 11 : A + AB = A + B Penjabaran : A + AB = A(1 + B ) + AB = A + AB + AB = A + B ( A + A) A + AB = A + B 43 Aturan 10 dan aturan 11 berbeda dengan aturan yang sebelumnya karena terdiri dari dua variabel. Aturan ini berguna untuk menyederhanakan persamaan dimana satu atau lebih variabel dapat dihilangkan. Pembuktian berdasarkan tabel kebenaran dari dua persamaan tersebut dapat dilihat pada tabel berikut : Tabel 3.7. Pembuktian Aturan 10 dan 11 A B A + AB A+B A + AB A+ B 0 0 0 0 1 1 0 1 1 1 1 1 1 0 1 1 0 0 1 1 1 1 1 1 Aturan-aturan aljabar boole di atas dapat dirangkumkan sebagai berikut : 1. A ⋅ 0 = 0 2. A ⋅ 1 = A Operasi 3. A ⋅ A = A AND 4. A ⋅ A = 0 5. A + 0 = A 6. A + 1 = 1 Operasi 7. A + A = A OR 8. A + A = 1 9. A = A 10. A + AB = A + B 11. A + AB = A + B Teorema de Morgan Teorema de Morgan ini sangat berguna untuk menyederhanakan persamaan rangkaian yang menggunakan gerbang NAND dan NOR. Teorema de Morgan ada 2, yaitu : 1. A⋅ B = A + B (untuk dua variabel) 44 A⋅ B ⋅C = A + B + C (untuk tiga variabel) Gerbang NAND ekivalen dengan rangkaian yang meng-OR-kan seluruh komplemen input. Hal ini dapat dilihat pada gambar berikut : Gambar 3.22. Bentuk Grafis Teorema de Morgan pertama 2. A + B = A⋅ B (untuk dua variabel) A + B + C = A⋅ B ⋅C (untuk tiga variabel) Gerbang NOR ekivalen dengan rangkaian yang meng-AND-kan seluruh komplemen input. Hal ini dapat dilihat pada gambar berikut : Gambar 3.23. Bentuk Grafis Teorema de Morgan kedua 3.8 Teknik Bubble Pushing Teknik bubble pushing adalah : suatu metode untuk membentuk rangkaian logika ekivalen berdasarkan Teorema De Morgan. Cara untuk merubah rangkaian logika ekivalen ini ada 2 (dua) langkah, yaitu: a. Merubah gerbang logika (gerbang AND menjadi OR dan gerbang OR menjadi AND) b. Tambahkan bubble jika pada gerbang logika asli tidak terdapat bubble (baik pada input maupun output). Sebaliknya jika pada gerbang logika yang asli terdapat bubble maka pada rangkaian logika ekivalennya bubble dihilangkan. Untuk lebih jelasnya tentang cara membuat rangkaian logika ekivalen, dapat dilihat pada gambar 3.24 berikut : 45 Gambar 3.24. Rangkaian Logika Asli dan Rangkaian Ekivalen dengan menggunakan Teknik Bubble Pushing Pembuktian metode ini dapat dilakukan dengan cara membandingkan tabel kebenarannya antara rangkaian logika yang asli dengan rangkaian logika ekivalennya. 3.9 Gerbang NAND dan NOR sebagai Gerbang Universal Gerbang yang paling sering digunakan untuk membentuk rangkaian kombinasi adalah gerbang NAND dan NOR dibandingkan gerbang AND dan OR. Dari sisi aplikasi perangkat luar gerbang NAND dan NOR lebih umum sehingga gerbang NAND dan NOR dikenal sebagai gerbang yang “universal”. Alasannya adalah banyak sistem digital dapat dengan mudah diimplementasikan dengan gerbang universal tersebut, baik rangkaian kombinasi maupun rangkaian sekuensial. Selain itu gerbang NAND dan gerbang NOR lebih banyak tersedia di pasaran dibandingkan dengan gerbang AND dan OR. Berdasarkan alasan itu, maka terkadang kita perlu melakukan modifikasi rangkaian dengan menggunakan gerbang NAND dan NOR. Modifikasi dari gerbang logika dasar ke gerbang logika NAND atau NOR ada 2 metode, yaitu : 46 1. Modifikasi dari persamaan logika Modifikasi ke gerbang NAND 1. Y = A → Y = A⋅ A 2. Y = A ⋅ B → Y = A⋅ B 3. Y = A + B → atau Y = A ⋅1 Y = A+ B → Y = A⋅ B Modifikasi ke gerbang NOR 1. Y = A → Y = A+ A atau Y = A+0 2. Y = A ⋅ B → Y = A⋅ B → Y = A+ B 3. Y = A + B → Y = A+ B 2. Modifikasi dari diagram gerbang logika Pemodifikasian dari gerbang logika dasar ke dalam gerbang NAND berdasarkan diagram gerbang logika dapat dilihat pada gambar berikut : Gerbang Dasar Gerbang yang dimanipulasi ke NAND Gambar 3.25. Konversi Gerbang Universal ke Gerbang NAND Modifikasi gerbang logika dasar ke dalam gerbang NOR berdasarkan diagram gerbang logika dapat dilihat pada gambar berikut : 47 Gerbang Dasar Gerbang yang dimanipulasi ke NOR Gambar 3.26. Konversi Gerbang Universal ke Gerbang NOR Contoh 3.7 Modifikasi rangkaian berikut dengan menggunakan gerbang NAND saja dan NOR saja dengan menggunakan metode persamaan logika dan metode diagram gerbang logika ! Jawab : Metode persamaan logika Modifikasi ke dalam bentuk NAND saja Y = ( A ⋅ B) + C = ( A ⋅ B) + C = ( A ⋅ B) ⋅ C Rangkaian Logika : Modifikasi ke dalam bentuk NOR saja Y = ( A ⋅ B) + C = ( A ⋅ B) + C = ( A + B ) + C 48 Rangkaian Logika : Metode Diagram Gerbang Logika Modifikasi ke dalam bentuk NAND saja Rangkaian tsb dapat disederhanakan menjadi : Modifikasi ke dalam bentuk NOR saja 3.10 Bentuk Kanonik Sebuah variabel biner X mempunyai dua keadaan, yaitu X dan X , dan variable Y mempunyai dua keadaan Y dan Y . Jika dua variable X dan Y digabungkan dengan operasi AND maka akan ada empat kemungkinan kombinasi input yaitu : XY , X Y , X Y , dan X Y . Masing-masing dari empat kemungkinan itu 49 dinamakan dengan Minterm. Jadi, minterm adalah n variabel yang membentuk operasi AND yang menghasilkan suatu persamaan. Jika dua variable X dan Y digabung dengan operasi OR, maka empat kemungkinan kombinasi yang muncul adalah : X + Y , X + Y , X + Y , dan X + Y . Masing-masing dari empat kemungkinan itu dinamakan dengan Maxterm. Jadi, maxterm adalah n variabel yang membentuk operasi OR yang menghasilkan suatu persamaan. Tabel 3.8 Tabel Minterm dan Maxterm 3 Variabel Minterm X Y Maxterm Z Term Lambang Term Lambang 0 0 0 XYZ m0 X +Y + Z M0 0 0 1 X YZ m1 X +Y + Z M1 0 1 0 XY Z m2 X +Y + Z M2 0 1 1 X YZ m3 X +Y + Z M3 1 0 0 XYZ m4 X +Y + Z M4 1 0 1 X YZ m5 X +Y + Z M5 1 1 0 XY Z m6 X +Y + Z M6 1 1 1 XYZ m7 X +Y + Z M7 Dari table di atas, nampak bahwa setiap maxterm merupakan komplemen dari minterm yang bersesuaian dan begitu juga sebaliknya. Tabel 3.9. Fungsi dengan 3 Variabel X Y Z F1 F2 0 0 0 0 0 0 0 1 1 0 0 1 0 0 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 50 1 1 0 0 1 1 1 1 1 1 Suatu fungsi atau persamaan boole dapat dibuat dari suatu table kebenaran yang dibentuk dari minterm setiap kombinasi input yang menghasilkan output 1 dan kemudian meng-OR-kan semua minterm tersebut. Misalnya, fungsi F1 pada table 3.9 di atas dihasilkan dari kombinasi 001, 100, dan 111, sehingga bentuk persamaan fungsinya menjadi : F1 = X Y Z + X Y Z + XYZ = m1 + m4 + m7 Dengan cara yang sama diperoleh fungsi F2, yaitu : F2 = X YZ + X Y Z + XY Z + XYZ = m 3 + m5 + m 6 + m7 Dari contoh di atas, dapat dilihat bahwa setiap fungsi boole dapat dinyatakan sebagai suatu sum of minterm. Komplemen fungsi boole dapat dibaca dari table kebenaran di atas (table 3.9) dengan membentuk minterm dari setiap kombinasi input yang menghasilkan 0 dalam fungsi tersebut. Komplemen F1 adalah : F1 = X Y Z + X Y Z + X YZ + X Y Z + XY Z Jika fungsi F1 dikomplemenkan lagi, maka akan diperoleh : F1 = X Y Z + X Y Z + X YZ + X Y Z + XY Z F1 = ( X + Y + Z ) ( X + Y + Z ) ( X + Y + Z ) ( X + Y + Z ) ( X + Y + Z ) = M0 + M2 + M3 + M5 + M6 Dengan cara yang sama diperoleh fungsi F2, yaitu : F2 = ( X + Y + Z ) ( X + Y + Z ) ( X + Y + Z ) ( X + Y + Z ) = M0 + M1 + M2 + M4 Dari contoh di atas, dapat dilihat bahwa setiap fungsi boole dapat dinyatakan sebagai suatu sum of maxterm Jadi, fungsi boole dapat dinyatakan dalam bentuk sum of minterm atau sum of maxterm, yang biasa disebut bentuk kanonik. 51 3.10.1 Sum of Minterm atau Sum of Product Telah diuraikan sebelumnya, bahwa n variable input akan menghasilkan 2n minterm yang berbeda, dan setiap fungsi boole dapat dinyatakan dalam bentuk sum of minterm dan sum of maxterm. Kadang-kadang lebih mudah untuk menyatakan fungsi Boole tersebut dalam sum of minterm. Jika tidak tersedia dalam bentuk itu, dapat dibentuk dengan menguraikannya menjadi suatu bentuk penjumlahan dari operasi AND. Nama lain dari sum of minterm adalah sum of product. Contoh 3.8 Nyatakan fungsi Boole F = A + BC dalam bentuk sum of minterm. Jawab : Fungsi tersebut mempunyai 3 variabel , yaitu A, B, dan C. Term pertama hanya mengandung variable A, sehingga kurang 2 variabel, maka : A = A( B + B ) = AB + A B A = AB (C + C ) + A B (C + C ) = ABC + ABC + A BC + A BC Term kedua masih kurang 1 varibel, maka : BC = BC ( A + A) = A BC + A BC Dengan menggabungkan term pertama dan kedua, maka didapat : F = A + BC = ABC + ABC + ABC + ABC + ABC + ABC ABC muncul dua kali, dan sesuai dengan aturan 7, X + X = X, maka salah satunya bisa dihilangkan, sehingga persamaannya menjadi : F = A + BC = ABC + ABC + ABC + ABC + ABC = m1 + m4 + m5 + m6 + m7 Untuk memudahkan penulisan, persamaan di atas dapat dinyakan dengan notasi : F ( A, B, C ) = ∑ (1,4,5,6,7) Keterangan notasi di atas : • Lambang penjumlahan Σ menyatakan penjumlahan atau peng-OR-an minterm 52 • Angka 1,4,5,6,7 merupakan nomor minterm • Huruf A,B,C merupakan variabel yang dipakai oleh minterm Dari sebuah tabel kebenaran dapat diperoleh persamaan logikanya. Cara membuat persamaan sum of minterm dari sebuah tabel kebenaran dapat dilakukan dengan melakukan operasi OR untuk setiap minterm yang mempunyai nilai keluaran tinggi. Contoh 3.9 Nyatakan F dalam persamaan sum of minterm untuk tabel kebenaran berikut : X Y Z F 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 Jawab : F = X Y Z + X Y Z + XYZ = m1 + m4 + m7 Persamaan di atas dapat ditulis dengan menggunakan notasi singkat : F(X,Y,Z) = Σ(1,4,7) 3.10.2 Sum of Maxterm atau Product of Sum Nama lain dari Sum of Maxterm adalah Product of Sum. Untuk menyatakan fungsi Boole dalam sum of maxterm, fungsi tersebut harus dalam bentuk fungsi OR. Hal ini dilakukan dengan menggunakan hukum distributif X + YZ = (X + Y) (X + Z). Untuk lebih jelasnya dapat dilihat pada contoh berikut : 53 Contoh 3.10 Nyatakan fungsi Boole F = XY + X Z dalam bentuk sum of maxterm. Jawab : Pertama, fungsi tersebut diubah menjadi bentuk OR dengan menggunakan hukum distributif. F = XY + X Z = ( XY + X )( XY + Z ) = ( X + X )(Y + X )( X + Z )(Y + Z ) = ( X + Y )( X + Z )(Y + Z ) Fungsi tersebut mempunyai 3 variabel X,Y, dan Z. Masing-masing bentuk OR mempunyai variabel yang tersebunyi, oleh karena itu : X +Y = X +Y + ZZ = ( X + Y + Z )( X + Y + Z ) X + Z = X + YY + Z = ( X + Y + Z )( X + Y + Z ) Y + Z = X X +Y + Z = ( X + Y + Z )( X + Y + Z ) Dengan menggabungkan semua term tersebut dan menghilangkan term yang muncul lebih dari satu kali, maka didapat : F = ( X + Y + Z )( X + Y + Z )( X + Y + Z )( X + Y + Z ) = M 0M 2M 4M 5 Bentuk persamaan notasi : F ( X , Y , Z ) = Π (0, 2,4,5) Keterangan notasi di atas : • Lambang penjumlahan Π menyatakan peng-AND-an maxterm • Angka 0,2,4,5 merupakan nomor maxterm • Huruf X,Y,Z merupakan variabel yang dipakai oleh maxterm Cara membuat persamaan sum of maxterm dari sebuah tabel kebenaran dapat dilakukan dengan operasi AND untuk setiap maxterm yang mempunyai nilai keluaran rendah. 54 Contoh 3.11 Nyatakan F dalam persamaan sum of maxterm untuk tabel kebenaran berikut : X Y Z F 0 0 0 0 0 0 1 1 0 1 0 0 0 1 1 0 1 0 0 1 1 0 1 0 1 1 0 0 1 1 1 1 Jawab : F = ( X + Y + Z )( X + Y + Z )( X + Y + Z )( X + Y + Z ) + ( X + Y + Z ) = M 0M 2M 3M 5M 6 Persamaan di atas dapat ditulis dengan menggunakan notasi singkat : F(X,Y,Z) = Π(0,2,3,5,6) 3.10.3 Perubahan Bentuk Kanonik Jika suatu fungsi sum of minterm adalah : F(A,B,C) = Σ (1,4,5,6,7) maka fungsi komplemennya adalah : F ( A, B, C ) = Σ(0,2,3) = m0 + m2 + m3 Jika F dikomplemenkan kembali akan diperoleh F kembali, dan digunakan teorema de morgan pada minterm, maka : F ( A, B, C ) = ( m0 + m 2 + m3 ) = m 0 ⋅ m 2 ⋅ m3 = M 0 ⋅ M 2 ⋅ M 3 = Π (0,2,3) Perubahan terakhir merupakan definisi dari minterm dan maxterm seperti yang terdapat pada tabel 3.8. Dari tabel terlihat hubungan : 55 mj = M j Jadi secara umum, untuk mengubah salah satu bentuk kanonik ke bentuk kanonik lain cukup dilakukan dengan menukar lambang Σ dengan Π, dan ditulis semua bilangan yang tidak ada dalam bentuk aslinya, begitu juga sebaliknya. Contoh 3.10 Nyatakan fungsi Boole F ( X , Y , Z ) = Π (0,2,4,5) ke dalam bentuk sum of minterm. Jawab : F ( X , Y , Z ) = Σ(1,3,6,7) Catatan : Perlu diingat di sini, jumlah minterm dan maxterm untuk n variabel adalah 2n. 3.11 1. Soal-soal Latihan Buktikan kedua Teorema de Morman dengan cara menurunkan tabel kebenaran. 2. Modifikasilah persamaan atau rangkaian logika di bawah ini dengan menggunakan gerbang NAND saja dan NOR saja ! a. F = AB + ABC b. c. 56 3. Konversikan persamaan berikut menjadi bentuk NOR saja dan gambarkanlah rangkaiannya : ( F = (A + B ) A + C 4. ) Implementasikan fungsi berikut yang menggunakan keadaan tak-acuh (don’t care), dengan tidak lebih dari 2 buah gerbang NOR. Andaikan masukan normal dan komplemennya tersedia. F = ABC + ABD + ABC D F d = ABC + AB D 5. 6. Buktikan bahwa gambar (a) dan (b) adalah ekivalen ! Buatlah rangkaian padanan dari rangkaian logika di bawah ini menjadi rangkaian logika yang terdiri dari gerbang AND, OR, dan NOT. Buktikan kebenarannya menggunakan tabel kebenaran. 7. Turunkan tabel kebenaran keluaran F1 dan F2 untuk rangkaian di bawah ini : 8. Diketahui tabel kebenaran sebagai berikut : 57 x y z F1 F2 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1 Nyatakan F1 dan F2 dalam persamaan sum of product / sum of minterm dan product of sum / sum of maxterm, kemudian buat rangkaian logika untuk persamaan-persamaan tersebut. 9. Nyatakan fungsi berikut menjadi sum of minterm dan product of maxterm : F(A,B,C,D) = D(A’+B) + B’D F(W,X,Y,Z) = Y’Z + WXY’ + WXZ’ + W’X’Z F(A,B,C) =A’B+B’C 10. Ubahlah fungsi berikut menjadi bentuk kanonik yang lain : a. F(X,Y,Z) = Σ (1,3,7) b. F(A,B,C,D) = Π(0,2,6,11,13,14) c. F(X,Y,Z) = Σ (0,3,6,7) d. F(A,B,C,D) = Π(0,1,2,3,4,6,12) 58