KOMPUTASI

advertisement

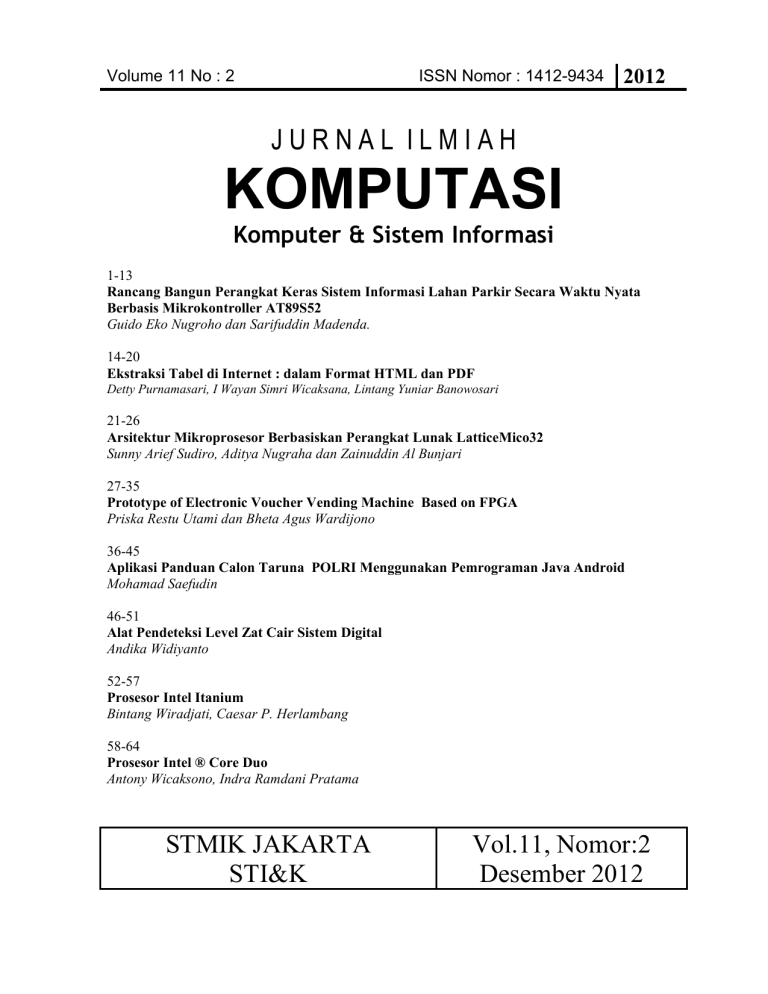

Volume 11 No : 2 ISSN Nomor : 1412-9434 2012 JURNAL ILMIAH KOMPUTASI Komputer & Sistem Informasi 1-13 Rancang Bangun Perangkat Keras Sistem Informasi Lahan Parkir Secara Waktu Nyata Berbasis Mikrokontroller AT89S52 Guido Eko Nugroho dan Sarifuddin Madenda. 14-20 Ekstraksi Tabel di Internet : dalam Format HTML dan PDF Detty Purnamasari, I Wayan Simri Wicaksana, Lintang Yuniar Banowosari 21-26 Arsitektur Mikroprosesor Berbasiskan Perangkat Lunak LatticeMico32 Sunny Arief Sudiro, Aditya Nugraha dan Zainuddin Al Bunjari 27-35 Prototype of Electronic Voucher Vending Machine Based on FPGA Priska Restu Utami dan Bheta Agus Wardijono 36-45 Aplikasi Panduan Calon Taruna POLRI Menggunakan Pemrograman Java Android Mohamad Saefudin 46-51 Alat Pendeteksi Level Zat Cair Sistem Digital Andika Widiyanto 52-57 Prosesor Intel Itanium Bintang Wiradjati, Caesar P. Herlambang 58-64 Prosesor Intel ® Core Duo Antony Wicaksono, Indra Ramdani Pratama STMIK JAKARTA STI&K Vol.11, Nomor:2 Desember 2012 PENGASUH JURNAL ILMIAH KOMPUTASI Pelindung: Prof. ES. Margianti, SE., MM Prof. Suryadi H.S., SSi., MM Drs. Agus Sumin, MMSI JURNAL ILMIAH KOMPUTASI Komputer & Sistem Informasi DAFTAR ISI Penanggung Jawab: Prof. Dr. Sarifuddin Madenda Dewan Redaksi/Reviewer: 1. 2. 3. 4. 5. 6. 7. 8. Prof. Dr. Didin Mukhodim Drs. Tjahjo Dwinurti T., MM Prof. Dr. Sarifuddin Madenda Dr. Lussiana ETP Hj. Latifah, SSi., MMSI Rosalina Lokolo, SE., MM Eko Hadiyanto, SSi., MMSI Dr. Pipit Dewi Arnesia Pimpinan Pelaksana Redaksi : Ire Puspa Wardhani, SKom., MM Editor dan Layout: 1. Dr. Sunny Arief Sudiro 2. Dr. Bheta Agus Wardijono 3. Yudi Irawan Chandra, SKom., MMSI Sekretariat Redaksi 1. Sahni Damerianta P, SKom., MMSI (Koordinator) 2. Don Elsyafitra, SKom (Pj. Web) 3. Maria Sri Wulandari, (Pj. Adm) Adm dan Sirkulasi : 1. Edi Pranoto, SE., MM 2. Fitri Sjafrina, SKom., MMSI 3. Sunarto Usna, Drs., MMSI Alamat Redaksi : Kampus STMIK Jakarta STI&K Jln. BRI Radio Dalam Kebayoran Baru Jakarta Selatan Telp. (021) 7397973, 7210722 Fax. (021) 7210720 Email : info@ stmik-jakarta.ac.id ISSN Nomor 1412-9434 Volume 11 Nomor 2 Tahun 2012 Redaksi menerima sumbangan naskah berupa artikel, hasil penelitian, atau karya ilmiah yang belum pernah dan tidak akan dipublikasikan di media lain. Naskah sudah diterima redaksi selambat-lambatnya tanggal 10 sebelum bulan penerbitan. 1-13 Rancang Bangun Perangkat Keras Sistem Informasi Lahan Parkir Secara Waktu Nyata Berbasis Mikrokontroller AT89S52 Guido Eko Nugroho dan Sarifuddin Madenda. 14-20 Ekstraksi Tabel di Internet : dalam Format HTML dan PDF Detty Purnamasari, I Wayan Simri Wicaksana, Lintang Yuniar Banowosari 21-26 Arsitektur Mikroprosesor Berbasiskan Perangkat Lunak LatticeMico32 Sunny Arief Sudiro, Aditya Nugraha dan Zainuddin Al Bunjari 27-35 Prototype of Electronic Voucher Vending Machine Based on FPGA Priska Restu Utami dan Bheta Agus Wardijono 36-45 Aplikasi Panduan Calon Taruna POLRI Menggunakan Pemrograman Java Android Mohamad Saefudin 46-51 Alat Pendeteksi Level Zat Cair Sistem Digital Andika Widiyanto 52-57 Prosesor Intel Itanium Bintang Wiradjati, Caesar P. Herlambang 58-64 Prosesor Intel ® Core Duo Antony Wicaksono, Indra Ramdani Pratama Jurnal Komputasi, Volume 11 No: 2 Desember 2012 ISSN: 1412-9434 Arsitektur Mikroprosesor Berbasiskan Perangkat Lunak LatticeMico32 Sunny Arief Sudiro, Aditya Nugraha dan Zainuddin Al Bunjari STMIK Jakarta STI&K, Jur. Teknik Elektro, Fak.Teknologi Industri, Universitas Gunadarma [email protected] Abstrak LatticeMico32 adalah mikroprosesor 32-bit soft core yang dibuat oleh Lattice Semiconductor yang dioptimasikan penggunaannya untuk FPGA (eld-programmable gate arrays). Arsitekturnya menggunakan Harvard Architecture, dimana instruksi dan bus data diletakkan terpisah. LatticeMico32 menggunakan RISC untuk set instruksinya yang memungkinkan untuk mengirimkan set instruksi yang lebih simple dan performa lebih cepat. Sebagai hasilnya, prosesor ini mengkonsumsi daya sumber lebih rendah untuk melakukan kinerja yang dibutuhkan untuk aplikasi. : architecture, microprocessor, CPU, WISHBONE, instruction set, commands, registers, Kata Kunci 1 Pendahuluan LatticeMico32 adalah mikroprosesor 32-bit soft core yang dibuat oleh Lattice Semiconductor yang dioptimasikan penggunaannya untuk FPGA (eld-programmable gate arrays). LatticeMico ini bersifat opensource [1], dimana pengguna bisa melakukan perubahan-perubahan ke arsitektur prosesor LatticeMico sesuai dengan device yang akan digunakan. Arsitekturnya menggunakan Harvard architecture, dimana instruksi dan bus data diletakkan terpisah. Dengan set instruksi dan bus data yang terpisah, prosesor ini mampu mengeksekusi instruksi dan data memori secara bersamaan hanya menggunakan satu cycle. LatticeMico32 menggunakan RISC (Reduced instruction set computing) untuk set instruksinya yang memungkinkan untuk mengirimkan set instruksi yang lebih simple dan performa lebih cepat. Sebagai hasilnya, prosesor ini mengkonsumsi daya sumber lebih rendah untuk melakukan kinerja yang dibutuhkan untuk aplikasi. LatticeMico32 mempunyai tur, antara lain: RISC load/store architecture, 32-bit data path, 32-bit xed-size instructions (semua instruktur berupa 32 bits, termasuk jump, call and branch instructions), 32 general purpose registers, Up to 32 external interrupts, Set instruksi yang dapat diatur sendiri, Optional congurable caches, Optional pipelined memories, Dual Wishbone memory interfaces (one read-only instruction bus, one read-write data/peripheral bus), Memory mapped I/O, 6 stage pipeline. 2 Pipeline Architecture LatticeMico32 menggunakan 32-bit, 6-stage pipeline seperti yang terlihat pada gambar diatas. Pipeline ini saling bertautan dan mengelilingi satu sama lain. Bypass logic bertanggung jawab untuk mengirim hasil kembali melalui pipeline, sehingga instruksi-instruksi tersebut dapat dieksekusi dalam satu cycle (single-cycle). Saling bertautan maksudnya adalah mendeteksi hambatan ketika proses read-after-write terjadi dan menunda pipeline sampai hambatan tersebut selesai diatasi. Enam pipeline stage tersebut antara lain : • Address Alamat dari instruksi yang akan dieksekusi dihitung dan dikirim ke cache instruksi. 21 Jurnal Komputasi, Volume 11 No: 2 Desember 2012 ISSN: 1412-9434 • Fetch Instruksi nya dibaca melalui mem- ports, timer 32-bit, sebuah DMA controller, ori. general-purpose I/O (GPIO), sebuah I2C master controller, serial peripheral interface (SPI), • Decode Instruksi didekode, dan operan dan UART. Plug pada peripheral secara dramayang ada diambil dari le register atau di- tis mempercepat desain sistem, menghilangkan ambil dari pipeline sebelumnya. kebutuhan untuk code-custom dari banyak fungsi • Execute Operasi yang sesuai dengan in- perangkat keras umum jika akan membangun sebuah sistem Mico32 berbasis embedded system struksi tadi dijalankan. Untuk instruksi [2]. sederhana seperti penjumlahan atau operasi logika, akan berhenti di proses ini, dan hasilnya dapat dikirimkan kembali ke proses awal. 4 Register Architecture • Memory Untuk instruksi kompleks seperti Ada dua macam register yang disediakan, load, store, perkalian, shift diperlukan General-Purpose Registers dan Control and Stastage eksekusi tambahan. tus Register. • Writeback Hasil yang diproduksi oleh instruksi dikirim balik ke le register. 4.1 General-Purpose Registers LatticeMico32 memiliki tur 32-bit register dengan aturan: • Berdasarkan kesepakatan, register 0 (r0) harus selalu memegang nilai 0, dan ini diperlukan untuk operasi yang tepat oleh kedua assembler LatticeMico32 dan C compiler. Pada saat dimulai, nilai 0 dalam r0 tidak terprogram, sehingga harus diinisialisasi untuk memuat r0 dengan nilai 0. Gambar 1: Blok diagram Latticemico32. Gambar 1 memperlihatkan blok diagram dari LatticeMico32, dimana terjadinya enam tahap pipeline tersebut secara berurutan mengikuti alur process dari blok diagram tersebut. 3 LatticeMico32 Interface Sesuai dengan pendekatan open source, Lattice memilih antar muka Wishbone untuk Mico32 dan telah mengumumkan berbagai peripheral yang tersedia, termasuk memory controllers, asynchronous SRAM, onchip block memory, I/O • Register 1 sampai 28 adalah benar-benar untuk tujuan umum dan dapat digunakan sebagai sumber atau register tujuan untuk instruksi apapun. Setelah reset, nilai-nilai dalam semua register tidak terdenisi. • Register 29 (ra) digunakan oleh instruksi call untuk menyimpan return address namun ini tujuannya umum. • Register 30 (ea) digunakan untuk menyimpan nilai Program Counter (PC) ketika pengecualian terjadi, sehingga tidak boleh digunakan oleh user-level program. • Register 31 (ba) menyimpan nilai Program Counter (PC) saat breakpoint atau watchpoint exception terjadi, sehingga tidak boleh digunakan oleh user-level program. 22 Jurnal Komputasi, Volume 11 No: 2 Desember 2012 ISSN: 1412-9434 4.2 Control and Status Register Control dan status register merupakan register yang berfungsi untuk mengatur control dari processor dan membantunya dalam menjalankan instruksi. Berikut merupakan Control dan status register, • PC - Program Counter CSR PC adalah register 32-bit yang berisi alamat dari instruksi yang sedang dieksekusi. Karena semua instruksi yang empat byte lebar, dua bit paling signikan dari PC selalu nol. Setelah reset, nilai CSR PC h00000000. • EID - ID Exception CSR EID adalah nilai 3-bit yang menunjukkan apa yang menyebabkan eksekusi program berhenti. Nilainilai dan peristiwa yang sesuai adalah sebagai berikut: 0 Reset 1 Breakpoint Exception 2 Instruction Bus Error 3 Watchpoint Exception 4 Data Bust Error 5 Divide-by-zero 6 Interrupt 7 System Call • IP - Interrupt Pending CSR IP berisi pending bit untuk masing-masing dari 32 interupsi. Sebuah pending bit diset ketika interrupt yang sesuai dengan permintaan dinyatakan low. Bit 0 bersesuaian menginterupsi 0. Bit dalam CSR IP dapat dihapus dengan menulis 1 dengan instruksi wcsr. Menulis 0 tidak akan memiliki efek. Setelah reset, nilai CSR IP h00000000. • ICC - Instruksi Control Cache CSR ICC menyediakan bit kontrol bahwa ketika ditulis dengan nilai apapun, menyebabkan isi dari cache instruksi seluruh untuk menjadi tidak absah. • DCC - Data Control Cache CSR DCC menyediakan bit kontrol yang ketika ditulis dengan nilai apapun, menyebabkan isi dari cache seluruh data akan batal. • CC - Counter Siklus CSR CC adalah register 32-bit optional yang ditambah satu pada setiap siklus clock. Hal ini dapat digunakan untuk sekuens prole ghost code. • CFG - Conguration CFG CSR merincikan kongurasi-kongurasi contoh tertentu dari sebuah prosesor LatticeMico32. • EBA - Exception Basis Address CSR EBA menetapkan alamat dasar dari handler pengecualian. Setelah reset, nilai EBA diatur ke EBA_RESET. Jika menulis nilai ke register di mana byte yang rendah tidak nol, maka akan dibaca kembali semua nol. • IE - Interrupt Enable IE CSR berisi satu ag-bit, IE, yang menentukan apakah interupsi diaktifkan. Flag ini memiliki prioritas terhadap CSR IM. Selain itu, ada dua bit, BIE dan EIE, yang digunakan 5 Memory Architecture untuk menunjukkan nilai eld IE ketika baik breakpoint atau pengecualian lain ter- Pada bagian ini akan dibahas mengenai arsitekjadi. Setiap interupsi terkait dengan sedikit tur memori. mask (IE bit) diindeks dengan interupsi masing-masing. Setelah reset, nilai IE CSR 5.1 Address Space h00000000. Untuk LatticeMico32 prosesor dengan cache, • IM Interrupt Mask CSR IM berisi bit en- bagian dari ruang alamat yang disimpan di cache able untuk masing-masing 32 interupsi. Bit dapat dikongurasi secara terpisah baik untuk in0 bersesuaian menginterupsi 0.Supaya se- struksi dan data cache. Ini memungkinkan ukubuah interrupt akan dibangkitkan, baik en- ran dari cache tag RAM menjadi sekecil mungkin able bit dalam register ini dan ag IE dalam (semakin kecil nilai cache address, semakin kecil CSR IE harus diset ke 1. Setelah reset, nilai tag RAM). Gambar 2 menggambarkan beberapa CSR IM h00000000. kemungkinan kongurasi. Biasanya, bagian dari 23 Jurnal Komputasi, Volume 11 No: 2 Desember 2012 ISSN: 1412-9434 ruang alamat yang disimpan di cache digunakan untuk menyimpan kode atau data program, dengan komponen I / O yang dipetakan ke dalam alamat uncacheable. jumlah sumber daya FPGA digunakan. Instruksi yang berakhir dengan huruf "i" menggunakan nilai langsung bukan register. Instruksi yang berakhir dengan "hi" menggunakan 16-bit langsung dan high 16 bit dari register. Instruksi yang berakhir dengan huruf "u" menangani data sebagai unsigned integer. Gambar 2: Cacheable Address. 5.2 Endianness Prosesor LatticeMico32 adalah big-endian, yang berarti bahwa multi-byte objek, seperti half-words and words, tersimpan dengan most signicant byte pada lowest address. 5.3 Gambar 3: Stack Layout Stack layout Gambar 3 menunjukkan tata letak konvensional frame stack. Stack bertambah ke arah memori lebih rendah karena data dimasukkan ke atasnya. Stack pointer (sp) menunjuk ke lokasi yang tidak digunakan pertama, dan frame pointer (fp) menunjukkan lokasi pertama kali yang digunakan ketika frame aktif. Dalam banyak kasus, sebuah compiler mungkin dapat menghilangkan frame pointer, karena data sering dapat diakses dengan menggunakan perpindahan negatif dari stack pointer, membebaskan frame pointer untuk digunakan sebagai register general-purpose. 6 Instruction Set Categories LatticeMico32 mendukung berbagai instruksi untuk aritmatika, perbandingan, data logika, pergerakan data, dan kontrol program. Tidak semua instruksi yang tersedia dalam semua kongurasi prosesor. Support untuk beberapa jenis instruksi dapat dihilangkan untuk mengurangi 6.1 Arithmetic Set instruksi meliputi 32-bit operasi standar aritmatika integer. Dukungan untuk perkalian dan instruksi pembagian adalah opsional. • Add: add, addi • Subtract: sub • Multiply: mul, muli • Divide and modulus: divu, modu Terdapat juga instruksi untuk sign-extend byte dan setengah kata data untuk ukuran kata. Dukungan untuk instruksi ini adalah opsional. • Sign-extend: sextb, sexth 6.2 Logic Set instruksi meliputi 32-bit operasi bitwise standar logika. Sebagian besar instruksi logika juga memiliki 16-bit langsung atau high 16-bit versi. • AND: and, andi, andhi 24 Jurnal Komputasi, Volume 11 No: 2 Desember 2012 ISSN: 1412-9434 • OR: or, ori, orhi • Exclusive-OR: xor, xori • Complement: not • NOR: nor, nori • Exclusive-NOR: xnor, xnori 6.3 • Berpindah antar general-purpose register: mv • Memindahkan immediate ke high 16 bits register: mvhi • Tulis dan baca control dan status register: rcsr, wcsr Comparison Set instruksi memiliki instruksi comparison dasar dengan register-to-register dan register-to-16-bit- 6.6 Program Flow Control immediate dan signed dan unsigned comparison. Instruksi program ow control meliputi branches, Instruksi akan kembali 1 jika bernilai true dan 0 function dan exception calls, dan return. ketika false. • Equal: cmpe, cmpei • Not equal: cmpne, cmpnei • Greater: cmpg, cmpgi, cmpgu, cmpgui • Greater or equal: cmpge, cmpgei, cmpgeu, cmpgeui 6.4 Shift Set instruksi berguna untuk menggeser ke kiri dan kekanan suatu data yang terdapat dalam general-purpose registers. Jumlah dari bit yang akan di geser akan di bawa langsung menuju register atau 5-bit immediate. • Left shift: sl, sli • Right shift: sr, sri, sru, srui 6.5 6.5 Data Transfer • Unconditional branch: b, bi • Branch if equal: be • Branch if not equal: bne • Branch if greater: bg, bgu • Branch if greater or equal: bge, bgeu • Function call and return: call, calli, ret • System call: scall • Return from exception: eret • Software breakpoint and return: bret break, Data transfer meliputi instruksi yang dapat memindahkan data byte, half-word, dan ukuran kata antara memory dan register. Alamat memory merupakan hasil dari penjumlahan general- 7 Penutup purpose register dan signed 16-bit immediate, sebagai contoh (r2+32). LatticeMico32 ini bersifat open source yang • Load register from memory: lb, lbu, lh, lhu, memungkinkan penggunanya mengubah arsitektur dari Mico32 ini sesuai dengan device yang lw akan digunakan, dengan tambahan WISHBONE • Store register to memory: sb, sh, sw Ter- interface processor ini dapat ditambahkan dendapat juga instruksi untuk memindahkan gan perangkat memori luar ataupun peripheral data dari satu register ke yang lainnya, tambahan. LatticeMico32 memiliki dua register, termasuk general-purpose dan kontrol dan yaitu general-purpose register dan control and status register. status register. 25 Jurnal Komputasi, Volume 11 No: 2 Desember 2012 ISSN: 1412-9434 Daftar Pustaka [3] Anonymous, LatticeMico32. http://en.wikipedia.org/wiki/LatticeMico32, [1] Morris K., Soft Core War LatticeMico32 20012. Opens the Field, FPGA and Structured ASIC, September 26, 2006. [2] Minev, Petar B; Kukenska, Valentina S; [4] Anonymous, LatticeMico32 Implementation Of Soft-Core Processors In Processor Reference Manual. FPGAs, International Scientic Conference, http://milkymist.org/socdoc/lm32_archman.pdf, UNITECH, Gabrovo, November 2007 2009 26