4 BAB II TEORI DASAR SISTEM C

advertisement

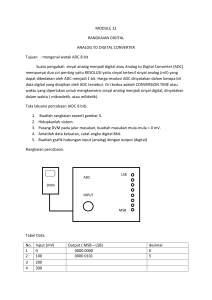

BAB II TEORI DASAR SISTEM C-V METER PENGUKUR KARAKTERISTIK KAPASITANSI-TEGANGAN 2.1. C-V Meter Karakteristik kapasitansi-tegangan (C-V characteristic) biasa digunakan untuk mengetahui karakteristik suatu divais semikonduktor 1-3) . Untuk keperluan tersebut diperlukan instrumen ukur berupa suatu sistem C-V meter. Sistem C-V meter secara umum digambarkan seperti pada Gambar 2.1. a) pengukur kapasitansi, Sistem terdiri atas: b) pengkonversi besaran analog ke digital (analog to digital conveter), c) Mikrokontroler / SoC (System on Chip) , d) tampilan komputer, e) sumber tegangan yang dapat diatur nilainya (programmable voltage source), f) sumber tegangan step, g) divais yang akan diukur karakteristiknya (fixture). Gambar 2.1 Diagram blok sistem C-V meter pengukur karakteristik kapasitansi-tegangan 4 Besarnya tegangan keluaran voltage source dan tegangan step yang diberikan ke divais (fixture) yang akan dikarakterisasi diatur oleh SoC. Perubahan tegangan akan menyebabkan aliran muatan pada fixture. Perubahan muatan ini dibaca oleh pengukur kapasitansi dan diubah menjadi nilai tegangan analog. ADC (analog to digital converter) mengubah nilai tegangan analog menjadi data digital sehingga dapat diproses oleh SoC. Data digital hasil pengukuran kapasitansi ini selanjutnya diolah oleh SoC dan dikirimkan ke komputer untuk ditampilkan dan diolah lebih lanjut. 2.2. Metode balikan muatan (feedback charge method) Salah satu pengukuran kapasitansi metode kuasi-statik yang telah banyak digunakan untuk aplikasi komersil adalah metode balikan muatan (feedback charge method) 1,4) . Rangkaian pada gambar 2.2 merupakan contoh rangkaian yang menggunakan metode balikan muatan. Rangkaian ini merupakan integrator yang berfungsi untuk megumpulkan semua muatan yang mengalir pada CF. Kapasitor CX sebagai C masukan dihubungkan langsung ke op-amp dan sumber tegangan untuk mengurangi noise. Metode ini disebut metode balikan muatan 4,7) yang menggunakan tegangan masukan step (∆V) terhadap ground semu pada opamp. Metode ini mempunyai impedansi yang tinggi yaitu masukan impedansi op-amp. Gambar 2.2 Pengukur Kapasitansi menggunakan metode balikan muatan Nilai kapasitansi ditentukan dengan mengukur transfer muatan sebagai respon dari kenaikan tegangan masukan (∆V). Tegangan ∆V jatuh semua pada CX 5 karena titik A berada pada ground semu. Muatan pada kapasitor umpan balik CF dikosongkan dengan menutup saklar S. Ketika pengukuran dimulai, saklar S dibuka dan ∆V menyebabkan muatan ∆Q terbentuk pada kapasitor CX dan secara otomatis op-amp akan membentuk ∆Q yang sama pada kapasitor CF karena keduanya terhubung seri., dan menghasilkan tegangan keluaran ∆Vo seperti pada persamaan 2.1. ΔV0 = − ΔQ CF (2.1) Karena ∆Q = CX ∆V, dapat diperoleh tegangan keluaran (∆Vo) yang proporsional terhadap kapasitansi CX. ΔV0 = − CX ΔV CF (2.2) DUT direferensikan terhadap masukan virtual ground dari penguat balikan muatan, sehingga tegangan step akan muncul seluruhnya pada DUT. Hal ini memberikan pengontrolan yang lebih ketat pada tegangan yang diberikan ke Cx. Penguatan yang lebih besar dapat mengurangi kebutuhan rangkaian pembaca Vout dan memberikan hasil yang lebih stabil dan rendah gangguan (noise). Penguatan dapat digunakan untuk pengukuran CX > CF dengan memilih rasio kapasitansi CF /CX yang sesuai. Metode balikan muatan cocok digunakan karena mempunyai kekebalan noise yang tinggi akibat impedansi masukan op-amp yang sangat tinggi. Pengukuran berdasarkan tegangan yang bisa diatur relatif mempermudah pembuatan kurva karakteristik C-V. Dengan mengubah ∆V dalam suatu daerah tegangan tertentu, dapat diperoleh.sebuah kurva CLF terhadap V. 1) Rangkaian balikan muatan tidak terpengaruh oleh frekuensi sehingga mempunyai daerah operasi yang lebar, ini digambarkan oleh gambar 2.3 4,7). Rasio penguatan sinyal terhadap noise untuk rangkaian tidak menurun ketika waktu tunda (delay) panjang digunakan. 6 Gambar 2.3 2.3. Gambar penguatan terhadap frekuensi untuk rangkaian metode balikan muatan SoC (System on a Chip) SoC / komputer mikro adalah suatu sistem yang terdiri atas mikroprosesor, memori, masukan/keluaran dan jalur bus data dalam satu kemasan (single chip) 8) . Pada sistem C-V meter, SoC berfungsi mengatur keluaran sumber tegangan (voltage source), mengatur nilai tegangan step, mengatur kerja ADC, mengolah data hasil pengukuran, dan mengirimkan hasil pengukuran ke PC. Saat ini terdapat banyak jenis SoC dengan beragam fasilitas serta keunggulan dan kelemahannya masing-masing. Salah satu SoC yang banyak diproduksi dan digunakan untuk eksperimen dan penelitian adalah SoC dari keluarga MCS-51. 2.4. ADC (Analog to Digital Converter) ADC (analog to digital converter) berfungsi untuk menghasilkan data digital yang merepresentasikan nilai yang proporsional dengan besaran analog yang berupa tegangan atau arus 9) . Secara umum dilihat dari kemampuannya ada tiga tipe ADC 8) : 1. Tipe integrating atau yang dikenal dengan dual-slope conversion. Walaupun lambat, tipe ini keakuratannya sangat baik dan murah. ADC jenis ini banyak digunakan pada voltmeter. 2. Tipe flash converter, ADC ini mempunyai respon paling cepat namun harganya sangat mahal dan resolusinya terbatas. 7 3. Tipe succesive-approximation, jenis ADC ini paling banyak digunakan karena kecepatan, akurasi dan variasi harganya. Nilai kode digital yang dihasilkan dapat diperoleh dengan menggunakan persamaan 2.3. 2n KodeDigital = Vin VRef (2.3) Di mana n menunjukkan resolusi ADC yang ditunjukkan dengan jumlah bit, Vin adalah tegangan masukan ADC dan VRef merupakan tegangan referensi yang menjadi nilai skala penuh ADC. Dari persamaan 2.3, satu LSB adalah sama dengan VRef / 2n. Untuk akurasi yang lebih baik dapat diperoleh dengan menggunakan resolusi yang lebih tinggi (n yang lebih tinggi), atau menggunakan tegangan referensi yang lebih rendah. Masalah untuk resolusi ADC yang lebih tinggi adalah pada harganya, dan juga semakin kecil LSB berarti akan semakin sulit untuk mengukur sinyal karena sinyal yang diukur biasanya tenggelam dalam noise (gangguan). Penggunaan tegangan referensi yang kecil akan mengakibatkan berkurangnya masukan dynamic range. Terdapat beberapa kesalahan (error) yang sering muncul pada penggunaan ADC, yaitu kesalahan kuantisasi (Quantization Error), kesalahan offset (Offset Error), kesalahan skala penuh (Full Scale Error) dan kesalahan penguatan (Gain Error). 10) 2.4.1 Kesalahan Kuantisasi (Quantization Error) Gambar 2.4 merupakan contoh kasus untuk ADC 3 bit. Ketika masukan ADC sama dengan nol, kode keluaran adalah nol (000). Ketika tegangan masukan membesar mendekati VREF/8, kesalahan juga membesar karena masukannya tidak lagi tegangan nol, tapi keluaran tetap nol karena daerah tegangan masukan tersebut diwakili oleh satu kode keluaran, yaitu nol (000). Ketika masukan mencapai VREF/8, kode keluaran berubah dari 000 menjadi 001 yaitu ketika kode keluaran tepat mewakili tegangan masukan dan kesalahannya menjadi 0. Ketika tegangan masukan membesar melebihi VREF/8, kesalahan membesar lagi hingga mencapai VREF/4, di mana kesalahannya berubah kembali menjadi 0. Proses ini berlanjut sepanjang daerah masukan dan kesalahan berbentuk gelombang gigi 8 gergaji. Kesalahan maksimumnya adalah 1 LSB. Daerah 0-1 LSB ini dikenal dengan “ketidakpastian kantisasi”. 10) Kesalahan kuantisasi merupakan ketidakpastian kantisasi maksimum. Gambar 2.4 Kesalahan kuantisasi (Quantization Error) 9 Kesalahan kuantisasi 1 LSB bisa disebut ± ½ LSB jika diberikan offset masukan sebesar ½ LSB seperti diilustrasikan pada gambar 2.5. Gambar 2.5 Kesalahan kuantisasi ± ½ LSB 10 2.4.2 Kesalahan Offset (Offset Error) Pada ADC ideal, tegangan masukan ½ dari VREF/2n akan menyebabkan perubahan kode keluaran dari nilai nol ke nilai satu. Setiap deviasi dari nilai ini disebut dengan kesalahan ofset skala nol (Zero Scale Offset Error), atau kesalahan offset (offset error) 10) . Kesalahan ini bisa bernilai positif atau negatif ketika titik transisi pertama lebih tinggi atau lebih rendah dari nilai ideal. Kesalahan offset adalah konstan dan bisa dengan mudah dikalibrasi. Kesalahan offset dapat diekspresikan dalam bentuk persen tegangan skala penuh, Volt, atau dalam LSB.ADC) Gambar 2.6 mengilustrasikan kesalahan offset untuk ADC 3 bit, di mana titik perubahan kode keluaran dari nilai nol ke satu bergeser lebih besar dari idealnya. Gambar 2.6 Kesalahan offset (Offset Error) 11 2.4.3 Kesalahan Skala Penuh (Full Scale Error) Pada ADC ideal, transisi kode keluaran ke nilai skala penuh terjadi ketika tegangan masukan seperti pada persamaan 2.4.ADC) 2n − 1,5 Vin = xVRef 2n (2.4) di mana Vref adalah tegangan referensi ADC dan n merupakan resolusi ADC. Pada ADC yang sebenarnya tegangan masukan skala penuh yang menyebabkan perubahan kode keluaran ini dapat berbeda dari kondisi idealnya. Kesalahan skala penuh adalah kesalahan pada titik transisi keluaran skala penuh. Salah satu sumber kesalahannya bisa akibat dari tegangan offset dan sisanya karena kesalahan pada kemiringan atau fungsi transfernya).10) Kesalahan skala penuh bisa diekspresikan dalam LSB, Volt atau persen dari nilai ideal tegangan masukan skala penuh. Gambar 2.7 mengilustrasikan kesalahan skala penuh untuk ADC 3 bit, di mana titik perubahan kode keluaran menjadi nilai skala penuh bergeser lebih rendah dari idealnya. Gambar 2.7 Kesalahan Skala Penuh (Full Scale Error) 12 2.4.4 Kesalahan Penguatan (Gain error) Kesalahan penguatan (Gain Error), atau kesalahan penguatan skala penuh (Full Scale Gain Error), merupakan deviasi dari kurva kemiringan ideal dari sebuah fungsi transfer ideal ADC. Ini adalah sama dengan kesalahan skala penuh dengan kesalahan offset-nya dikurangi. Gambar 2.6 mengilustrasikan kesalahan penguatan. Pada gambar 2.8 jika kita geser kurva transfer ADC aktual sedemikian rupa sehingga kesalahan skala nol menjadi nol, perbedaan antara transisi skala penuh kurva aktual dan ideal adalah kesalahan penguatan (gain error)10). Kesalahan penguatan diekspresikan dalam LSB atau persen dari tegangan skala penuh ideal. Gambar 2.8 Kesalahan Penguatan (Gain Error) 13 2.5. Prinsip Kerja DAC (Digital to Analog Converter) DAC (digital to analog converter) berfungsi mengubah nilai data digital menjadi besaran analog berupa tegangan atau arus 9) . Gambar 2.9 menunjukkan rangkaian dasar DAC 4 bit yang terdiri dari rangkaian penguat jumlah dengan 4 buah saklar yang mewakili masukan kode digital. Gambar 2.9 Rangkaian DAC 4 bit Resistor R1, R2, R3 dan R4 dipilih sedemikian rupa sehingga nilai R1=8xR4, R2 = 4xR4, R3 = 2xR4 dan nilai R dapat dipilih sesuai dengan nilai keluaran maksimum yang diinginkan. Nilai tegangan keluaran DAC sebanding nilai data biner yang diberikan. Saklar SW1 merupakan LSB dan SW3 merupakan MSB dengan kondisi saklar pada posisi tertutup menyatakan data biner bernilai 1. Untuk nilai R4 = ½ R fungsi transfer untuk DAC 4 bit pada gambar 2.9 diberikan oleh persamaan 2.5 yang merupakan persamaan umum untuk DAC, di mana Vo adalah tegangan analog keluaran, VRef merupakan tegangan referensi dan kode digital merupakan kombinasi nilai masukan digital yang diwakili oleh saklar SW1, SW2, SW3 dan SW4. Vo = VRef 2n KodeDigital (2.5) 14 2.6. Multiplekser Analog Multiplekser analog merupakan deretan atau kombinasi saklar analog yang dapat dikendalikan secara digital. Gambar 2.10 menunjukkan salah satu contoh multiplekser analog 3 bit. Salah satu dari 8 buah masukan analog akan dipilih dengan mengatur 3 bit masukan pengaturan alamat. Salah satu jenis multiplekser yang banyak digunakan adalah IC CMOS 4051. Masukan Analog X0 X1 X2 X3 X4 X5 X6 X7 X A B Keluaran C Pengaturan Alamat Gambar 2.10 Multiplekser 3 bit 15 2.7. Penguat Penjumlah Penguat penjumlah terdiri dari op-amp dengan dua atau lebih masukan dihubungkan menggunakan penguatan inverting seperti ditunjukkan pada gambar 2.11. Gambar 2.11 Rangkaian penguat penjumlah Keluaran dari penguat penjumlah merupakan penjumlahan dari tegangan masukan dikalikan dengan penguatan masing-masing masukan yang ditentukan dengan rasio nilai R terhadap R1, R2 dan R3 yaitu seperti pada persamaan 2.3. 11) R R ⎛ R ⎞ Vo = − ⎜ V 1 + V2+ V 3⎟ R2 R3 ⎠ ⎝ R1 2.3 16 2.8. Rangkaian Nilai Mutlak Rangkaian nilai mutlak merupakan penguat penyearah tegangan yang menghasilkan keluaran bernilai positif untuk setiap masukannya baik itu masukan positif atau pun negatif. Salah satu bentuk rangkaian penguat nilai mutlak penguatan satu ditunjukkan pada gambar 2.12. 12) Gambar 2.12 (a) Rangkaian nilai mutlak (b) Rangkaian ekivalen untuk Vi > 0 (c) Rangkaian ekivalen untuk Vi < 0 17 Pada sinyal masukan positif dioda D1 terbuka, D2 terhubung singkat opamp A2 akan berfungsi sebagai penguat dengan penguatan 1x seperti diilustrasikan pada gambar 2.10 (b) sehingga sinyal keluaran akan sama dengan masukan. Pada sinyal masukan negatif, dioda D1 terhubung, D2 terbuka dan opamp A2 akan berfungsi sebagai penguat inverting dengan penguatan -1x digambarkan oleh gambar 2.10 (c). R3 berfungsi sebagai kompensasi masukan agar masukan op-amp A2 melihat kedua masukan berimbang. Keluaran dari rangkaian nilai mutlak pada gambar 2.10 (a) adalah nilai mutlak dari tegangan masukan seperti pada persamaan 2.4 Vo = Vi 2.9. 2.4 Pengendali tegangan tinggi Pengendali tegangan tinggi yang dibahas pada tesis ini adalah pengendalian tegangan yang lebih tinggi dari tegangan yang digunakan pada sistem kontrol. Tegangan tinggi akan dikendalikan oleh tegangan yang jauh lebih rendah dengan resolusi yang berbeda. Contoh rangkaian pengendali tegangan tinggi ditunjukkan pada gambar 2.13. Pada penerapannya, tegangan tinggi yang dikendalikan dapat mencapai 220 V dengan penggunaan komponen yang sesuai. 18 Gambar 2.13 Rangkaian pengendali tegangan tinggi Rangkaian ini pada dasarnya merupakan sebuah penguat dengan sistem balikan negatif menggunakan rangkaian op-amp gabungan. Rangkaian op-amp gabungan dibentuk dari U4, Q1, Q2, dan bermacam-macam resistor dan kapasitor untuk pemberian bias dan kompensasi frekuensi. Balikan diberikan oleh RO3 dan CO1. Masukan ke penguat inverting dibentuk oleh RO0 dari sumber (V In). Penguatan rangkaian (Kv) diberikan oleh persamaan 2.5. Kv = RO3 RO0 (2.5) 19 2.10. Pembatas arus Untuk membatasi arus keluaran dari suatu sumber tegangan dapat digunakan rangkaian pembatas arus. Salah satu rangkaian pembatas arus sederhana adalah dengan menggunakan transistor. Contoh rangkaian pembatas arus ditunjukkan oleh gambar 2.14, rangkaian tersebut merupakan rangkaian pengendali tegangan tinggi yang dilengkapi dengan pembatas arus. Arus positif maksimum yang dapat dikeluarkan dibatasi oleh transistor Q3 dan RO7 dan arus negatif oleh Q4 dan RO8. Gambar 2.14 Rangkaian pengendali pembatas arus tegangan tinggi dengan 20 Arus maksimum rangkaian dapat diatur dengan menggunakan persamaan 2.6 dan 2.7. I + maks = VBE Q3 RO7 (2.6) I − maks = VBE Q4 RO8 (2.7) 2.11. Kapasitansi Pada Dioda Gambar 2.15 (a) menunjukkan bagaimana lapisan deplesi dari sebuah dioda pn terbentuk oleh muatan tetap (fixed charges) ion donor dan akseptor yang terkonsentrasi pada titik pertemuan (junction) bahan p dan n. Lapisan ini mempunyai karakteristik sebuah kapasitor yang disebut kapasitansi deplesi. Kapasitansi lapisan deplesi, bergantung pada tegangan bias yang diberikan. Karena lapisan deplesi bergantung pada konsentrasi ketidakmurnian dari substrat, konsentrasi ketidakmurnian dan tegangan built-in dapat dihitung dengan mengukur karakteristik C-V dari struktur dioda sambungan pn 13). Gambar 2.15 Kapasitansi pada Dioda sambungan pn (a) Lapisan Deplesi (b) Panjar Mundur (c) Panjar Maju 21 Ketika tegangan luar diberikan pada dioda baik dalam arah panjar maju ataupun arah panjar mundur, seperti ditunjukkan oleh bagian (b) dan (c) pada gambar 2.15, akan mempengaruhi lebar lapisan deplesi. Tegangan yang cukup untuk “melawan” tegangan penghalang dapat menyebabkan mengalirnya arus. Lebar daerah deplesi dapat diatur dengan menjaga tegangan panjar pada tingkat yang tidak dapat mengalirkan arus. Salah satu jenis dioda yang khusus digunakan sebagai kapasitor adalah dioda varactor. Varactor merupakan dioda semikonduktor dengan sifat kapasitor yang bergantung tegangan, yaitu dioda sambungan pn yang memanfaatkan prinsip kebergantungan kapasitansi daerah lapisan deplesi pada dioda. Karena lapisan deplesi berlaku sebagai kapasitor, dioda varaktor akan membentuk kapasitor yang dapat diatur (variable capacitor). Dioda varactor banyak digunakan sebagai kapasitor penala (tuning capacitor) pada rangkaian osilator. Gambar 2.16 Kurva C-V dioda varactor tipe MV2105 14) 22 Gambar 2.17 Kurva C-V dioda 13) Kapasitansi dari varactor yang umum digunakan berkisar antara 2 sampai 50 pF untuk tegangan panjar sebesar 2 Volt. Gambar 2.16 dan 2.17 menunjukkan contoh kurva karakteristik dari dioda. 23